| Programn<br>rules: A s     |                          |         | ple      |

|----------------------------|--------------------------|---------|----------|

| Euclid's alg<br>Greatest C |                          |         |          |

| 15                         | 5                        | 6       |          |

| 9                          |                          | 6       | subtract |

| 3                          |                          | 6       | subtract |

| 6                          |                          | 3       | swap     |

| 3                          |                          | 3       | subtract |

| O                          | answer: (                | 3       | subtract |

| September 18, 2015         | http://csg.csail.mit.edu | u/6.175 | L05=     |

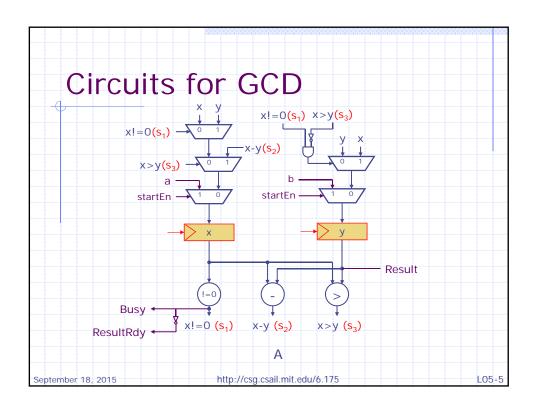

| Euclidean Algorithm               |                           |  |

|-----------------------------------|---------------------------|--|

| Reg#(Bit#(32)) x <- mkReg(0);     |                           |  |

| Reg#(Bit#(32)) y <- mkReg(0);     |                           |  |

| rule gcd;                         | A rule inside a module    |  |

| if (x >= y) begin                 | may execute anytime       |  |

| x <= x - y;                       |                           |  |

| end else if (x != 0) begin        | If $x$ is 0 then the rule |  |

| x <= y; y <= x;                   | has no effect             |  |

| endrule                           |                           |  |

| method Action start(Bit#(32) a, E | 3i+#(32) b);              |  |

| x <= a; y <= b;                   | endmethod                 |  |

| method Bit#(32) result; return y; | endmethod                 |  |

| method Bool resultRdy; return x   |                           |  |

|                                   | != 0; endmethod           |  |

```

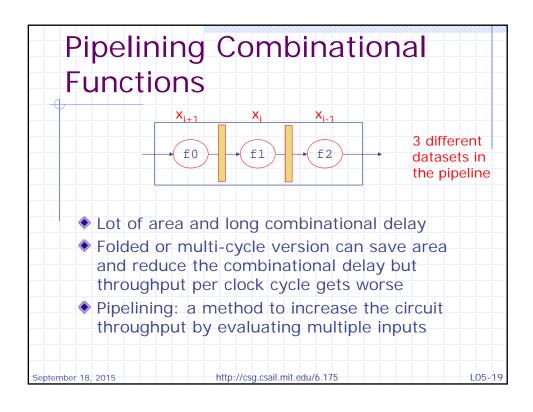

Combinational 32-bit multiply

function Bit#(64) mul32(Bit#(32) a, Bit#(32) b);

Bit#(32) tp = 0;

Bit#(32) prod = 0;

for (Integer i = 0; i < 32; i = i+1)

Combinational

begin

circuit uses 31

Bit#(32) m

= (a[i]==0)? 0 : b;

add32 circuits

Bit#(33) sum = add32(m, tp, 0);

prod[i:i] = sum[0];

= sum[32:1];

end

return {tp,prod};

endfunction

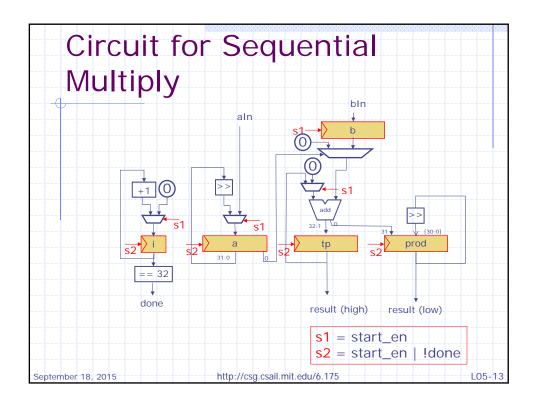

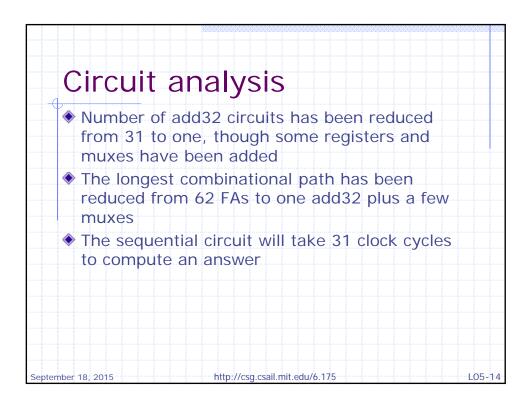

We can reuse the same add32 circuit if we store

the partial results in a register

September 18, 2015

http://csg.csail.mit.edu/6.175

L05-8

```

```

Multiply using registers

function Bit#(64) mul32(Bit#(32) a, Bit#(32) b);

Bit#(32) prod = 0;

Bit#(32) tp = 0;

for(Integer i = 0; i < 32; i = i+1)</pre>

begin

Bit#(32) m = (a[i]==0)? 0 : b;

Bit#(33) sum = add32(m, tp, 0);

prod[i:i] = sum[0];

Combinational

tp = sum[32:1];

version

end

return {tp,prod};

endfunction

Need registers to hold a, b, tp, prod and i

Update the registers every cycle until we are done

http://csg.csail.mit.edu/6.175

September 18, 2015

L05-9

```

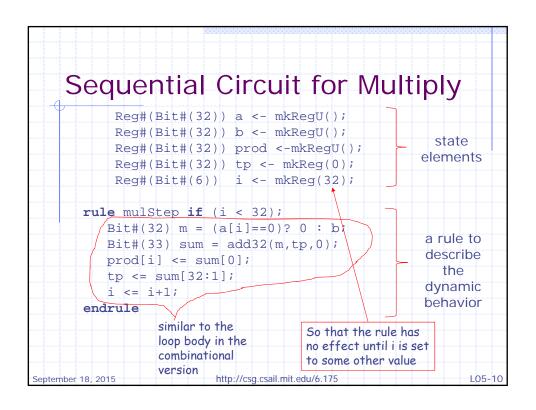

```

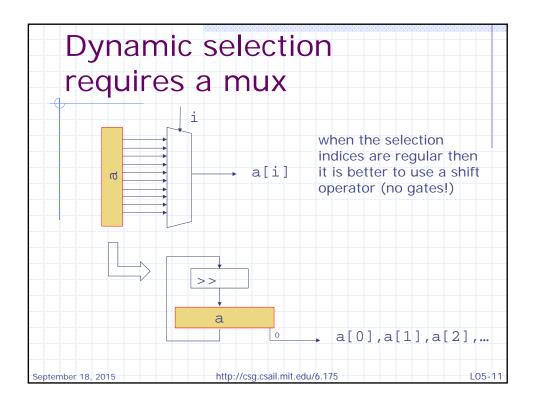

Replacing repeated

selections by shifts

Reg#(Bit#(32)) a <- mkRegU();</pre>

Reg#(Bit#(32)) b <- mkRegU();</pre>

Reg#(Bit#(32)) prod <-mkRegU();</pre>

Reg#(Bit#(32)) tp <- mkReg(0);</pre>

Reg#(Bit#(6)) i <- mkReg(32);</pre>

rule mulStep if (i < 32);</pre>

Bit#(32) m = (a[0]==0)? 0 : b;

a <= a >> 1;

Bit#(33) sum = add32(m, tp, 0);

prod <= {sum[0], prod[31:1]};</pre>

tp <= sum[32:1];

i <= i+1;

endrule

L05-12

September 18, 2015

http://csg.csail.mit.edu/6.175

```

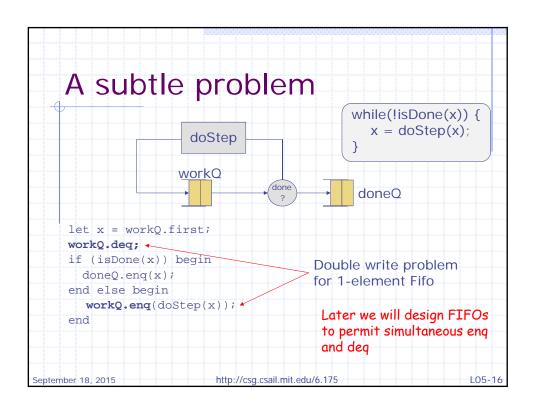

## Observations These programs are not very complex and yet it would have been tedious to express these programs in a state table or as a circuit directly BSV method calls are not available in Verilog/VHDL, and thus such programs sometimes require tedious programming Even the meaning of double-write errors is not standardized across tool implementations in Verilog September 18, 2015 http://csg.csail.mit.edu/6.175 L05-15

```

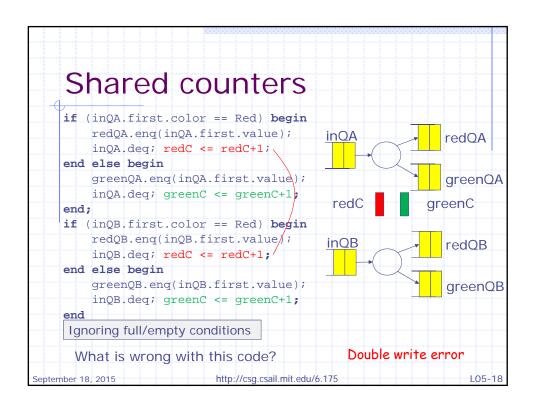

Illegal Actions — Double

Write

♦ x <= e1; x <= e2;

♦ x <= e1; if(p) x <= e2;

Parallel composition of two actions is illegal if it creates the possibility of a double-write error, that is, if its constituent (sub)actions invoke the same action method

September 18, 2015

http://csg.csail.mit.edu/6.175

L05-17

```