**Constructive Computer Architecture**

### Virtual Memory: From Address Translation to Demand Paging

Arvind

Computer Science & Artificial Intelligence Lab. Massachusetts Institute of Technology

L20-1

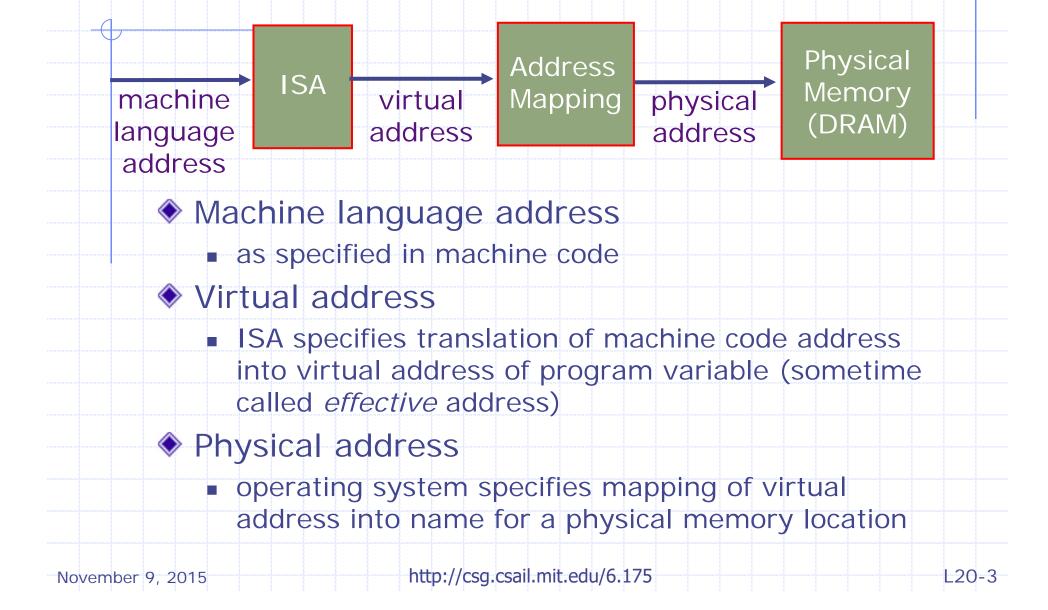

## Names for Memory Locations

## Paged Memory Systems

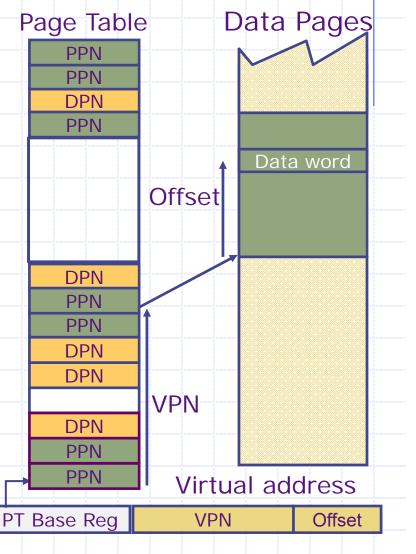

Processor generated address can be interpreted as a pair <page number, offset>

page number offset

A page table contains the physical address of the base of each page

$\mathbf{O}$

3

2

L20-4

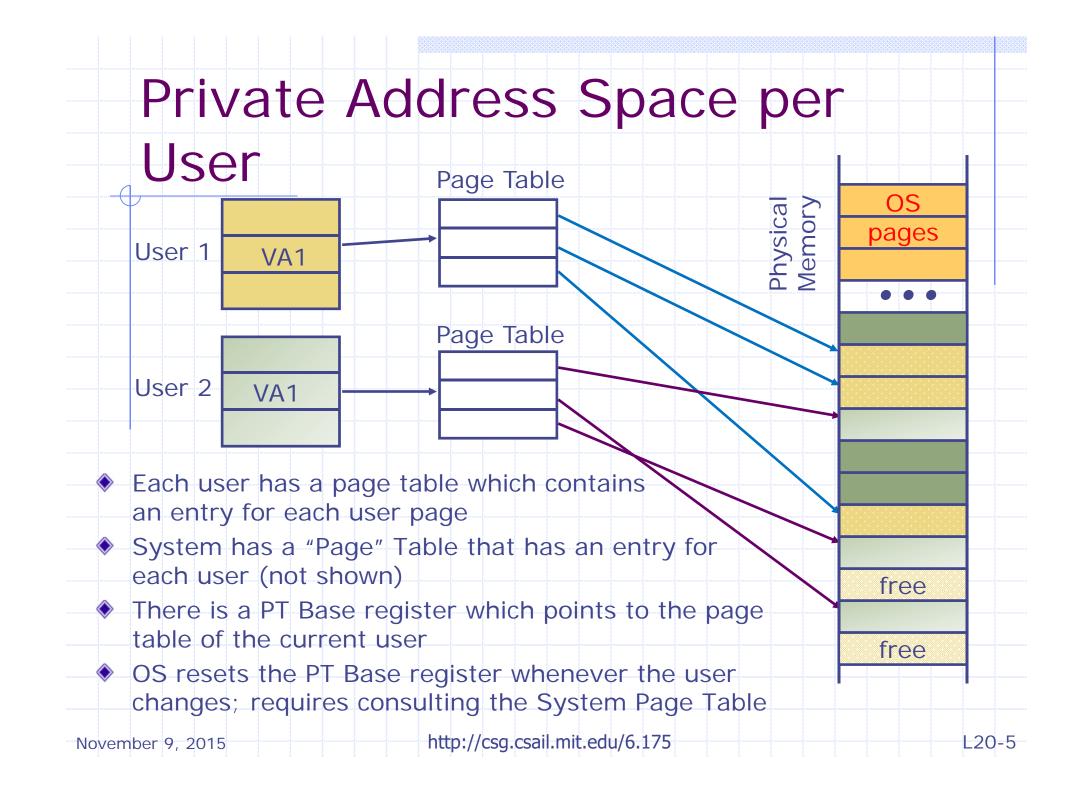

Address Space Page Table of User-1 of User-1

()

3

0

1

2

3

Page tables make it possible to store the pages of a program non-contiguously

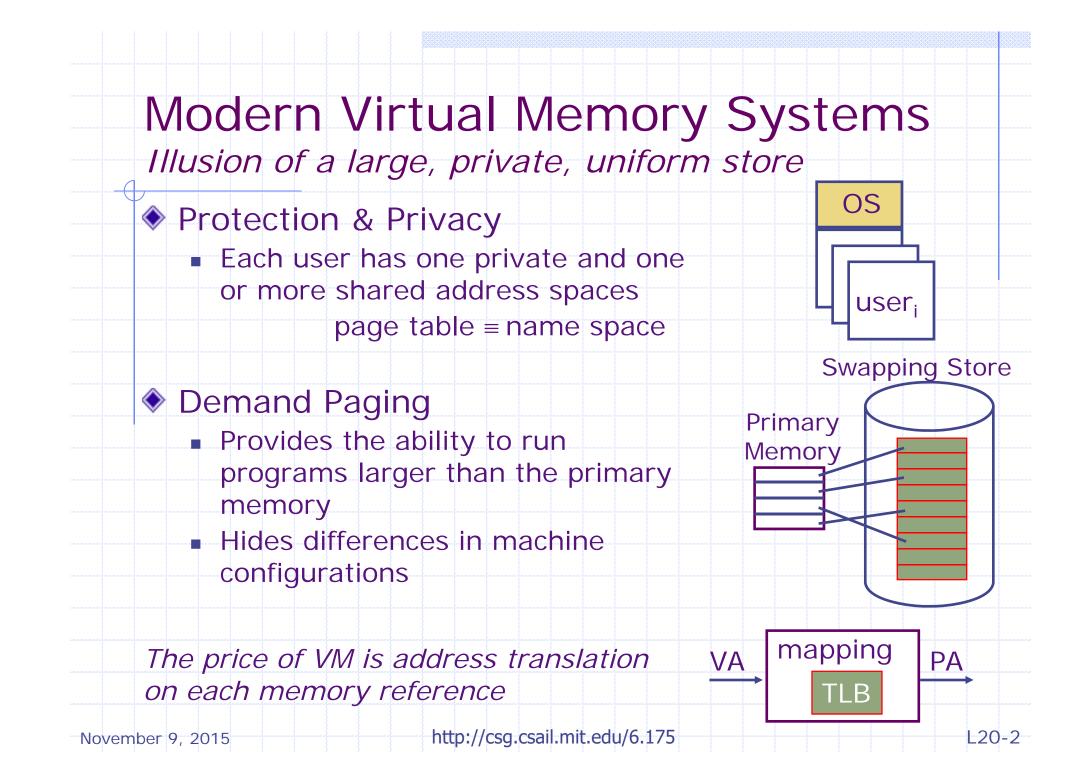

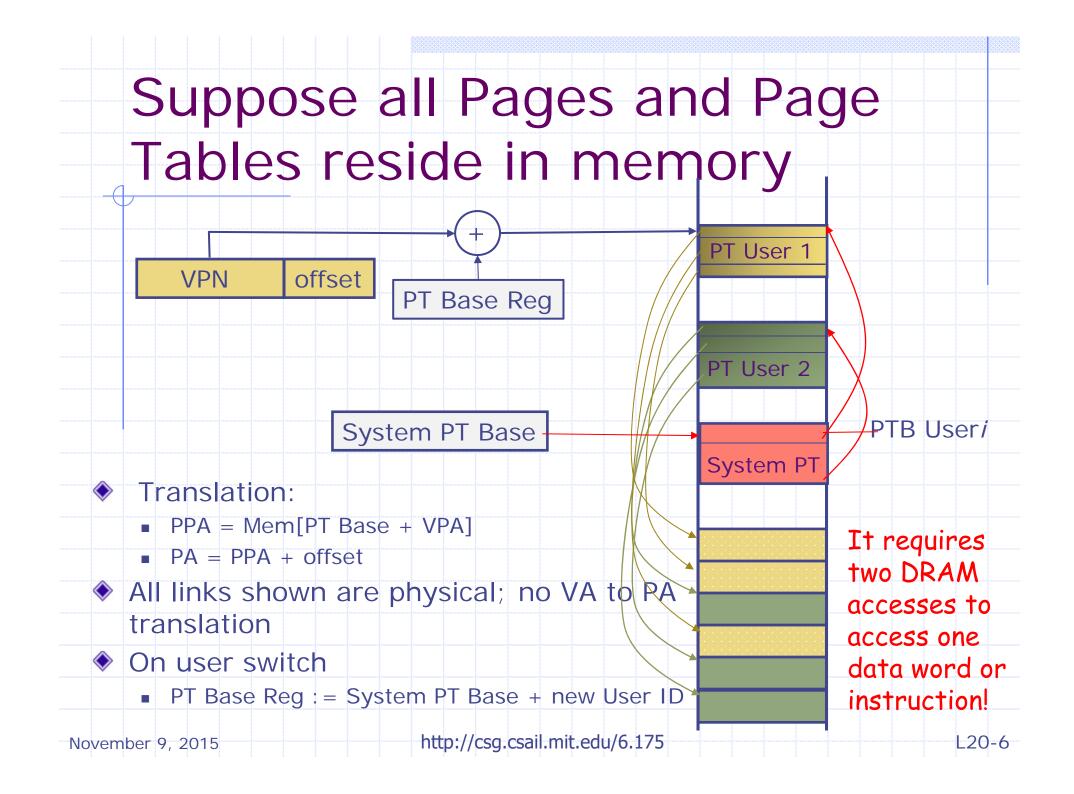

## VM Implementation Issues

- How to reduce memory access overhead

- ♦ What if all the pages can't fit in DRAM

- What if the user page table can't fit in DRAM

- What if the System page table can't fit in DRAM

A good VM design needs to be fast and space efficient

L20-7

# Page Table Entries and

Swap Space

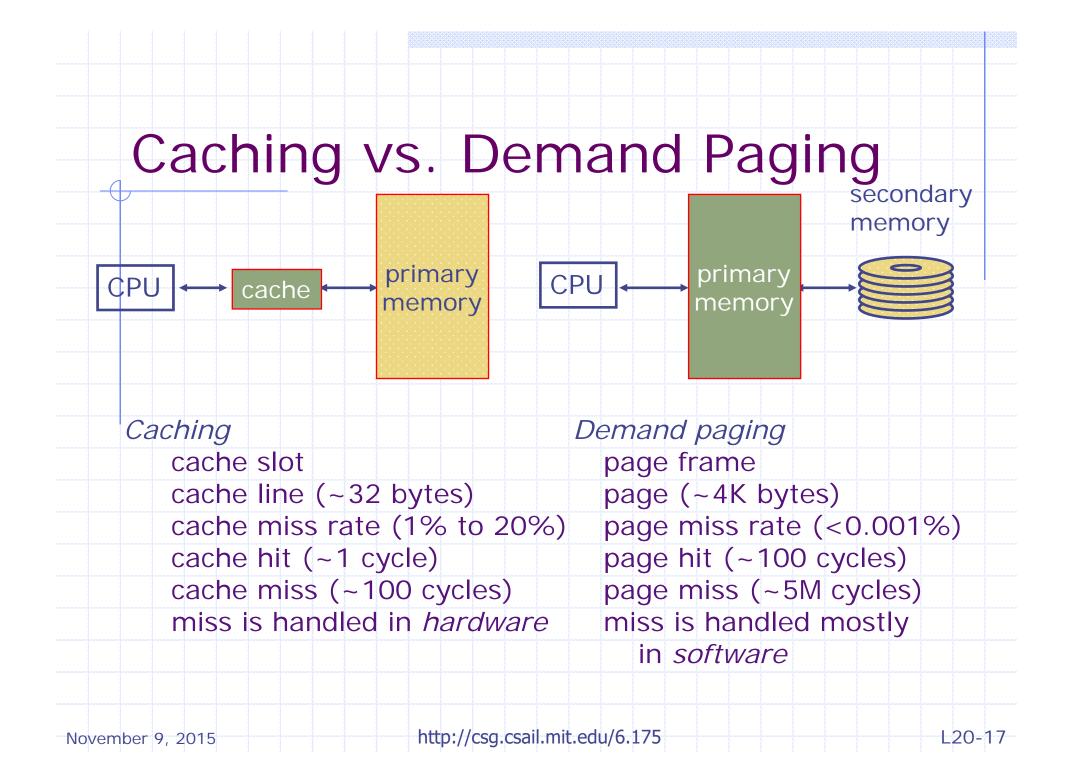

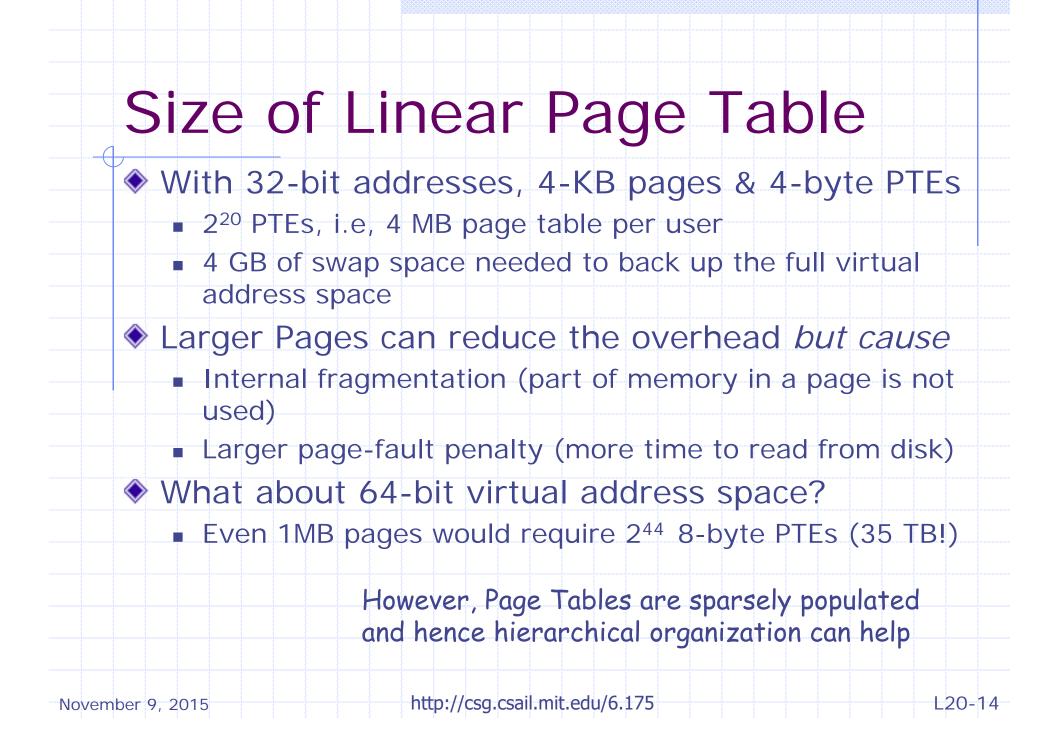

- DRAM has to be backed up by swap space on disk because all the pages of all the users cannot fit in DRAM

- Page Table Entry (PTE) contains:

- A bit to indicate if a page exists

- PPN (physical page number) for a memory-resident page

- DPN (disk page number) for a page on the disk

- Protection and usage bits

November 9, 2015

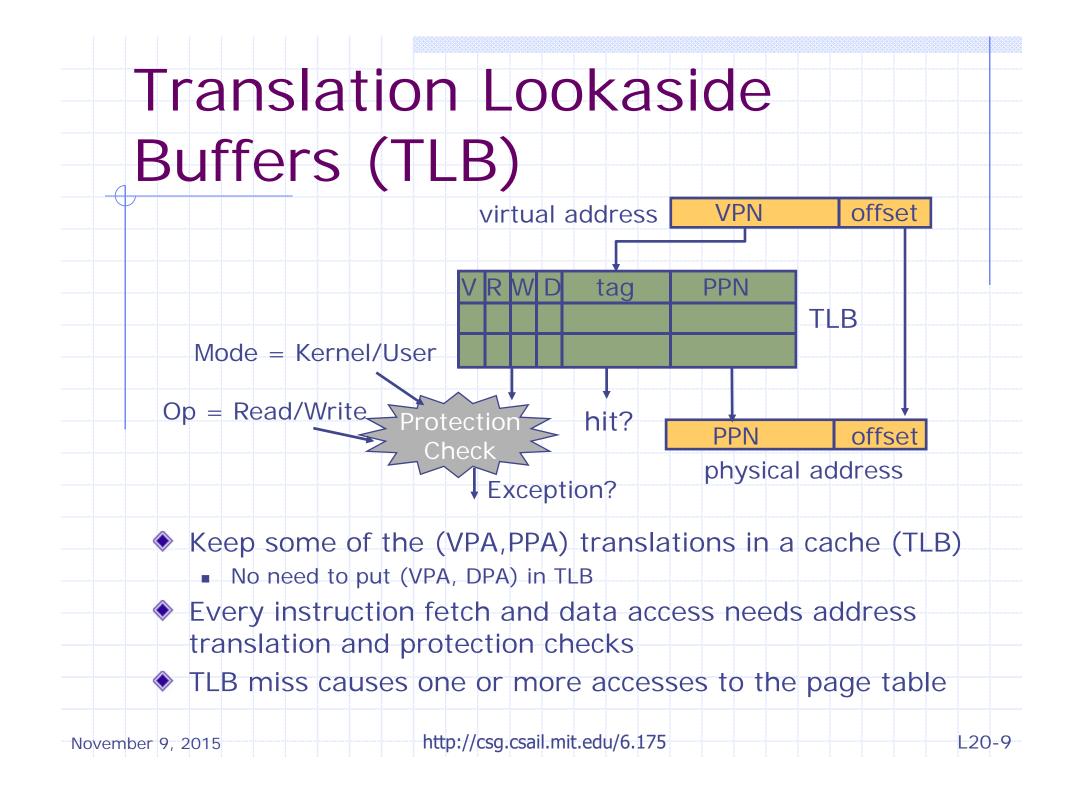

## **TLB Designs**

#### Typically 32-128 entries, usually fully associative

- Each entry maps a large page, hence less spatial locality across pages → more likely that two entries conflict

- Sometimes larger TLBs (256-512 entries) are 4-8 way set-associative

TLB Reach: Size of largest virtual address space that can be simultaneously mapped by TLB Example: 64 TLB entries, 4KB pages, one page per entry

TLB Reach = 64 entries \* 4 KB = 256 KB

Replacement policy? Random, FIFO, LRU, ...

Switching users is expensive because TLB has to be flushed

Store User IDs in TLB entries

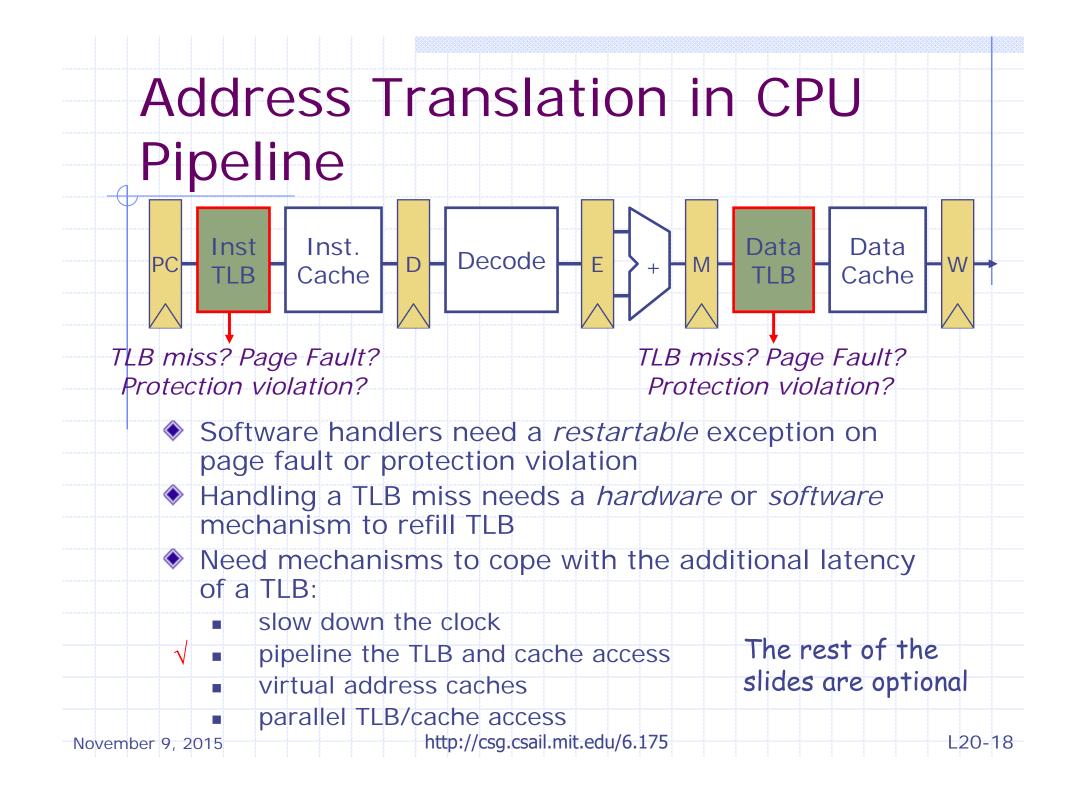

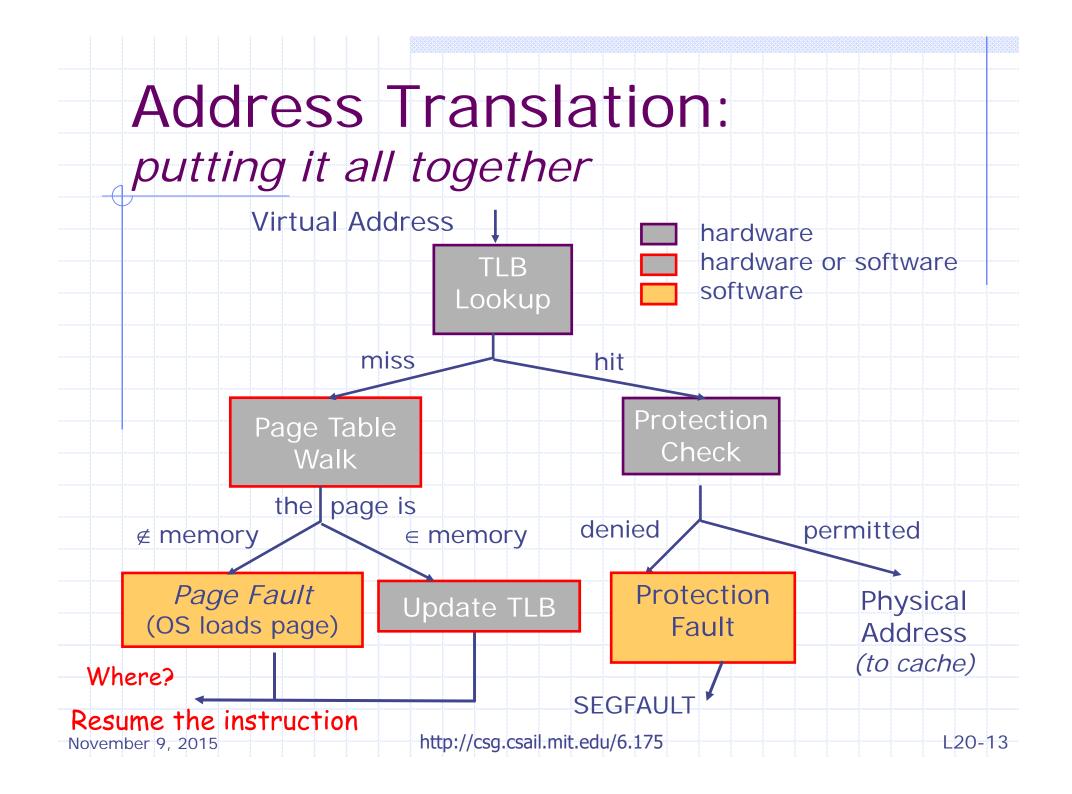

## Handling a TLB Miss

#### Software (MIPS, Alpha)

- TLB miss causes an exception and the operating system walks the page tables and reloads TLB

- A privileged "untranslated" addressing mode is used for PT walk

#### ♦ Hardware (SPARC v8, x86, PowerPC)

- A memory management unit (MMU) walks the page tables and reloads the TLB

- If a missing (data or PT) page is encountered during the TLB reloading, MMU gives up and signals a Page-Fault exception for the original instruction

## Handling a Page Fault

- When the referenced page is not in DRAM:

- The missing page is located (or created)

- It is brought in from disk, and page table is updated

- Another job may be run on the CPU while the first job waits for the requested page to be read from disk

- If no free pages are left, a page is swapped out approximate LRU replacement policy

Since it takes a long time (msecs) to transfer a page, page faults are handled completely in software (OS)

http://csg.csail.mit.edu/6.175 November 9, 2015

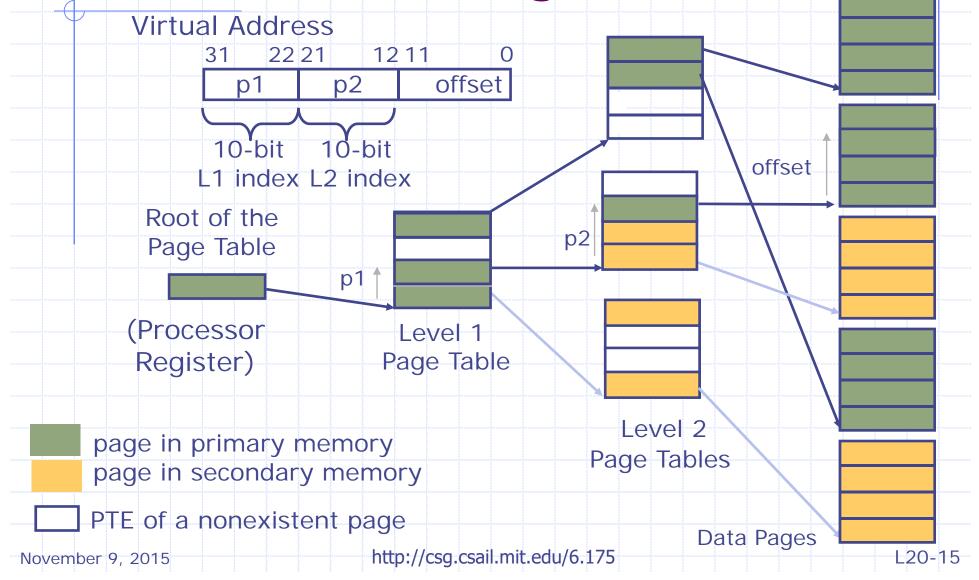

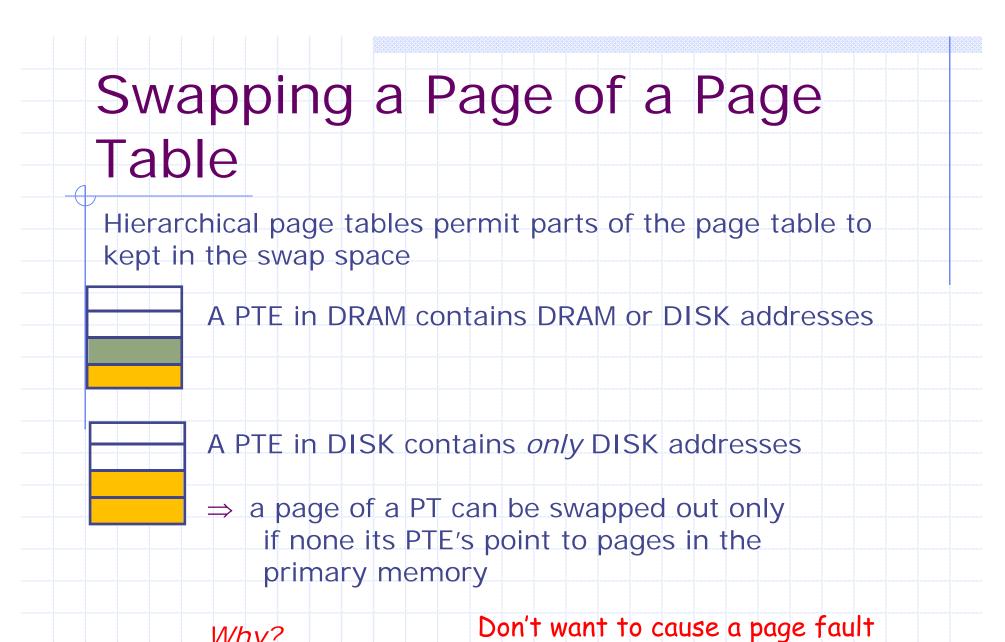

## **Hierarchical Page Table**

Why? Don't want to cause a page fault during translation when the data is in memory

November 9, 2015 http://csg.csail.mit.edu/6.175

L20-16