# BSV by Example

The next-generation language for electronic system design

Rishiyur S. Nikhil and Kathy R. Czeck

Copyright © 2010 Bluespec, Inc. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means – electronic, mechanical, photocopying, or otherwise – without the prior written permission of Bluespec, Inc.

Edition 1.0

ISBN: 978-1456418465

Bluespec is a registered trademark of Bluespec, Inc. The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

While every precaution has been taken in the preparation of this book, Bluespec, Inc. and authors assume no responsibility for errors or omissions, or for damages resulting from the use of the information contained herein.

Any questions may be directed to support@bluespec.com. Additional support resources are available at http://www.bluespec.com/support/.

The authors thank all our colleagues and friends at Bluespec, MIT and Sandburst who contributed to the creation of BSV, its tools, and to the expertise for their effective use. In this book, the authors are merely channeling this vast body of shared knowledge.

# Contents

|   | Tab  | le of Contents                                                    | 4  |

|---|------|-------------------------------------------------------------------|----|

| 1 | Intr | roduction                                                         | 13 |

|   | 1.1  | Design activities where BSV is used                               | 13 |

|   | 1.2  | Key ideas in BSV                                                  | 14 |

|   |      | 1.2.1 Behavior                                                    | 14 |

|   |      | 1.2.2 Structure                                                   | 15 |

|   | 1.3  | Why BSV? Can't we do all this with existing languages (like C++)? | 15 |

|   | 1.4  | About this book                                                   | 19 |

| 2 | Get  | tting started with BSV                                            | 21 |

|   | 2.1  | A simple example                                                  | 21 |

|   |      | 2.1.1 Comments                                                    | 22 |

|   |      | 2.1.2 Package                                                     | 22 |

|   |      | 2.1.3 (* synthesize *)                                            | 22 |

|   |      | 2.1.4 Module definition                                           | 22 |

|   |      | 2.1.5 Rule                                                        | 23 |

|   |      | 2.1.6 System tasks                                                | 23 |

|   | 2.2  | Building the design                                               | 24 |

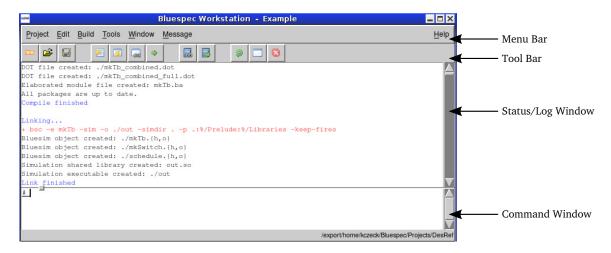

|   |      | 2.2.1 Bluespec Development Workstation (BDW)                      | 24 |

|   |      | 2.2.2 Components of a BSV design                                  | 24 |

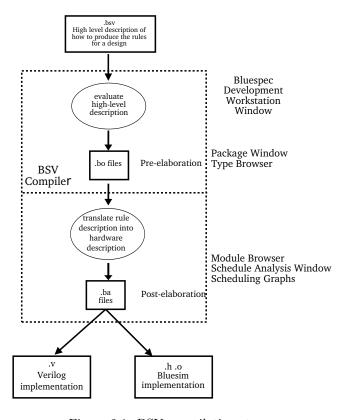

|   |      | 2.2.3 Overview of the BSV build process                           | 25 |

|   |      | 2.2.4 Create a project file                                       | 26 |

|   |      | 2.2.5 Compile                                                     | 27 |

|   | 2.3 | Multiple modules in a single package                  | 28 |

|---|-----|-------------------------------------------------------|----|

|   |     | 2.3.1 Interfaces                                      | 29 |

|   | 2.4 | Multiple packages in a single design                  | 31 |

| 3 | Dat | ca types                                              | 33 |

|   | 3.1 | Type                                                  | 33 |

|   | 3.2 | Uppercase and lowercase in type and value identifiers | 33 |

|   | 3.3 | Typeclasses and overloading                           | 34 |

|   | 3.4 | Pre-defined type classes                              | 35 |

|   | 3.5 | Data type conversion functions                        | 35 |

|   | 3.6 | Some common scalar types                              | 36 |

|   |     | 3.6.1 Bit#(n)                                         | 36 |

|   |     | 3.6.2 Bool                                            | 37 |

|   |     | 3.6.3 UInt#(n)                                        | 37 |

|   |     | 3.6.4 Int#(n)                                         | 37 |

|   | 3.7 | Using abstract types instead of Bit                   | 37 |

|   | 3.8 | Integers                                              | 40 |

|   | 3.9 | Strings                                               | 42 |

| 4 | Var | iables, assignments, and combinational circuits       | 43 |

|   | 4.1 | Variable declaration and initialization               | 43 |

|   |     | 4.1.1 Side-effect initialization                      | 44 |

|   |     | 4.1.2 Value initialization                            | 44 |

|   |     | 4.1.3 Value initialization from a Value method        | 45 |

|   |     | 4.1.4 Initializing sub-interface components           | 45 |

|   |     | 4.1.5 Additional examples                             | 46 |

|   | 4.2 | Combinational circuits                                | 47 |

|   |     | 4.2.1 Error - no type declaration                     | 50 |

|   |     | 4.2.2 Error - no initialization                       | 50 |

| <b>5</b> | Rul | es, registers, and fifos                           | <b>51</b> |  |  |  |  |

|----------|-----|----------------------------------------------------|-----------|--|--|--|--|

|          | 5.1 | Defining and updating a register                   | 51        |  |  |  |  |

|          |     | 5.1.1 Registers                                    | 52        |  |  |  |  |

|          |     | 5.1.2 Updating the register                        | 52        |  |  |  |  |

|          | 5.2 | Rules and their semantics: atomicity and orderings | 53        |  |  |  |  |

|          | 5.3 | Composition of rules                               | 54        |  |  |  |  |

|          |     | 5.3.1 Attribute descending_urgency                 | 56        |  |  |  |  |

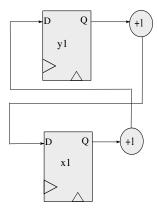

|          | 5.4 | Multiple registers in a rigid synchronous pipeline | 57        |  |  |  |  |

|          | 5.5 | Using register syntax shorthands                   |           |  |  |  |  |

|          | 5.6 | Using valid bits                                   | 60        |  |  |  |  |

|          | 5.7 | Multiple FIFOs in an elastic asynchronous pipeline | 61        |  |  |  |  |

| 6        | Mo  | dule hierarchy and interfaces                      | 65        |  |  |  |  |

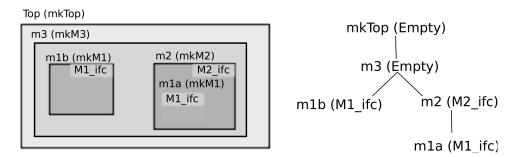

|          | 6.1 | Module hierarchies                                 | 65        |  |  |  |  |

|          |     | 6.1.1 Parameter                                    | 67        |  |  |  |  |

|          |     | 6.1.2 Scope of methods                             | 68        |  |  |  |  |

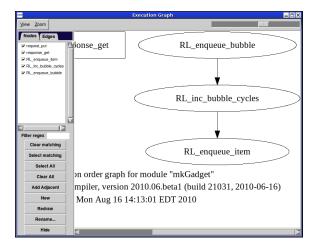

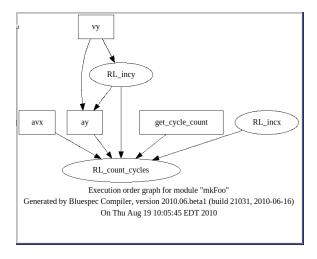

|          |     | 6.1.3 Analyzing a design                           | 69        |  |  |  |  |

|          | 6.2 | Implicit conditions of methods                     | 70        |  |  |  |  |

|          | 6.3 | ActionValue methods                                | 71        |  |  |  |  |

|          |     | 6.3.1 The let statement                            | 72        |  |  |  |  |

|          |     | 6.3.2 The <- operator                              | 72        |  |  |  |  |

|          |     | 6.3.3 Defining the ActionValue Method              | 72        |  |  |  |  |

|          | 6.4 | ActionValue method with type error                 | 73        |  |  |  |  |

|          | 6.5 | ActionValue method with error in rule condition    | 74        |  |  |  |  |

|          | 6.6 | Defining an Action function                        | 75        |  |  |  |  |

|          | 6.7 | Nested interfaces                                  | 76        |  |  |  |  |

|          | 6.8 | Standard connectivity interfaces                   | 81        |  |  |  |  |

| 7        | Sch | ${f eduling}$                                      | 85        |  |  |  |  |

|          | 7.1 | Scheduling error due to parallel composition       | 86        |  |  |  |  |

|          | 7.2 | Scheduling attributes                              | 87        |  |  |  |  |

|          |     | 7.2.1 Prioritization using descending_urgency      | 87        |  |  |  |  |

|    |      | 7.2.2 Descending urgency vs. execution order                   | 89         |

|----|------|----------------------------------------------------------------|------------|

|    |      | 7.2.3 mutually_exclusive                                       | 91         |

|    |      | 7.2.4 conflict_free                                            | 93         |

|    |      | 7.2.5 preempts                                                 | 94         |

|    |      | 7.2.6 fire_when_enabled, no_implicit_conditions                | 96         |

|    | 7.3  | always_ready, always_enabled                                   | 99         |

|    | 7.4  | -aggressive-conditions                                         | 100        |

|    | 7.5  | Separating an ActionValue method                               | 102        |

| 8  | RW   | ires and Wire types                                            | 107        |

|    | 8.1  | RWire                                                          | 107        |

|    |      | 8.1.1 Up-down counter with simultaneous up/down commands       | 108        |

|    |      | 8.1.2 Attributes (*fire_when_enabled, no_implicit_conditions*) | 111        |

|    |      | 8.1.3 Compiling the Example                                    | 112        |

|    |      | 8.1.4 RWire with pattern-matching                              | 113        |

|    | 8.2  | Wire                                                           | 114        |

|    | 8.3  | DWire                                                          | 115        |

|    | 8.4  | PulseWire                                                      | 116        |

|    | 8.5  | BypassWire                                                     | 119        |

|    | 8.6  | RWires and atomicity                                           | 120        |

| 9  | Poly | ymorphism                                                      | <b>123</b> |

|    | 9.1  | Polymorphic function                                           | 123        |

|    |      | 9.1.1 Common overloading provisos                              | 125        |

|    |      | 9.1.2 Size relationship provisos                               | 126        |

|    |      | 9.1.3 value<br>Of and SizeOf pseudo-functions                  | 126        |

|    | 9.2  | Simple polymorphic module with provisos                        | 127        |

| 10 | Adv  | ranced types and pattern-matching                              | 133        |

|    | 10.1 | User-defined types                                             | 133        |

|    |      | 10.1.1 Type synonyms                                           | 133        |

|    |      | 10.1.2 Enums                                                   | 134        |

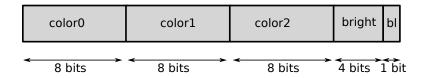

|    |      | 10.1.3 Structs                                                 | 136        |

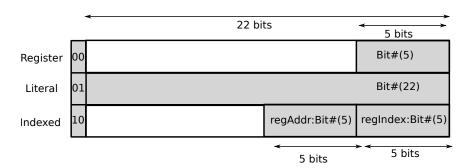

|           | 10.1.4 Tagged unions                                         | <br>137 |

|-----------|--------------------------------------------------------------|---------|

|           | 10.1.5 Maybe type                                            | <br>139 |

|           | 10.1.6 Case statements and pattern-matching on tagged unions | <br>141 |

|           | 10.2 Simple Processor Model                                  | <br>143 |

|           | 10.3 Structs of registers vs. register containing a struct   | <br>145 |

|           | 10.4 Tuples                                                  | <br>148 |

| 11        | Static elaboration - For-loops/while-loops                   | 151     |

|           | 11.1 Non-terminating for-loops and while-loops               | <br>151 |

|           | 11.2 Static and dynamic conditionals                         | <br>153 |

| <b>12</b> | Expressions                                                  | 157     |

|           | 12.1 "Don't care" expressions, 2-valued and 4-valued logic   | <br>158 |

|           | 12.2 Case expressions                                        | <br>160 |

|           | 12.3 Function calls                                          | <br>160 |

| <b>13</b> | Vectors                                                      | 163     |

|           | 13.1 Arrays and square-bracket notation                      | <br>164 |

|           | 13.2 Arrays vs. Vectors                                      | <br>165 |

|           | 13.3 bit-vectors and square bracket notation                 | <br>167 |

|           | 13.4 Whole register update                                   | <br>172 |

|           | 13.5 Vector of registers                                     | <br>174 |

|           | 13.6 Register containing a vector vs. a vector of registers  | <br>175 |

|           | 13.7 Vector of module interfaces                             | <br>176 |

|           | 13.8 Static and dynamic indexing of vectors                  | <br>177 |

| 14        | Finite State Machines (FSMs)                                 | 181     |

|           | 14.1 Building an FSM explicitly using rules                  | <br>181 |

|           | 14.2 One-hot FSM explicitly using rules                      | <br>183 |

|           | 14.3 StmtFSM                                                 | <br>185 |

|           | 14.3.1 A basic template                                      | <br>186 |

|           | 14.3.2 AutoFSM                                               | <br>187 |

|           | 14.3.3 StmtFSM example                                       | <br>188 |

| <b>15</b> | Imp  | porting existing RTL into a BSV design             | 195 |

|-----------|------|----------------------------------------------------|-----|

|           | 15.1 | Using an existing interface                        | 196 |

|           |      | 15.1.1 Module header definition                    | 197 |

|           |      | 15.1.2 Parameters                                  | 197 |

|           |      | 15.1.3 Clocks and Resets                           | 198 |

|           |      | 15.1.4 Methods                                     | 199 |

|           | 15.2 | Defining a new interface                           | 200 |

| A         | Sou  | rce Files                                          | 203 |

|           | A.1  | Getting started with BSV                           | 203 |

|           |      | A.1.1 A simple example                             | 203 |

|           |      | A.1.2 Testbench communicating with DUT             | 204 |

|           |      | A.1.3 Multiple packages in a single design         | 205 |

|           | A.2  | Data types                                         | 206 |

|           |      | A.2.1 Using abstract types instead of Bit          | 206 |

|           |      | A.2.2 Integers                                     | 208 |

|           |      | A.2.3 Strings                                      | 210 |

|           | A.3  | Variables, assignments, and combinational circuits | 210 |

|           |      | A.3.1 Variable declaration and initialization      | 211 |

|           |      | A.3.2 Combinational circuits                       | 212 |

|           | A.4  | Rules, registers, and FIFOs                        | 213 |

|           |      | A.4.1 Defining and updating a Register             | 213 |

|           |      | A.4.2 Composition of rules                         | 214 |

|           |      | A.4.3 Multiple registers in a rigid pipeline       | 214 |

|           |      | A.4.4 Using register syntax shorthand              | 216 |

|           |      | A.4.5 Using valid bits                             | 217 |

|           |      | A.4.6 Asynchronous pipeline using FIFOs            | 218 |

|           | A.5  | Module hierarchy and interfaces                    | 220 |

|           |      | A.5.1 Module hierarchies                           | 220 |

|           |      | A.5.2 Implicit conditions of methods               | 221 |

|           |      | A.5.3 ActionValue method                           | 222 |

|           |      | A.5.4 ActionValue method with type error           | 223 |

|     | A.5.5  | ActionValue method with error in rule condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 224 |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | A.5.6  | Defining an Action function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 225 |

|     | A.5.7  | Nested interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 226 |

|     | A.5.8  | Standard connectivity interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 228 |

| A.6 | Schedu | ıling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 230 |

|     | A.6.1  | Scheduling error due to parallel composition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 230 |

|     | A.6.2  | Prioritization using descending_urgency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 232 |

|     | A.6.3  | descending urgency vs. execution order                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 233 |

|     | A.6.4  | mutually_exclusive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 234 |

|     | A.6.5  | ${\color{red} \textbf{conflict\_free}} \ . \ . \ . \ . \ . \ . \ . \ . \ . \$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 235 |

|     | A.6.6  | preempts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 236 |

|     | A.6.7  | $fire\_when\_enabled, \ no\_implicit\_conditions \\ \ \ldots \\ $ | 238 |

|     | A.6.8  | always_ready, always_enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 239 |

|     | A.6.9  | aggressive_conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 240 |

|     | A.6.10 | Separating ActionValue method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 241 |