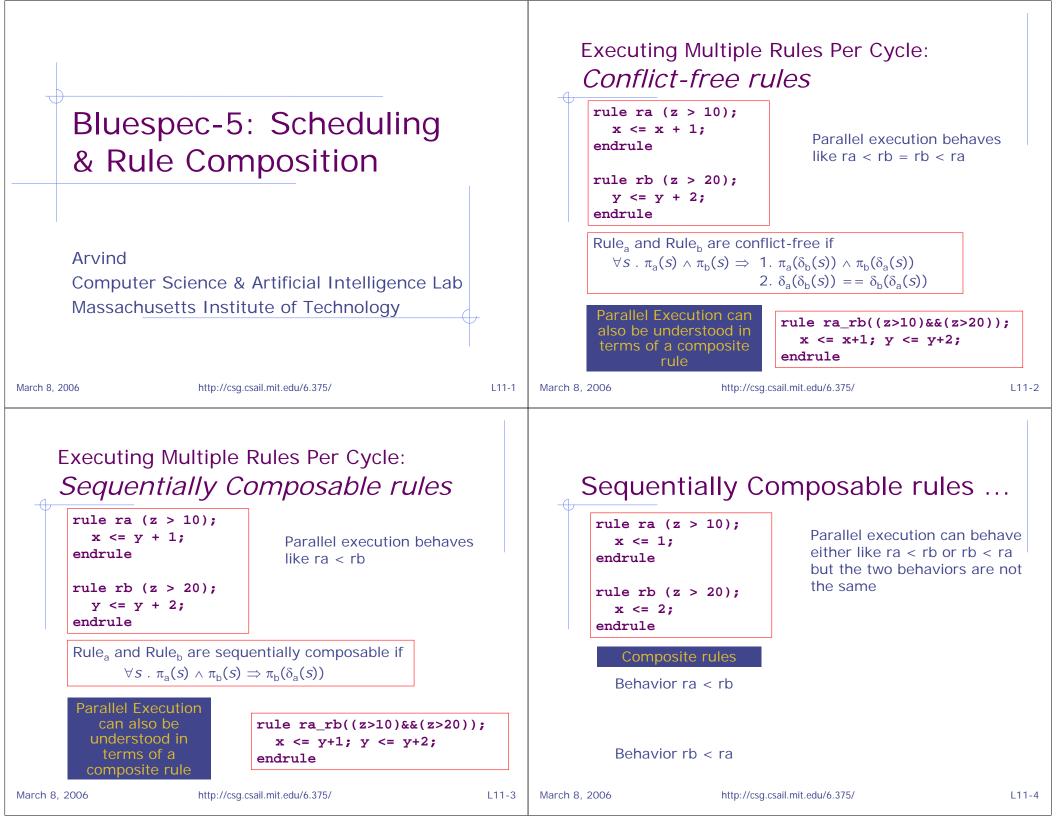

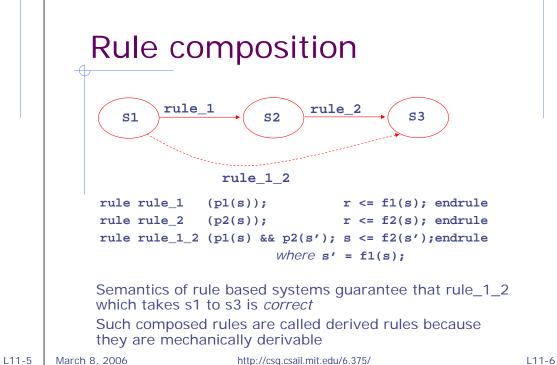

## A property of rule-based systems

- Adding a new rule to a system can only introduce new behaviors

- If the new rule is a *derived* rule, then it does not add new behaviors

Example of a derived rule: Given rules:  $R_a$ : when  $\pi_a(s) = s := \delta_a(s)$ ;  $R_{\rm b}$ : when  $\pi_{\rm b}(s) = s := \delta_{\rm b}(s)$ ; The following rule is a derived rule:  $R_{a,b}$ : when  $\pi_a(s) \& \pi_b(\delta_a(s)) => s := \delta_b(\delta_a(s));$ For CF rules  $\pi_{\mathbb{H}}(\delta_{n}(s)) = \pi_{\mathbb{H}}(s)$  and  $s := \delta_{\mathbb{H}}(\delta_{n}(s)) = \delta_{n}(\delta_{\mathbb{H}}(s))$ :

For SC rules

$$\pi_{b}(\delta_{a}(s)) = \pi_{b}(s)$$

and  $s := \delta_{b}(\delta_{a}(s));$

8. 2006

March 8, 2006

http://csg.csail.mit.edu/6.375/

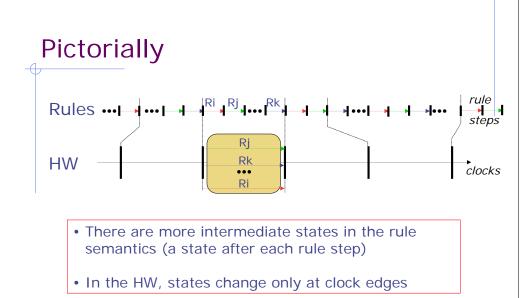

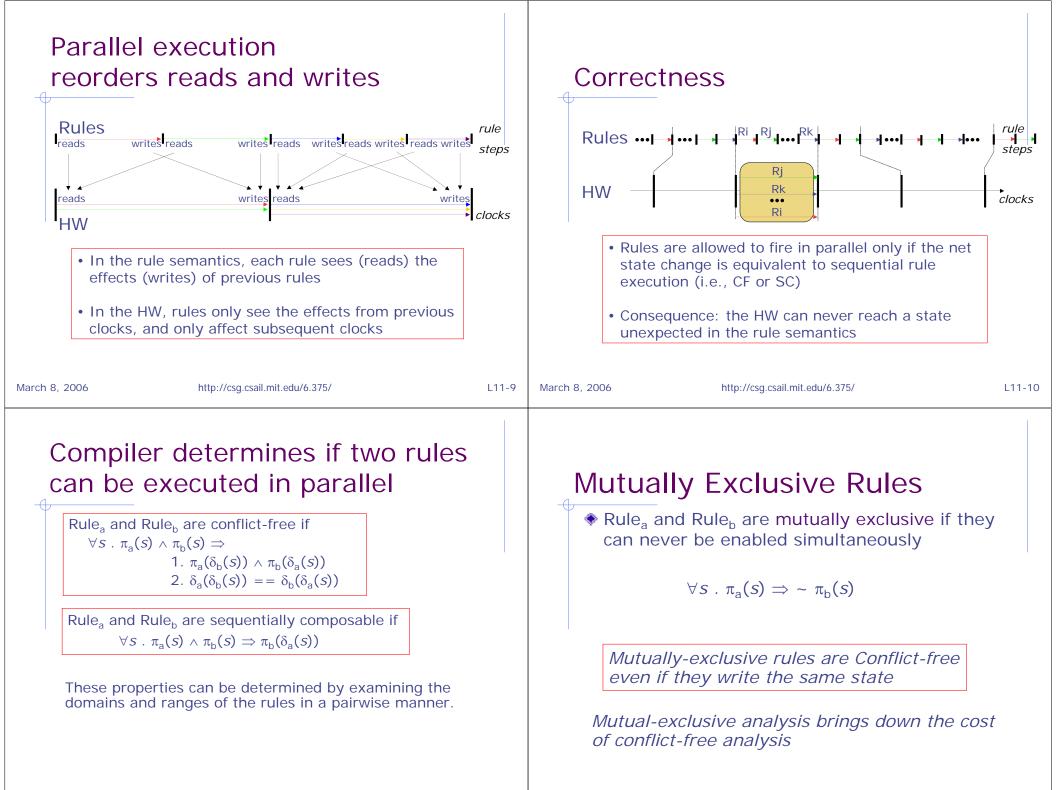

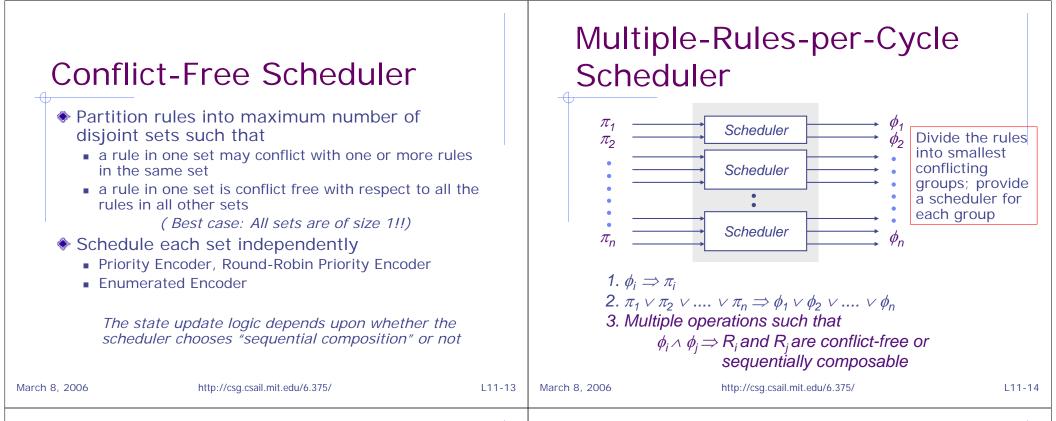

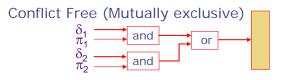

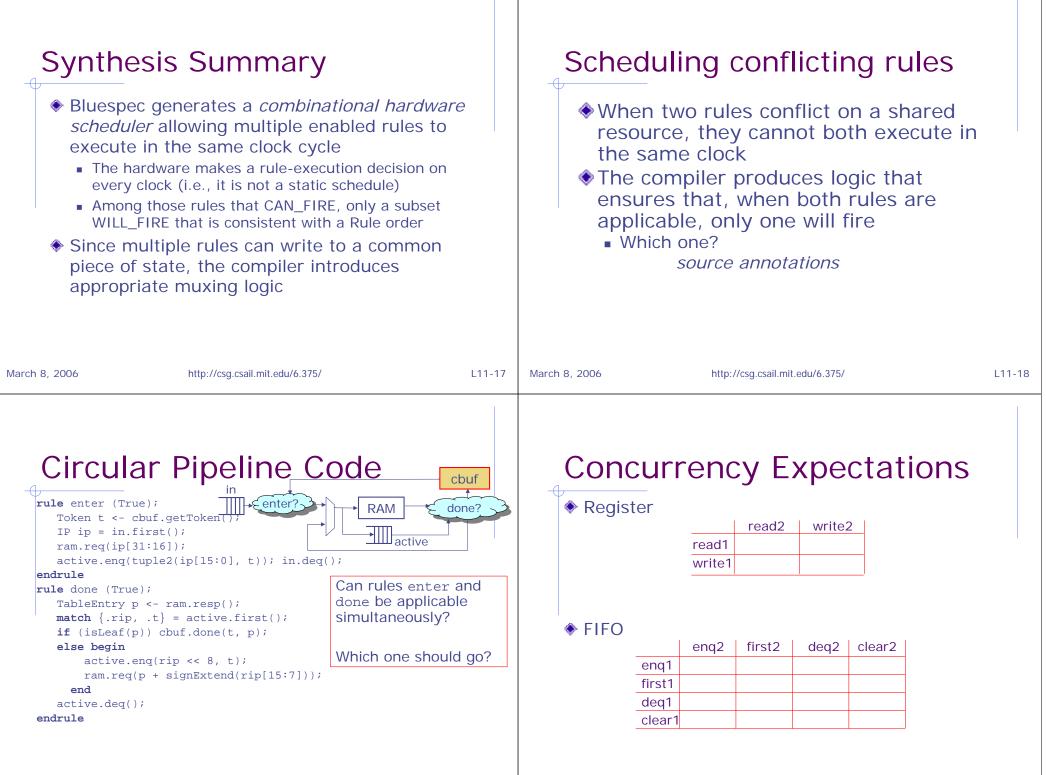

### Implementation oriented view of concurrency

- A. When executing a set of rules in a clock cycle, each rule reads state from the leading clock edge and sets state at the trailing clock edge

- $\Rightarrow$  none of the rules in the set can see the effects of any of the other rules in the set

- B. However, in one-rule-at-a-time semantics, each rule sees the effects of all previous rule executions

Thus, a set of rules can be safely executed together in a clock cycle only if A and B produce the same net state change

March 8, 2006

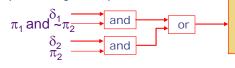

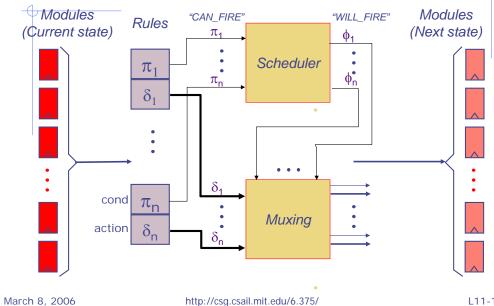

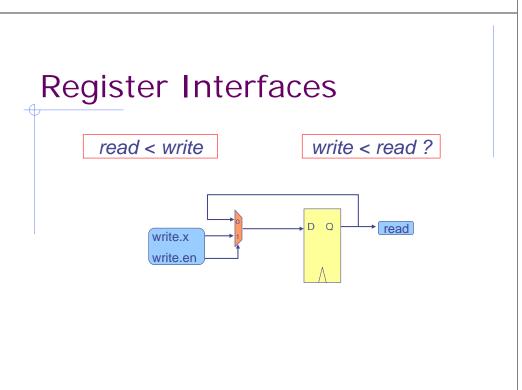

#### Muxing structure

Muxing logic requires determining for each register (action method) the rules that update it and under what conditions

Sequentially composable

#### Scheduling and control logic

**CF** rules either do not

update the

or are ME

same element

$\pi_1 \rightarrow -\pi_2$

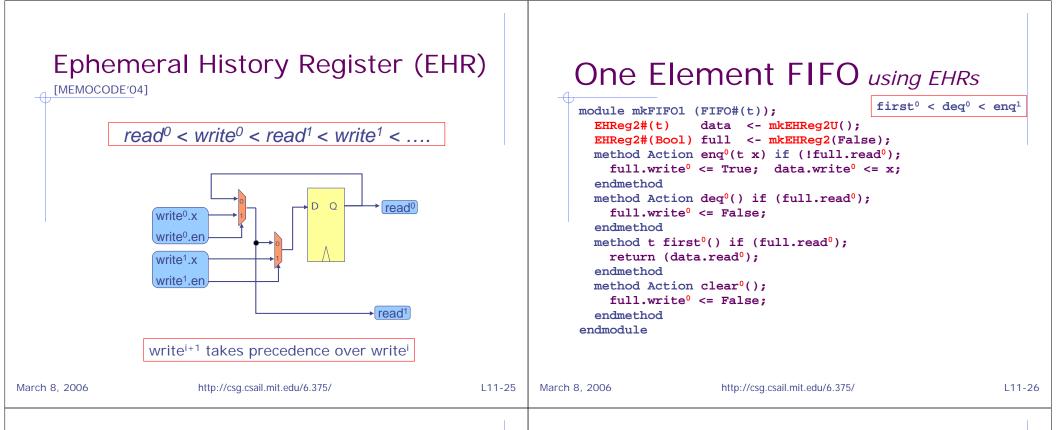

#### **One Element FIFO Two-Element FIFO** Concurrency? module mkFIF02#(FIFO#(t)); module mkFIF01 (FIF0#(t)); Reg#(t) data0 <-mkRegU; Reg#(Bool) full0 <- mkReg(False);</pre> data <- mkReqU();</pre> Req#(t) Reg#(t) data1 <-mkRegU; Reg#(Bool) full1 <- mkReg(False);</pre> Reg#(Bool) full <- mkReg(False);</pre> eng and deg? method Action eng(t x) if (!full); method Action eng(t x) if (!(full0 && full1)); full <= True;</pre> data <= x; data1 <= x; full1 <= True;</pre> endmethod if (full1) then begin data0 <= data1; full0 <= True; end method Action deq() if (full); endmethod full <= False: method Action deq() if (full0 || full1); endmethod if (full0) full0 <= False; else full1 <= False; method t first() if (full); endmethod return (data); method t first() if (full0 || full1); endmethod return ((full0)?data0:data1); method Action clear(); endmethod full <= False;</pre> Shift register implementation method Action clear(); endmethod full0 <= False; full1 <= False;</pre> endmodule endmethod endmodule March 8, 2006 http://csg.csail.mit.edu/6.375/ L11-21 March 8, 2006 http://csg.csail.mit.edu/6.375/ L11-22

#### The good news ...

It is always possible to transform your design to meet desired concurrency and functionality

#### EHR as the base case?

#### The bad news ...

- EHR cannot be written in Bluespec as defined so far

- Even though this transformation to meet the performance "specification" is mechanical, the Bluespec compiler currently does not do this transformation. Choices:

- do it manually and use a library of EHRs

- rely on a low level (dangerous) programming mechanism.

# One Element FIFO w/ RWires

**Pipeline FIFO**

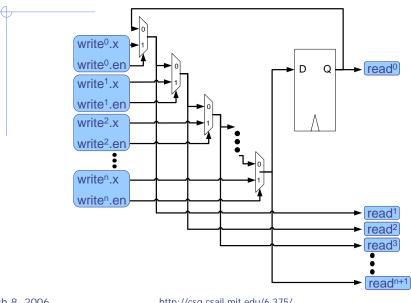

| <pre>module mkFIF01#(type t);     Reg#(t)    data &lt;- mkRegU();</pre>               | first < deq < enq |

|---------------------------------------------------------------------------------------|-------------------|

| <pre>Reg#(Bool) full &lt;- mkReg(False);</pre>                                        |                   |

| <pre>PulseWire deqW &lt;- mkPulseWire();<br/>method Action enq(t x) if (deqW   </pre> | !full);           |

| <pre>full &lt;= True; data &lt;= x;</pre>                                             |                   |

| endmethod                                                                             |                   |

| <pre>method Action deq() if (full);</pre>                                             |                   |

| <pre>full &lt;= False; deqW.send();</pre>                                             |                   |

| endmethod                                                                             |                   |

| <pre>method t first() if (full);</pre>                                                |                   |

| return (data);                                                                        |                   |

| endmethod                                                                             |                   |

| <pre>method Action clear();</pre>                                                     |                   |

| <pre>full &lt;= False;</pre>                                                          |                   |

| endmethod                                                                             |                   |

| endmodule                                                                             |                   |

|                                                                                       |                   |

#### One Element FIFO w/ RWires **Bypass FIFO**

| <pre>module mkFIF01#(type t);</pre>                    |                   |

|--------------------------------------------------------|-------------------|

| Reg#(t) data <- mkRegU();                              | enq < first < deq |

| <pre>Reg#(Bool) full &lt;- mkReg(False);</pre>         |                   |

| RWire#(t) enqW <- mkRWire();                           |                   |

| PulseWire deqW <- mkPulseWire();                       |                   |

| <pre>rule finishMethods(isJust(enqW.wget)    deq</pre> | W);               |

| <pre>full &lt;= !deqW;</pre>                           |                   |

| endrule                                                |                   |

| <pre>method Action enq(t x) if (!full);</pre>          |                   |

| <pre>enqW.wset(x); data &lt;= x;</pre>                 |                   |

| endmethod                                              |                   |

| <pre>method Action deq() if (full    isJust(enqW</pre> | .wget()));        |

| deqW.send();                                           |                   |

| endmethod                                              |                   |

| <pre>method t first() if (full    isJust(enqW.wg</pre> | et()));           |

| <pre>return (full ? data : unJust(enqW.wget));</pre>   |                   |

| endmethod                                              |                   |

| <pre>method Action clear();</pre>                      |                   |

| <pre>full &lt;= False;</pre>                           |                   |

| endmethod                                              |                   |

| endmodule                                              |                   |

|                                                        |                   |

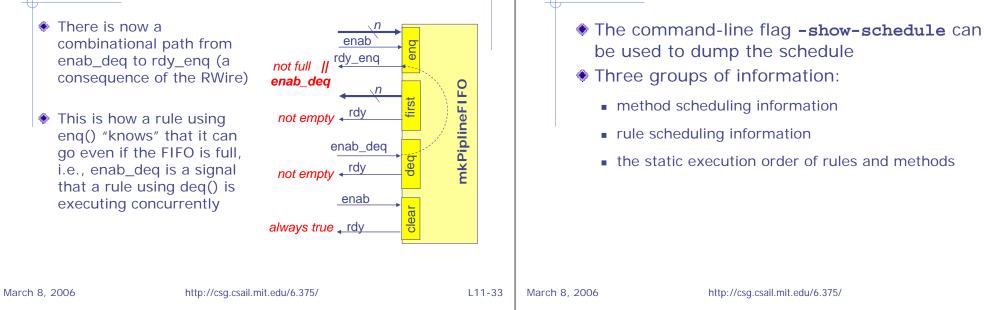

# A HW implication of mkPipelineFIFO

Viewing the schedule