| GCD:<br>Another implement                                                                      | ation                                            |

|------------------------------------------------------------------------------------------------|--------------------------------------------------|

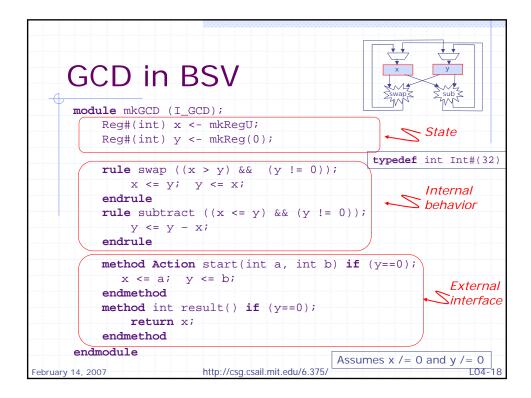

| <pre>module mkGCD (I_GCD);     Reg#(int) x &lt;- mkRegU;     Reg#(int) y &lt;- mkReg(0);</pre> | Combine swap<br>and subtract rule                |

| <pre>rule swapANDsub ((x &gt; y) &amp;&amp; (y</pre>                                           |                                                  |

| <pre>method Action start(int a, int</pre>                                                      | b) <b>if</b> (y==0);<br>Does it compute faster ? |

| endmodule l<br>February 14, 2007 http://csq.csail.mit.edu/6.375                                | · · · · · · · · · · · · · · · · · · ·            |

|                            | ated Veril                   | <u> </u>       | 000            |

|----------------------------|------------------------------|----------------|----------------|

| module mkGCD(CL            | RST_N,start_a,start          | _b,EN_start,RD | Z_start,       |

| re                         | <pre>sult,RDY_result);</pre> |                |                |

| input CLK; i               |                              |                |                |

| <pre>// action metho</pre> |                              |                |                |

|                            | start_a; input [31           | : 0] start_b;  | input EN_start |

| output RDY_st              |                              |                |                |

| <pre>// value method</pre> |                              |                |                |

|                            | ] result; output RDY         | _result;       |                |

| <pre>// register x a</pre> |                              |                |                |

| reg [31 : 0]               |                              |                |                |

|                            | x\$D_IN; wire x\$EN;         |                |                |

| reg [31 : 0]               |                              |                |                |

| wire [31 : 0]              | y\$D_IN; wire y\$EN;         |                |                |

| •••                        |                              |                |                |

| // rule RL_subt            |                              |                |                |

|                            | $IRE_RL\_subtract = x\_S$    | LE_Yd3 && !}   | 7_EQ_0al0;     |

| // rule RL swap            |                              |                |                |

| GCD: A Simple                                              | Test Bench                         |

|------------------------------------------------------------|------------------------------------|

| module mkTest ();                                          |                                    |

| Reg#(int) state <- mkReg(0);                               |                                    |

| I_GCD gcd <- mkGCD();                                      |                                    |

| <pre>rule go (state == 0);     gcd.start (423, 142);</pre> | Why do we need the state variable? |

| state <= 1;<br>endrule                                     |                                    |

| <pre>rule finish (state == 1);</pre>                       |                                    |

| \$display ("GCD of 423 & 142 =                             | =%d",gcd.result());                |

| <pre>state &lt;= 2; endrule</pre>                          |                                    |

| endrule                                                    |                                    |

| oruary 14, 2007 http://csg.csail.mit.edu/                  | 6.375/ LO4                         |

| GCD: Test Bench                                                                                                                                                             | ]                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| <pre>module mkTest (); Reg#(int) state &lt;- mkReg(0); Reg#(Int#(4)) c1 &lt;- mkReg(1); Reg#(Int#(7)) c2 &lt;- mkReg(1); I_GCD gcd &lt;- mkGCD();</pre>                     | Feeds all pairs (c1,c2)<br>1 < c1 < 7<br>1 < c2 < 15<br>to GCD |

| <pre>rule req (state==0);    gcd.start(signExtend(cl), sign    state &lt;= 1; endrule</pre>                                                                                 | Extend(c2));                                                   |

| <pre>rule resp (state==1);    \$display ("GCD of %d &amp; %d =%d"    if (c1==7) begin c1 &lt;= 1; c2 &lt;         else c1 &lt;= c1+1;    if (c2 == 63) state &lt;= 2;</pre> |                                                                |

| endrule<br>endmodule<br>February 14, 2007 http://csq.csail.mit.edu/6.:                                                                                                      | 375/ L04-2                                                     |

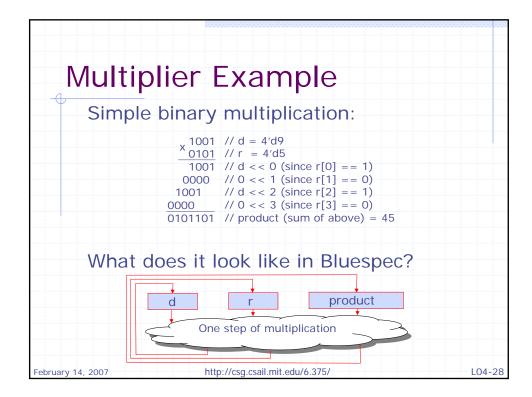

| <pre>Reg#(Int#(16)) d &lt;- mkReg(0);<br/>Reg#(Int#(16)) r &lt;- mkReg(0);<br/>rule cycle (r != 0);<br/>if (r[0] == 1) product &lt;= product + d;<br/>d &lt;= d &lt;&lt; 1;<br/>r &lt;= r &gt;&gt; 1;<br/>endrule</pre> | dule mkMult (I_                                                    | <pre>mult); product &lt;- mkReg(0);</pre> |                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------|-----------------------------|

| <pre>if (r[0] == 1) product &lt;= product + d;     d &lt;= d &lt;&lt; 1;     r &lt;= r &gt;&gt; 1; endrule  method Action start (Int#(16)x,Int#(16)y) if (r == 0);     d &lt;= signExtend(x); r &lt;= y;</pre>          | Reg#(Int#(16))                                                     | d <- mkReg(0);                            |                             |

|                                                                                                                                                                                                                         | <pre>if (r[0] == d &lt;= d &lt;&lt; 1; r &lt;= r &gt;&gt; 1;</pre> |                                           | t + d;                      |

|                                                                                                                                                                                                                         | method Action a                                                    | <pre>tart (Int#(16)x,Int#</pre>           | (16)y) <b>if</b> $(r == 0)$ |