|            | lysis               | ;      |           |     |        |           |                                         |

|------------|---------------------|--------|-----------|-----|--------|-----------|-----------------------------------------|

|            |                     |        |           |     |        |           |                                         |

|            | d Action            |        | 1 1       |     |        |           |                                         |

| II         | v0 then             |        |           |     |        |           |                                         |

| mothe      |                     |        |           |     | 1 1 1  | <= irue;  | end endmeth                             |

|            | d Action<br>vl then |        |           |     |        | <- Fals   | e. end                                  |

| <b>L</b> L |                     |        |           |     |        | end end   |                                         |

|            | erse                | Degin  | vu        |     | raise, | end end   |                                         |

|            |                     | Т      | urr       | ו m | ethods | into rule | es for analysis                         |

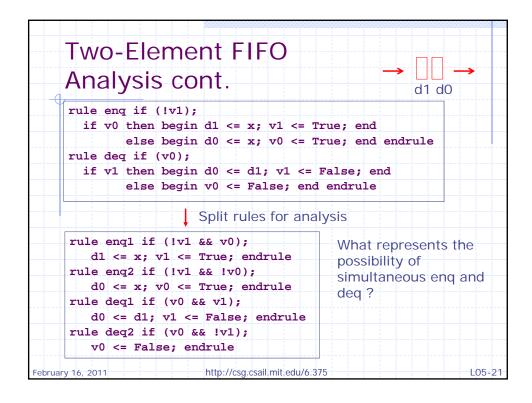

| rule       | eng if              | (!v1); |           |     |        |           |                                         |

| if         | v0 then             | begin  | <b>d1</b> | <=  | x; v1  | <= True;  | end                                     |

|            | else                | begin  | d0        | <=  | x; v0  | <= True;  | end endrule                             |

| rule       | deq if              | (v0);  |           |     |        |           |                                         |

| if         | vl then             | begin  | d0        | <=  | d1; v1 | <= Fals   | se; end                                 |

|            |                     |        |           |     | False; |           | han |

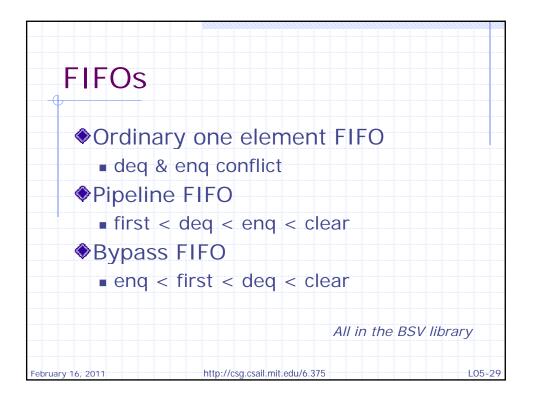

| One-Element Pipe                                                                                                                                                                                                                                                             | line FIFO                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| <pre>module mkPipelineFIFO1 (FIFO#(t)); Reg#(t) data &lt;- mkRegU(); Reg#(Bool) full &lt;- mkReg(False); RWire#(void) deqEN &lt;- mkRWire(); Bool deqp = isValid (deqEN method Action enq(t x) if                      (!full    deqp); full &lt;= True; data &lt;= x;</pre> | enab g !fu<br>!full ← rdy g or<br>!empty ← rdy g<br>.wget()));      |

| <pre>endmethod method Action deq() if (full); full &lt;= False; deqEN.wset(?); endmethod method t first() if (full);</pre>                                                                                                                                                   | This works correctly<br>in both cases (fifo full<br>and fifo empty) |

| <pre>return (data);<br/>endmethod<br/>method Action clear();<br/>full &lt;= False;<br/>endmethod endmodule</pre>                                                                                                                                                             | first < enq<br>deq < enq<br>enq < clear<br>deq < clear              |

| ary 16, 2011 http://csg.csail.mit.edu/6.375                                                                                                                                                                                                                                  | LO                                                                  |

| One-Element Pipe                                                                                                                                                                                                 | eline FIFO                                                                                                               |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| <pre>module mkPipelineFIFO1 (FIFO#(t));<br/>Reg#(t) data &lt;- mkRegU();<br/>Reg#(Bool) full &lt;- mkReg(False);<br/>RWire#(void) deqEN &lt;- mkRWire();<br/>Bool deqp = isValid (deqEN</pre>                    | enab<br>Ifull rdy<br>enab<br>enab<br>empty rdy<br>I.wget()));                                                            |  |  |

| <pre>method Action eng(t x) if</pre>                                                                                                                                                                             |                                                                                                                          |  |  |

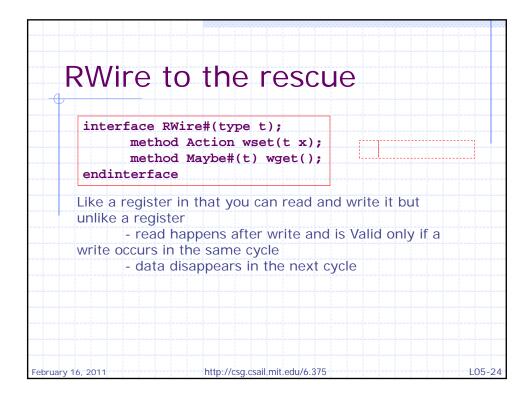

| <pre>full &lt;= True; data &lt;= x;<br/>endmethod<br/>method Action deq() if (full);<br/>full &lt;= False; deqEN.wset(?);</pre>                                                                                  | Rwire allows us to<br>create a combinational<br>path between eng and<br>deg but does not affect<br>the conflict analysis |  |  |

| endmethod<br><i>Conflict analysis:</i> Rwire deqEN allows of<br>enq & deq with the functionality deq <e<br>However, the conflicts around Register<br/>February 16, 2011<br/>http://csg.csail.mit.edu/6.37</e<br> | concurrent execution of<br>ang;<br>full remain!                                                                          |  |  |

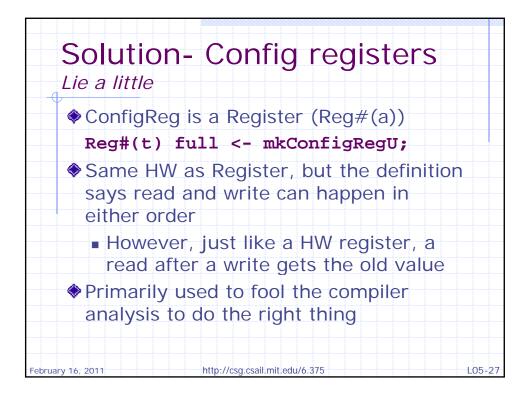

| One-Element Pipeline FIFO<br>A correct solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| module mkLFIF01 (FIF0#(t));       enab       g       !full         Reg#(t)       data <- mkRegU();       !full       rdy       g       or         Reg#(Bool)       full <- mkConfigReg(False);       enab       g       .full       g       or         RWire#(void)       deqEN <- mkRWire();       !empty       g       .full       .full |

| method Action enq(t x) if<br>(!full    deqp);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| full <= True;data <= x;endmethodNo conflicts around full:when both eng and deg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <pre>method Action deq() if (full);<br/>full &lt;= False; deqEN.wset(?);<br/>endmethod</pre> happen; if we want deq <<br>enq then full must be set<br>to True in case enq occurs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Scheduling constraint on<br>deqEn forces deq < enqfirst < enq<br>deq < enqenq < clear<br>deq < enqdeq < nq                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |