| cipalorulo                                             |                        |

|--------------------------------------------------------|------------------------|

| singlerule                                             |                        |

| rule doPipeline ;                                      |                        |

| <pre>let inst = iMem.req(pc);</pre>                    | fetch                  |

| <pre>let ppc = nextAddr(pc); let newPc = ppc;</pre>    |                        |

| <pre>let newIr=Valid(Fetch2Decode{pc:pc.ppc.ir</pre>   | <pre>nst:inst});</pre> |

| <pre>if(isValid(ir)) begin</pre>                       | execute                |

| <pre>let x = validValue(ir); let irpc = x.pc;</pre>    |                        |

| <pre>let ppc = x.ppc; let inst = x.inst;</pre>         |                        |

| <pre>let dInst = decode(inst);</pre>                   |                        |

| register fetch;                                        |                        |

| <pre>let eInst = exec(dInst, rVal1, rVal2, irpc,</pre> | ppc);                  |

| memory operation<br>rf update                          |                        |

| if (eInst.mispredict) begin                            |                        |

| newIr = Invalid;                                       |                        |

| newPc = eInst.addr; end                                |                        |

| end                                                    |                        |

| pc <= newPc; ir <= newIr;                              |                        |

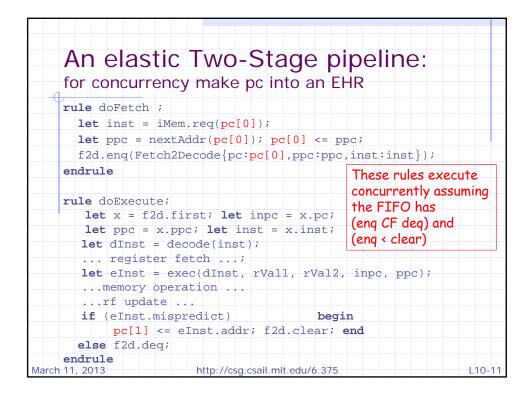

| An elastic Two-Stage p                                                                                                                               | ipeline                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| <pre>rule doFetch ; let inst = iMem.req(pc); let ppc = nextAddr(pc); pc &lt;= ppc; f2d.eng(Fetch2Decode{pc:pc.ppc;ppc,in</pre>                       | st:inst});                                                                                              |

| <pre>endrule rule doExecute; let x = f2d.first; let inpc = x.pc; let ppc = x.ppc; let inst = x.inst; let dInst = decode(inst); register fetch;</pre> | Can these rules<br>execute concurrently<br>assuming the FIFO<br>allows concurrent enq<br>deq and clear? |

| <pre>let eInst = exec(dInst, rVal1, rVal2,<br/>memory operation<br/>rf update</pre>                                                                  | inpc, ppc);                                                                                             |

| <pre>if (eInst.mispredict) begi</pre>                                                                                                                |                                                                                                         |

| endrule<br>rch 11, 2013 http://csg.csail.mit.edu/6.375                                                                                               | L10                                                                                                     |

| Ehr#(2, Bool) Va <- mkEhr(False);<br>Ehr#(2, t) db <- mkEhr(?); elem                          | #(t, tsz));<br>ere is only one<br>nent in the FIFO it |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Ehr#(2, Bool) va <- mkEhr(False);<br>Ehr#(2, t) db <- mkEhr(?);<br>cocio                      |                                                       |

|                                                                                               | les in da                                             |

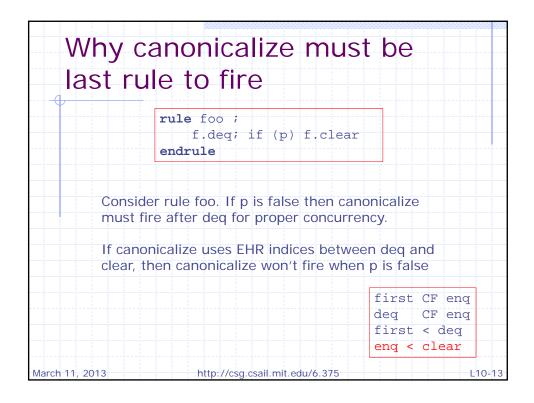

| <pre>rule canonicalize if(vb[2] &amp;&amp; !va[2]);</pre>                                     |                                                       |

| <pre>da[2] &lt;= db[2]; va[2] &lt;= True; vb[2] &lt; method Action eng(t x) if(!vb[0]);</pre> | <= False; endrule                                     |

| $db[0] \le x; vb[0] \le True; endmethod$                                                      |                                                       |

| method Action deg if (va[0]);                                                                 | first CF er                                           |

| <pre>va[0] &lt;= False; endmethod</pre>                                                       | deq CF er                                             |

| <pre>method t first if(va[0]);</pre>                                                          | first < dec                                           |

| return da[0]; endmethod                                                                       | enq < clear                                           |

| method Action clear;                                                                          |                                                       |

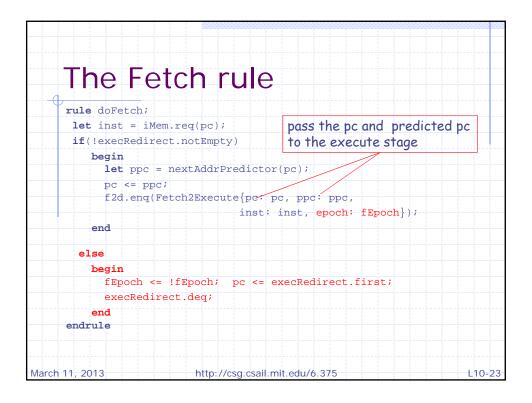

|                            | ased solution                                  |

|----------------------------|------------------------------------------------|

| rule doFetch ;             | Can these rules execute concurrently ?         |

| <b>let</b> inst=iMem.req   | (pc[0]);                                       |

| <b>let</b> ppc=nextAddr()  | pc[0]); pc[0]<=ppc;                            |

| f2d.enq(Fetch2Dec          | ode{pc:pc[0],ppc:ppc,epoch:epoch,              |

|                            | <pre>inst:inst});</pre>                        |

| endrule                    |                                                |

| <pre>rule doExecute;</pre> |                                                |

|                            | <pre>let inpc=x.pc; let inEp=x.epoch;</pre>    |

|                            | <pre>let inst = x.inst;</pre>                  |

| <b>if</b> (inEp == epoch   |                                                |

|                            | code(inst); register fetch;                    |

| memory oper                | <pre>ec(dInst, rVal1, rVal2, inpc, ppc);</pre> |

| rf update .                |                                                |

| if (eInst.misp             |                                                |

|                            | Inst.addr; epoch <= epoch + 1; end             |

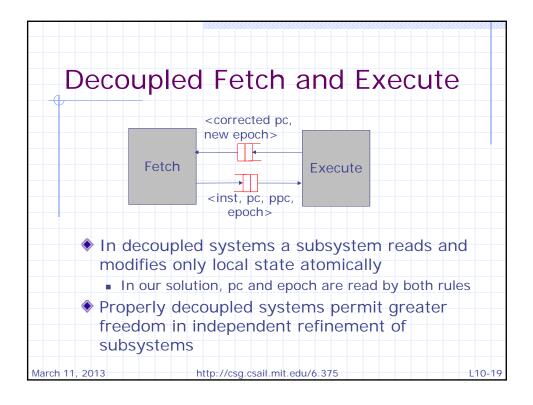

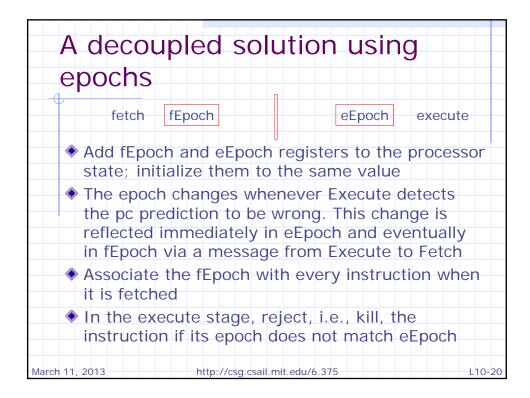

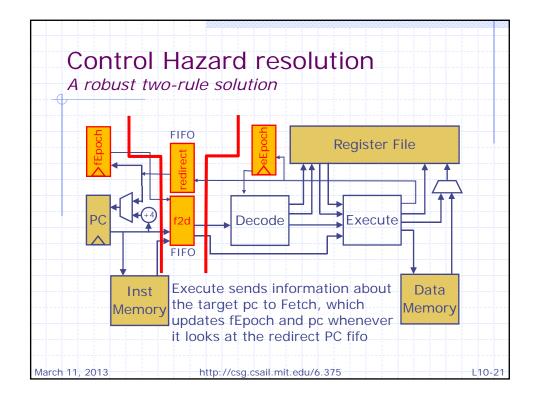

| Two-stage pipeline<br>Decoupled code structure                                                                                                                                                            |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| <pre>module mkProc(Proc);<br/>Fifo#(Fetch2Execute) f2d &lt;- mkFifo;<br/>Fifo#(Addr) execRedirect &lt;- mkFifo;<br/>Reg#(Bool) fEpoch &lt;- mkReg(False);<br/>Reg#(Bool) eEpoch &lt;- mkReg(False);</pre> |        |

| <pre>rule doFetch;<br/>let inst = iMem.req(pc);<br/><br/>f2d.enq( inst, fEpoch);<br/>endrule</pre>                                                                                                        |        |

| <pre>rule doExecute;<br/>if(inEp == eEpoch) begin<br/>Decode and execute the instruction; update state;<br/>In case of misprediction, execRedirect.eng(correct pc);</pre>                                 |        |

| end<br>f2d.deq;<br>endrule<br>endmodule<br>March 11, 2013 http://csg.csail.mit.edu/6.375                                                                                                                  | L10-22 |

| The E                         | Execute rul                    | if there was a feren                       |

|-------------------------------|--------------------------------|--------------------------------------------|

| rule doExecu                  | ite;                           | misprediction                              |

|                               | = f2d.first.inst; let pc       |                                            |

|                               | = f2d.first.ppc; let in        | Ep = f2d.first.epoch;                      |

|                               | = eEpoch) <b>begin</b>         |                                            |

|                               | st = decode(inst);             |                                            |

|                               | l1 = rf.rd1(validRegValue      |                                            |

|                               | l2 = rf.rd2(validRegValue      |                                            |

|                               | st = exec(dInst, rVall, r      |                                            |

|                               | t.iType == Ld) eInst.data      |                                            |

| ***************************** | req(MemReq{op: Ld, addr:       | ***************************************    |

|                               | (eInst.iType == St) <b>let</b> |                                            |

|                               |                                | <pre>eInst.addr, data: eInst.data});</pre> |

|                               | alid(eInst.dst))               |                                            |

|                               | (validRegValue(eInst.dst)      | , eInst.data);                             |

|                               | t.mispredict) <b>begin</b>     |                                            |

| execRe                        | edirect.enq(eInst.addr);       | eEpoch <= !inEp;                           |

| end                           |                                |                                            |

| end                           | Can these r                    | rules execute concurrently?                |

| f2d.deq;                      |                                |                                            |

| endrule                       |                                |                                            |

| March 11, 2013                | http://csg.csail.mit.e         | du/6.375 L10-24                            |

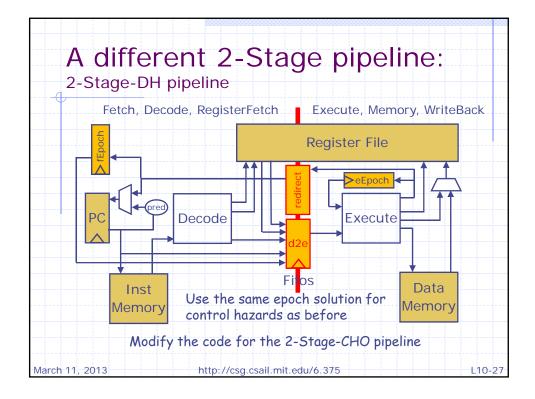

| ge-    | DH p                                           | Л                                                                         | $) \leftarrow 1$                                                                                                                                              |                                                                                                                                                                                                        |                                                                                                                                                                                                                                                     |                                 |                                 |                                 |

|--------|------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|---------------------------------|

| Drog(I | Proc);                                         |                                                                           |                                                                                                                                                               |                                                                                                                                                                                                        |                                                                                                                                                                                                                                                     |                                 |                                 |                                 |

|        |                                                | <-                                                                        | mkR                                                                                                                                                           | eall;                                                                                                                                                                                                  |                                                                                                                                                                                                                                                     |                                 |                                 |                                 |

|        |                                                |                                                                           |                                                                                                                                                               |                                                                                                                                                                                                        |                                                                                                                                                                                                                                                     |                                 |                                 |                                 |

|        |                                                |                                                                           |                                                                                                                                                               |                                                                                                                                                                                                        | ;                                                                                                                                                                                                                                                   |                                 |                                 |                                 |

|        |                                                |                                                                           |                                                                                                                                                               | -passpassta                                                                                                                                                                                            |                                                                                                                                                                                                                                                     |                                 |                                 |                                 |

| ol)    | fEpoch                                         | <-                                                                        | mkR                                                                                                                                                           | eq(Fal                                                                                                                                                                                                 | se);                                                                                                                                                                                                                                                |                                 |                                 |                                 |

|        |                                                |                                                                           |                                                                                                                                                               |                                                                                                                                                                                                        |                                                                                                                                                                                                                                                     |                                 |                                 |                                 |

|        |                                                |                                                                           |                                                                                                                                                               |                                                                                                                                                                                                        |                                                                                                                                                                                                                                                     |                                 |                                 |                                 |

| ddr) e | execRedi                                       | rect                                                                      | : <-                                                                                                                                                          | mkFif                                                                                                                                                                                                  | 0;                                                                                                                                                                                                                                                  |                                 |                                 |                                 |

| Fetch  |                                                |                                                                           |                                                                                                                                                               |                                                                                                                                                                                                        |                                                                                                                                                                                                                                                     |                                 |                                 |                                 |

| Execut |                                                |                                                                           |                                                                                                                                                               |                                                                                                                                                                                                        |                                                                                                                                                                                                                                                     |                                 |                                 |                                 |

|        | dr)<br>ecode2<br>ol)<br>ol)<br>ddr) e<br>Fetch | dr) pc<br>rf<br>iMem<br>dMem<br>ecode2Execute<br>ol) fEpoch<br>ol) eEpoch | <pre>dr) pc &lt;-     rf &lt;-     iMem &lt;-     dMem &lt;-     dMem &lt;- ecode2Execute) d2 ol) fEpoch &lt;- ol) eEpoch &lt;- ddr) execRedirect Fetch</pre> | <pre>dr) pc &lt;- mkR<br/>rf &lt;- mkR<br/>iMem &lt;- mkI<br/>dMem &lt;- mkD<br/>ecode2Execute) d2e &lt;<br/>ol) fEpoch &lt;- mkR<br/>ol) eEpoch &lt;- mkR<br/>ddr) execRedirect &lt;-<br/>Fetch</pre> | <pre>dr) pc &lt;- mkRegU;<br/>rf &lt;- mkRFile;<br/>iMem &lt;- mkIMemory<br/>dMem &lt;- mkDMemory<br/>ecode2Execute) d2e &lt;- mkFi<br/>ol) fEpoch &lt;- mkReg(Fal<br/>ol) eEpoch &lt;- mkReg(Fal<br/>ddr) execRedirect &lt;- mkFif<br/>Fetch</pre> | <pre>dr) pc &lt;- mkRegU;</pre> | <pre>dr) pc &lt;- mkRegU;</pre> | <pre>dr) pc &lt;- mkRegU;</pre> |

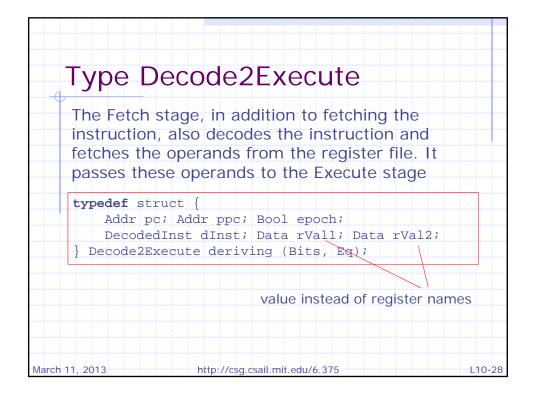

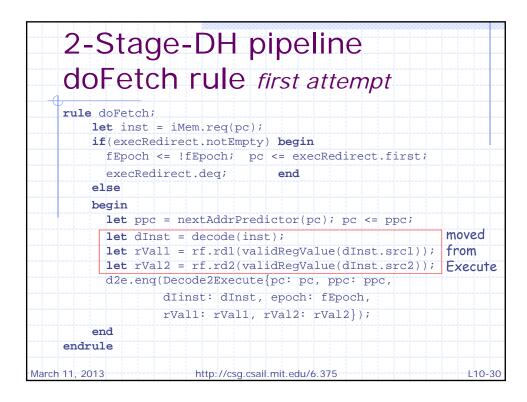

|               | Stage-DH pipeline<br>Execute rule <i>first attempt</i>                                                                      |        |

|---------------|-----------------------------------------------------------------------------------------------------------------------------|--------|

|               | loExecute;                                                                                                                  |        |

| le            | et x = d2e.first;                                                                                                           |        |

| le            | et dInst = x.dInst; let pc = x.pc;                                                                                          |        |

| le            | et ppc = x.ppc; let epoch = x.epoch;                                                                                        |        |

| le            | et rVal1 = x.rVal1; let rVal2 = x.rVal2;                                                                                    |        |

| if            | (epoch == eEpoch) <b>begin</b>                                                                                              |        |

|               | <pre>let eInst = exec(dInst, rVal1, rVal2, pc, ppc); if(eInst.iType == Ld) eInst.data &lt;-</pre>                           |        |

|               | <pre>dMem.req(MemReq{op:Ld, addr:eInst.addr, data:?}); else if (eInst.iType == St) let d &lt;-</pre>                        |        |

| no<br>change  | <pre>dMem.req(MemReq{op:St, addr:eInst.addr, data:eInst.dat if (isValid(eInst.dst) &amp;&amp;</pre>                         | .a});  |

| chunge        | <pre>validValue(eInst.dst).regType == Normal) rf.wr(validRegValue(eInst.dst), eInst.data); if(eInst.mispredict) begin</pre> |        |

|               | <pre>execRedirect.enq(eInst.addr); eEpoch &lt;= !eEpoch; end</pre>                                                          |        |

| SP            | end<br>Re.deg;                                                                                                              |        |

| endrul        |                                                                                                                             |        |

| March 11, 201 | 3 http://csg.csail.mit.edu/6.375                                                                                            | L10-31 |

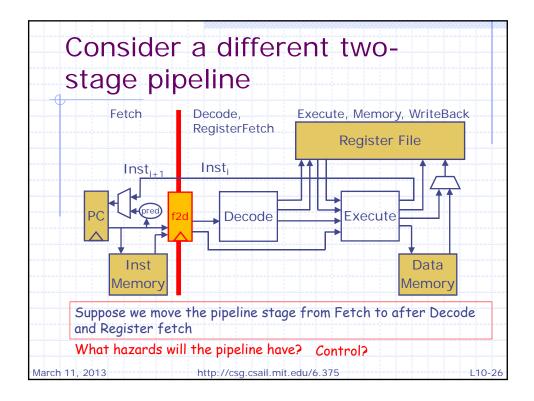

| Dat            | a Haz                                | zarc    | S                                              |                             |        |        |      |        |      |                  |

|----------------|--------------------------------------|---------|------------------------------------------------|-----------------------------|--------|--------|------|--------|------|------------------|

|                | fetch &                              |         | ]→€<br>d2e                                     | execute                     | 3      |        | oc   | rf     | dMen |                  |

|                | <i>time</i> t(<br>FDstage<br>EXstage |         |                                                |                             | $FD_5$ |        | t7   | • • •  |      |                  |

|                |                                      |         | Add(R1<br>Add(R4                               | -                           |        |        |      |        |      | *****            |

|                | must be st                           | alled u | intil I <sub>1</sub> เ                         | update                      | s the  | regi   | ster | file   |      |                  |

|                | <i>time</i> t(<br>FDstage<br>EXstage |         | t2 t3<br>FD <sub>2</sub> FI<br>EX <sub>1</sub> |                             | $FD_4$ | $FD_5$ |      | • • •  |      |                  |

| March 11, 2013 |                                      | http:// | <i>next</i><br>/csg.csail.                     | <i>lecture</i><br>mit.edu/6 |        | solvi  | ng D | oata F |      | <b>S</b><br>0-32 |