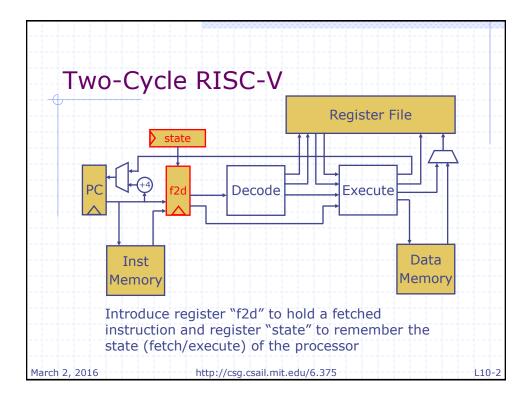

| Two-Cy            | cle RISC-V                             |  |

|-------------------|----------------------------------------|--|

| module mkPro      | c(Proc);                               |  |

| Reg#(Addr)        | pc <- mkRegU;                          |  |

| RFile             | rf <- mkRFile;                         |  |

| IMemory           | iMem <- mkIMemory;                     |  |

| DMemory           | dMem <- mkDMemory;                     |  |

| Reg#(Data)        | <pre>f2d &lt;- mkRegU;</pre>           |  |

| Reg#(State        | ) <pre>state &lt;- mkReg(Fetch);</pre> |  |

| <b>rule</b> doFet | ch (state == Fetch);                   |  |

| let in            | st = iMem.req(pc);                     |  |

| f2d <=            | inst;                                  |  |

| state             | <= Execute;                            |  |

| endrule           |                                        |  |

| Two-Cycle RISC V                                                        |

|-------------------------------------------------------------------------|

| The Execute Cycle                                                       |

| <pre>rule doExecute(stage==Execute);</pre>                              |

| <pre>let inst = f2d;</pre>                                              |

| <pre>let dInst = decode(inst);</pre>                                    |

| <pre>let rVal1 = rf.rd1(fromMaybe(?, dInst.src1));</pre>                |

| <pre>let rVal2 = rf.rd2(fromMaybe(?, dInst.src2));</pre>                |

| <pre>let eInst = exec(dInst, rVal1, rVal2, pc);</pre>                   |

| <pre>if(eInst.iType == Ld)</pre>                                        |

| eInst.data <- dMem.req(MemReq{op: Ld, addr:                             |

| eInst.addr, data: ?});                                                  |

| <pre>else if(eInst.iType == St)</pre>                                   |

| <pre>let d &lt;- dMem.req(MemReq{op: St, addr:</pre>                    |

| <pre>eInst.addr, data: eInst.data});</pre>                              |

| <pre>if (isValid(eInst.dst))</pre>                                      |

| <pre>rf.wr(fromMaybe(?, eInst.dst), eInst.data);</pre>                  |

| <pre>pc &lt;= eInst.brTaken ? eInst.addr : pc + 4;</pre>                |

| <pre>state &lt;= Fetch; no change from single-cycle</pre>               |

| endrule endmodule<br>March 2, 2016 http://csg.csail.mit.edu/6.375 L10-4 |

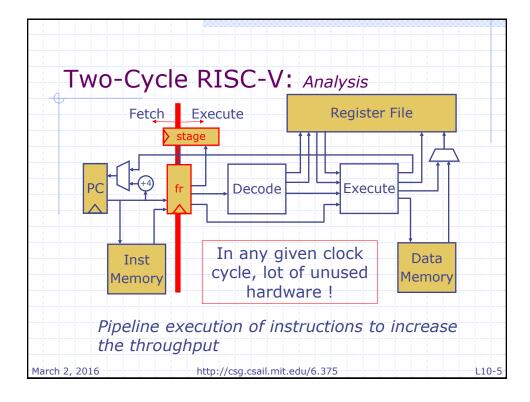

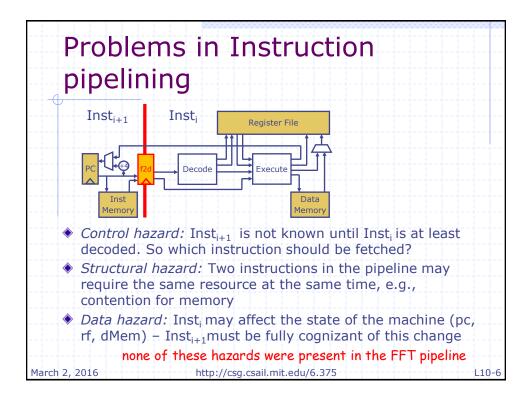

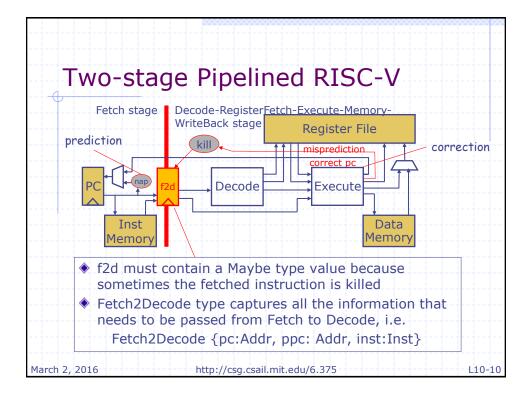

| Pipelining Two-Cycle F<br>single rule                                                    |                                            |

|------------------------------------------------------------------------------------------|--------------------------------------------|

| Siligie luie                                                                             |                                            |

| rule doPipeline ;                                                                        |                                            |

| <pre>let instF = iMem.req(pc);</pre>                                                     | fetch                                      |

| <pre>let ppcF = nap(pc); let nextPc = pp</pre>                                           | cF;                                        |

| <pre>let newf2d = Valid (Fetch2Decode{pc</pre>                                           | :pc,ppc:ppcF,                              |

| in                                                                                       | st:instF});                                |

| <pre>if(isValid(f2d)) begin</pre>                                                        | execute                                    |

| <pre>let x = fromMaybe(?,f2d); let pcD</pre>                                             | = x.pc;                                    |

| <pre>let ppcD = x.ppc; let instD = x.in let dInst = decode(instD); register fetch;</pre> | st;<br>these values are<br>being redefined |

| <pre>let eInst = exec(dInst, rVal1, rVa<br/>memory operation<br/>rf update</pre>         | 12, pcD, ppcD);                            |

| if (eInst.mispredict) begin nextPc                                                       | = eInst.addr;                              |

|                                                                                          | = Invalid; end                             |

| end                                                                                      |                                            |

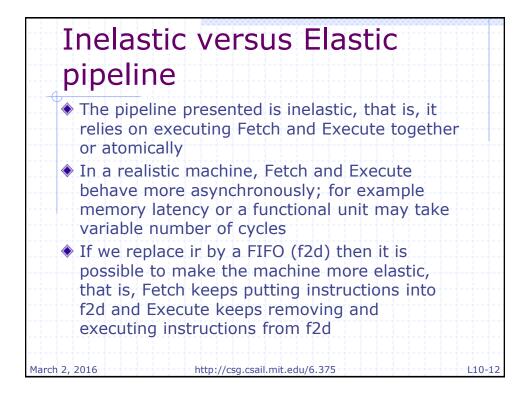

|                                         | sed solution                                                                        |

|-----------------------------------------|-------------------------------------------------------------------------------------|

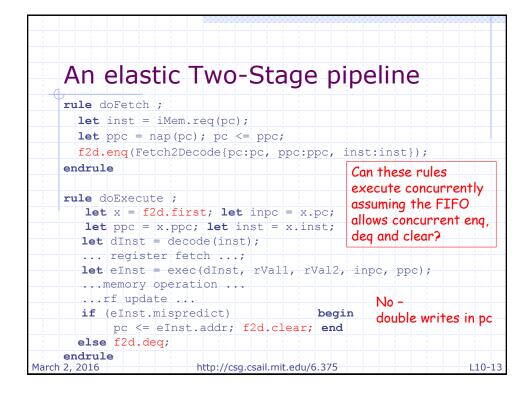

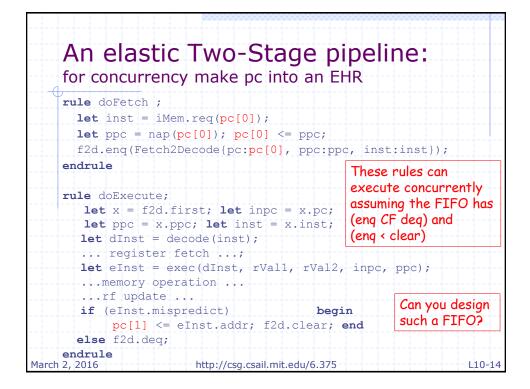

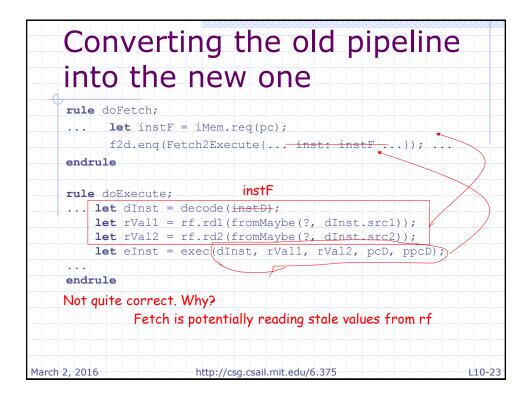

| rule doFetch ;                          | Can these rules execute concurrently ?                                              |

| <b>let</b> instF=iMem.req(              |                                                                                     |

| <b>let</b> ppcF=nap(pc[0])              | Ves                                                                                 |

| f2d.enq(Fetch2Decod                     | <pre>le{pc:pc[0],ppc:ppcF,epoch:epoch,     inst:instF});</pre>                      |

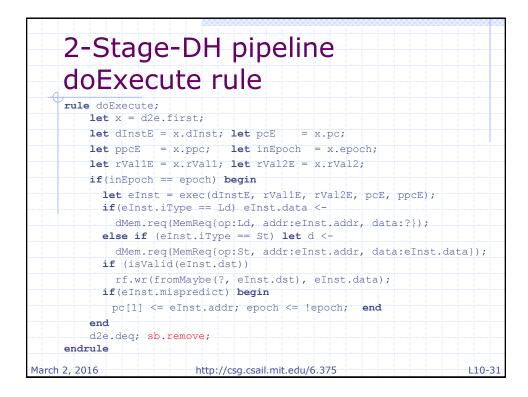

| <pre>endrule rule doExecute;</pre>      | Two values for epoch are sufficient !                                               |

|                                         | .et pcD=x.pc; let inEp=x.epoch;                                                     |

|                                         | <pre>let instD = x.inst;</pre>                                                      |

| <pre>if(inEp == epoch)</pre>            |                                                                                     |

|                                         | <pre>de(instD); register fetch;<br/>(dInst, rVal1, rVal2, pcD, ppcD);<br/>ion</pre> |

| rf update                               |                                                                                     |

| <b>if</b> (eInst.mispre                 | edict) begin                                                                        |

| *************************************** | <pre>nst.addr; epoch &lt;= next(epoch); end</pre>                                   |

| f2d.deg; endrule                        | end                                                                                 |

|                                         |                                                                                     |

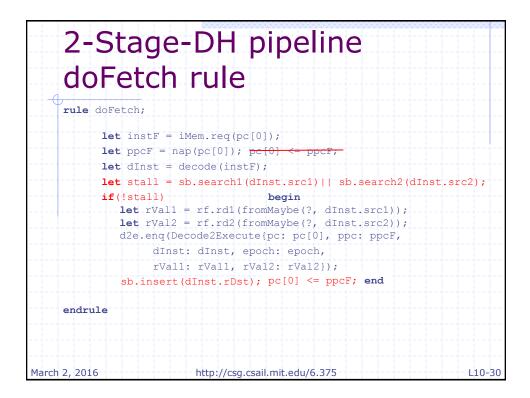

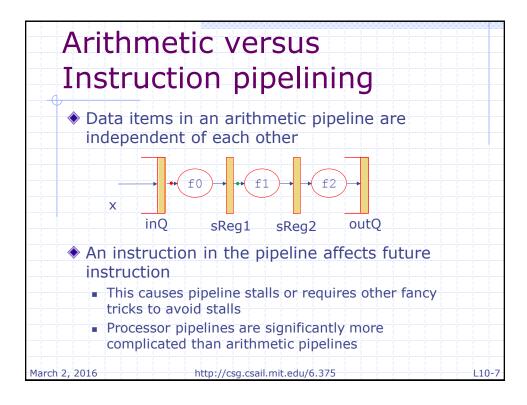

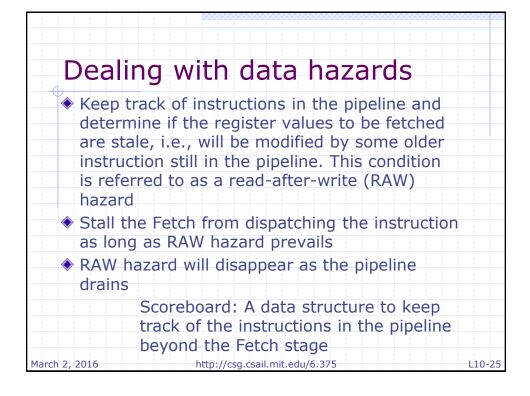

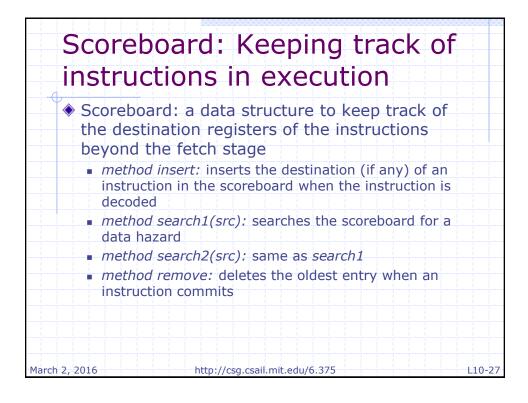

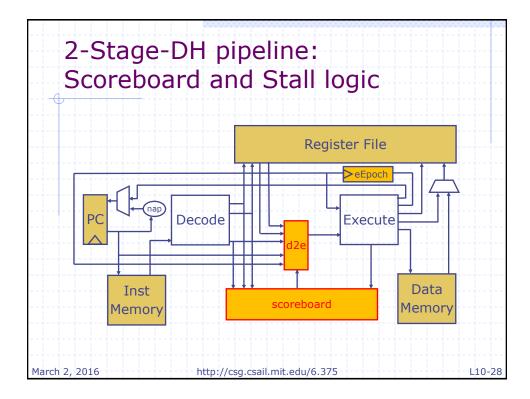

| doFetch rule                                                                                                                                                                                                                  |                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

|                                                                                                                                                                                                                               | What should happen to<br>pc when Fetch stalls?                      |

| <pre>if(!stall) begin     let rVal1 = rf.rdl(fromMaybe(?, dIn     let rVal2 = rf.rd2(fromMaybe(?, dIn     d2e.enq(Decode2Execute{pc: pc[0], p         dInst: dInst, epoch: epoch,         rVal1: rVal1, rVal2: rVal2});</pre> | st.src1));<br>st.src2));                                            |

| sb.insert(dInst.rDst); end<br>endrule<br>To avoid structural hazards, scoreboard<br>must allow two search ports                                                                                                               | pc should change only<br>when the instruction<br>is enqueued in d2e |