### **Complex Pipelining**

#### Daniel Sanchez Computer Science and Artificial Intelligence Laboratory M.I.T.

September 25, 2023

MIT 6.5900 Fall 2023

Instruction pipelining becomes complex when we want high performance in the presence of

- Multi-cycle operations, for example:

- Full or partially pipelined floating-point units, or

- Long-latency operations, e.g., divides

- Variable-latency operations, for example:

- Memory systems with variable access time

- Replicated functional units, for example:

- Multiple floating-point or memory units

### CDC 6600 Seymour Cray, 1963

- A fast pipelined machine with 60-bit words

- 128 Kword main memory capacity, 32 banks

- Ten functional units (parallel, unpipelined)

- Floating Point: adder, 2 multipliers, divider

- Integer: adder, 2 incrementers, ...

- Hardwired control

- Dynamic scheduling of instructions using a scoreboard

- Ten Peripheral Processors for Input/Output

- A fast multi-threaded 12-bit integer ALU

- Very fast clock, 10 MHz (FP add in 4 clocks)

- >400,000 transistors, 750 sq. ft., 5 tons, 150 kW, new freon-based cooling technology

- Fastest machine in world for 5 years (until CDC 7600)

- Over 100 sold (\$7-10M each)

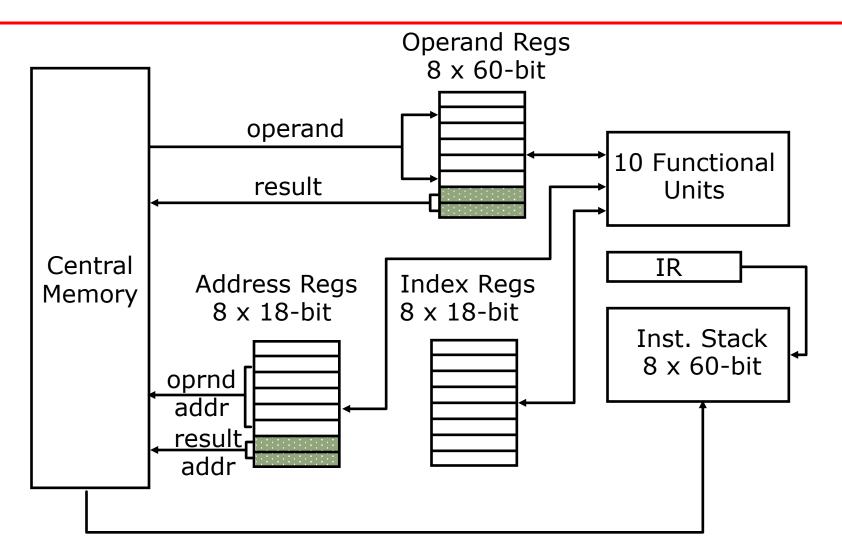

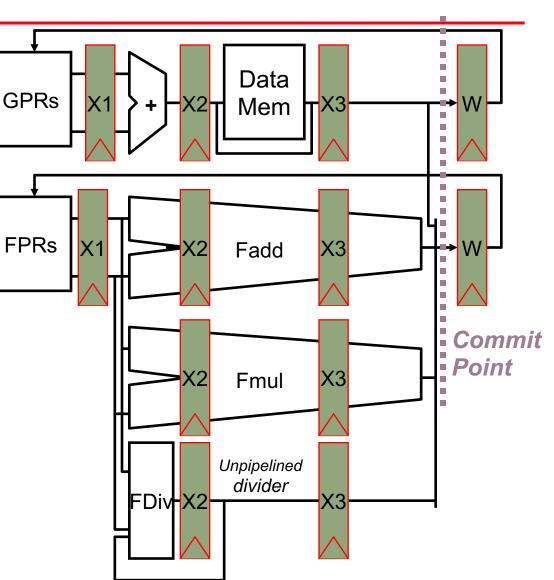

### CDC 6600: Datapath

### CDC 6600: A Load/Store Architecture

- Separate instructions to manipulate three types of registers

- 8 60-bit data registers (X)

- 8 18-bit address registers (A)

- 8 18-bit index registers (B)

- All arithmetic and logic instructions are reg-to-reg

$Ri \leftarrow (Rj) op (Rk)$

• Only Load and Store instructions refer to memory!

- Touching address registers 1 to 5 initiates a load

6 to 7 initiates a store

- very useful for vector operations

### **CDC6600:** Vector Addition

B1  $\leftarrow$  - n loop: JZE B1, exit A1  $\leftarrow$  B1 + a1 A2  $\leftarrow$  B1 + b1 X6  $\leftarrow$  X1 + X2 A6  $\leftarrow$  B1 + c1 B1  $\leftarrow$  B1 + 1 jump loop

*load into X1 load into X2*

store X6

Ai = address register Bi = index register Xi = data register

more on vector processing later...

# We will present complex pipelining issues more abstractly ...

September 25, 2023

Interaction between the Floating point datapath and the Integer datapath is determined largely by the ISA

#### RISC-V ISA (with F/D extensions)

- separate register files for FP and Integer instructions the only interaction is via a set of move instructions (some ISAs don't even permit this)

- separate load/store for FPRs and GPRs, but both use GPRs for address calculation

- branches only take GPRs as sources; FP compare instructions write result to a GPR, which can then be used in a branch

Much more hardware than an integer unit

Single-cycle floating point unit is a bad idea - why?

- it is common to have several floating point units

- it is common to have different types of FPUs *Fadd, Fmul, Fdiv, ...*

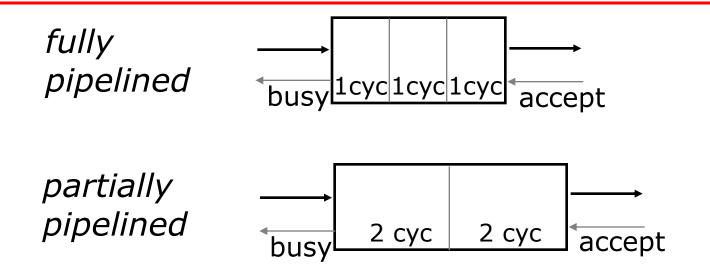

- an FPU may be pipelined, partially pipelined or not pipelined

To operate several FPUs concurrently, the register file needs to have more read and write ports

### **Functional Unit Characteristics**

Functional units have internal pipeline registers

- ⇒ operands are latched when an instruction enters a functional unit

- ⇒ inputs to a functional unit (e.g., register file) can change during a long latency operation

### Realistic Memory Systems

Latency of access to the main memory is usually much higher than one cycle and often unpredictable *Solving this problem is a central issue in computer architecture*

# Common approaches to improving memory performance

• separate instruction and data memory ports

$\Rightarrow$  no self-modifying code

caches

single cycle except in case of a miss  $\Rightarrow$  stall

- interleaved memory multiple memory accesses ⇒ bank conflicts

- split-phase memory operations

- ⇒ out-of-order responses

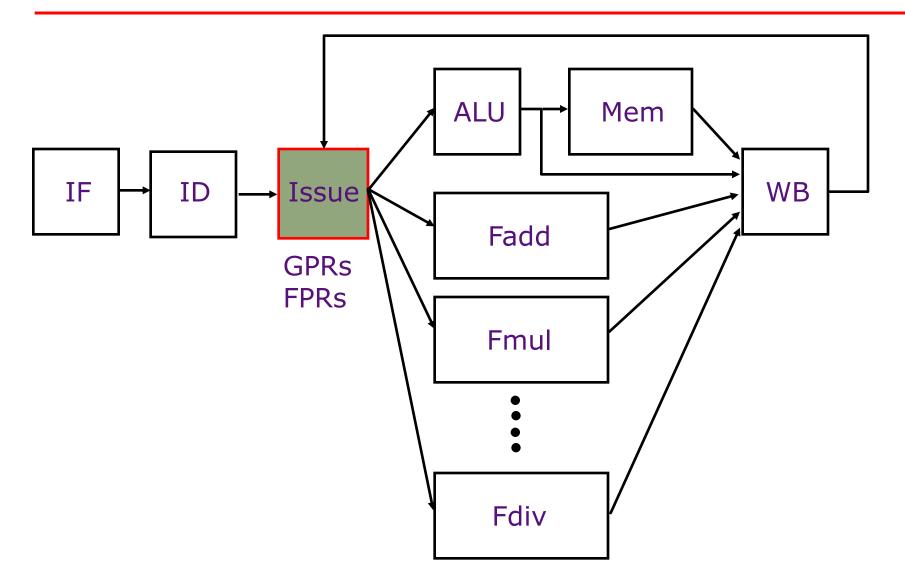

### **Complex Pipeline Structure**

### **Complex Pipeline Control Issues**

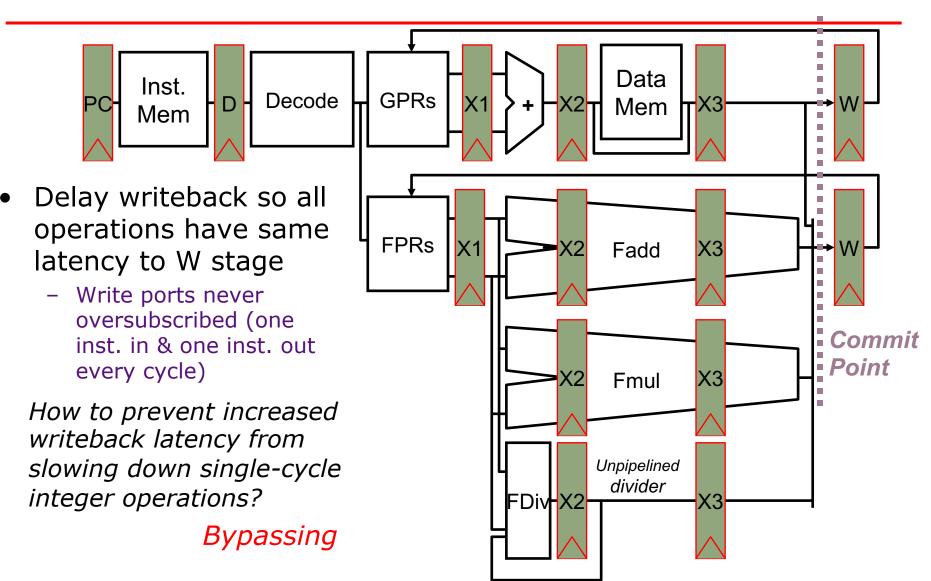

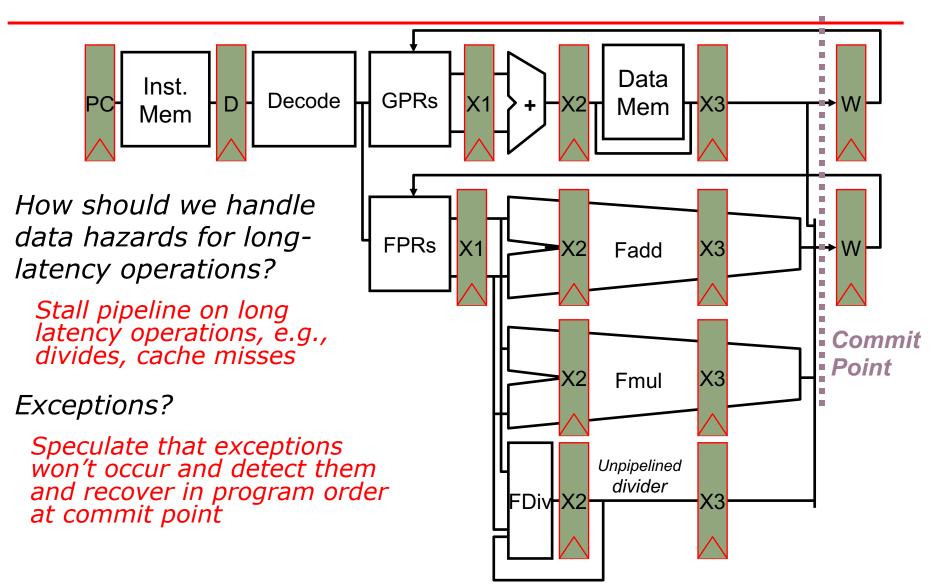

- Structural hazards at the execution stage if some FPU or memory unit is not pipelined and takes more than one cycle

- Structural hazards at the write-back stage due to variable latencies of different function units

- Out-of-order write hazards due to variable latencies of different function units

- How to handle exceptions?

# **Complex In-Order Pipeline**

September 25, 2023

MIT 6.5900 Fall 2023

# **Complex In-Order Pipeline**

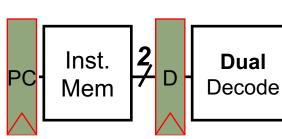

# Superscalar In-Order Pipeline

- Fetch two instructions per cycle; issue both simultaneously *if* one is integer/memory and other is floating-point

- Inexpensive way of increasing throughput

- Examples: Alpha 21064 (1992) MIPS R5000 series (1996)

- Can be extended to wider issue but register file ports and bypassing costs grow quickly

- E.g., 4-issue UltraSPARC

September 25, 2023

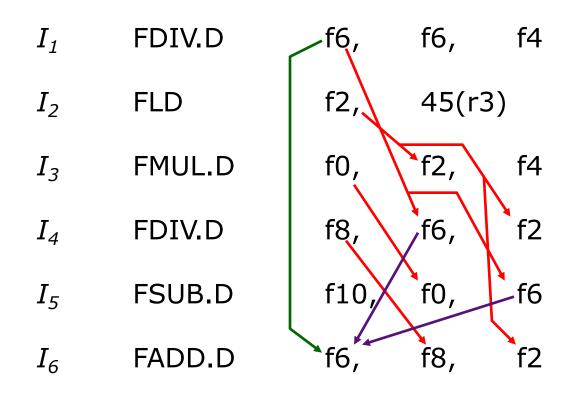

### **Dependence Analysis**

Needed to Exploit Instruction-level Parallelism

### Types of Data Hazards

# Consider executing a sequence of $r_k \leftarrow (r_i)$ op $(r_j)$ type of instructions

Data-dependenceRead-after-Write $r_3 \leftarrow (r_1)$  op  $(r_2)$ Read-after-Write $r_5 \leftarrow (r_3)$  op  $(r_4)$ (RAW) hazard

### **Detecting Data Hazards**

Range and Domain of instruction i

- R(i) = Registers (or other storage) modified by instruction i

- D(i) = Registers (or other storage) read by instruction i

Suppose instruction j follows instruction i in the program order. Executing instruction j before the effect of instruction i has taken place can cause a

| RAW hazard if | $R(i) \cap D(j) \neq \emptyset$ |

|---------------|---------------------------------|

| WAR hazard if | $D(i) \cap R(j) \neq \emptyset$ |

| WAW hazard if | $R(i) \cap R(j) \neq \emptyset$ |

### Register vs. Memory Data Dependences

- Data hazards due to register operands can be determined at the decode stage *but*

- Data hazards due to memory operands can be determined only after computing the effective address

| store | $M[(a1) + offset1] \leftarrow (a2)$ |

|-------|-------------------------------------|

| load  | $a3 \leftarrow M[(a4) + offset2]$   |

Does(a1) + offset1 == (a4) + offset2?

In lecture 10, we'll see how to handle memory dependencies For now, we focus only on register dependencies

### Data Hazards: An Example

RAW Hazards WAR Hazards WAW Hazards

MIT 6.5900 Fall 2023

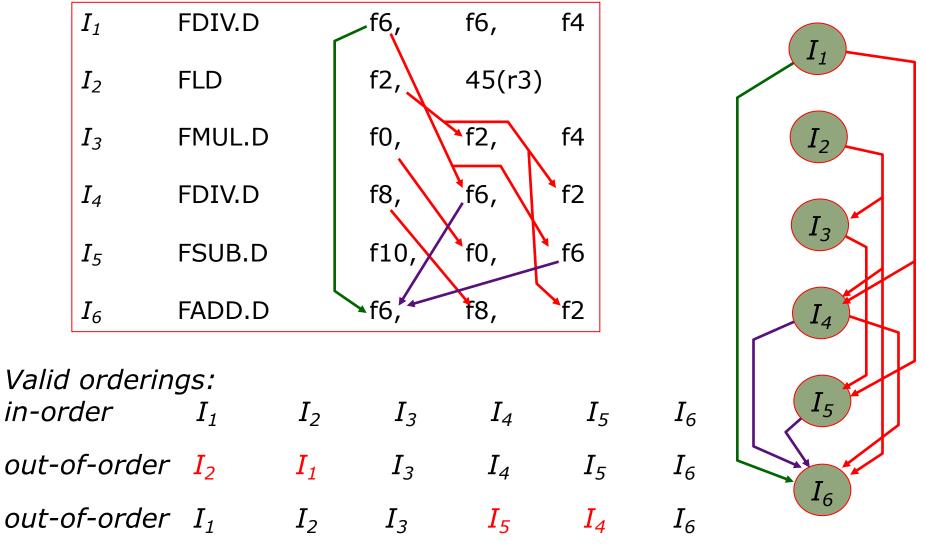

### **Instruction Scheduling**

September 25, 2023

MIT 6.5900 Fall 2023

# Out-of-order Completion

| T                                  |              |   |   | £        | C    |          | £C                         |          | £٨ |          |          |        | La       | ten | су       |          |

|------------------------------------|--------------|---|---|----------|------|----------|----------------------------|----------|----|----------|----------|--------|----------|-----|----------|----------|

| $I_1$                              | FDIV.D       |   |   | I        | 6,   |          | f6,                        |          | f4 |          |          |        |          | 4   |          |          |

| $I_2$                              | FLD          |   |   | f        | 2,   |          | 45(                        | r3)      |    |          |          |        |          | 1   |          |          |

| $I_3$                              | FMUL.C       | ) |   | f        | 0,   |          | f2,                        |          | f4 |          |          |        |          | 3   |          |          |

| $I_{\mathcal{A}}$                  | FDIV.D       |   |   | f        | 8,   |          | f6,                        |          | f2 |          |          |        |          | 4   |          |          |

| $I_5$                              | FSUB.D       |   |   | f        | f10, |          | f0,                        |          | f6 | 5 1      |          |        |          |     |          |          |

| $I_6$                              | FADD.D       | ) |   | f        | 6,   |          | f8,                        |          | f2 |          |          |        |          | 1   |          |          |

| cycle                              |              | 1 | 2 | 3        | 4    | 5        | 6                          | 7        | 8  | 9        | 10       | 11     | 12       | 13  | 14       | 15       |

| in-order comp                      |              | 1 | 2 |          |      | <u>1</u> | <u>2</u>                   | 3        | 4  |          | <u>3</u> | 5      | <u>4</u> | 6   | <u>5</u> | <u>6</u> |

| out-of-order co                    | тр           | 1 | 2 | <u>2</u> | 3    | <u>1</u> | 4                          | <u>3</u> | 5  | <u>5</u> | <u>4</u> | 6      | <u>6</u> |     |          |          |

| What problems can out-of-order cor |              |   |   |          |      |          | caus                       | e?       |    |          | ta h     |        |          |     | ds       |          |

| September 25, 2023                 | 25, 2023 MIT |   |   |          |      |          | all 2023 <i>Exceptions</i> |          |    |          |          | L06-23 |          |     |          |          |

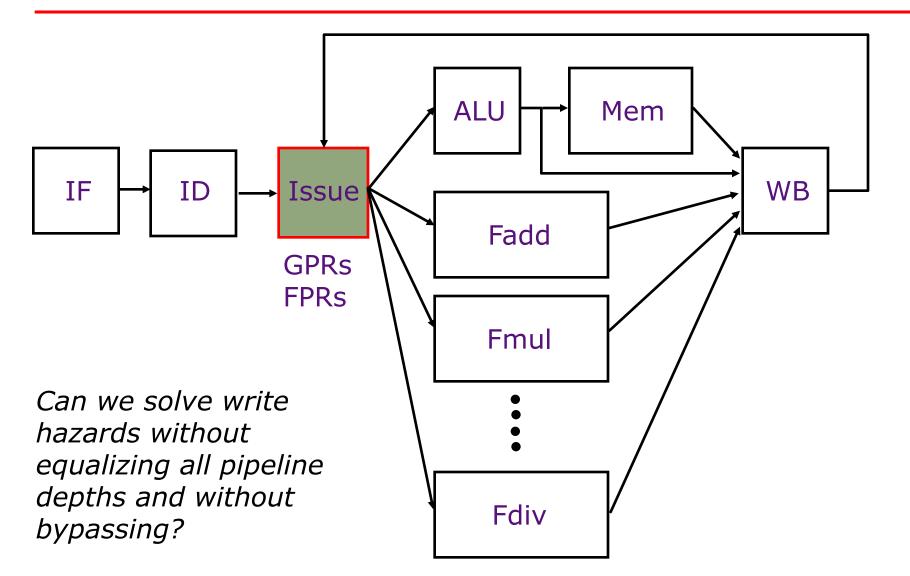

### Scoreboard: A Hardware Data Structure to Detect Hazards Dynamically

### **Complex Pipeline**

### When is it Safe to Issue an Instruction?

- Approach: Stall issue until sure that issuing will cause no dependence problems...

- Suppose a data structure keeps track of all the instructions in all the functional units

- The following checks need to be made before the Issue stage can dispatch an instruction

- Is the required function unit available?

- Is the input data available?  $\Rightarrow$  RAW?

- Is it safe to write the destination?  $\Rightarrow$  WAR? WAW?

- Is there a structural conflict at the WB stage?

### A Data Structure for Correct Issues Keeps track of the status of Functional Units

| Name  | Busy | Ор | Dest | Src1 | Src2 |

|-------|------|----|------|------|------|

| Int   |      |    |      |      |      |

| Mem   |      |    |      |      |      |

| Add1  |      |    |      |      |      |

| Add2  |      |    |      |      |      |

| Add3  |      |    |      |      |      |

| Mult1 |      |    |      |      |      |

| Mult2 |      |    |      |      |      |

| Div   |      |    |      |      |      |

The instruction i at the Issue stage consults this table

| FU available? | check the busy column                         |

|---------------|-----------------------------------------------|

| RAW?          | search the dest column for i's sources        |

| WAR?          | search the source columns for i's destination |

| WAW?          | search the dest column for i's destination    |

An entry is added to the table if no hazard is detected; An entry is removed from the table after Write-Back September 25, 2023 MIT 6.5900 Fall 2023 L06-27

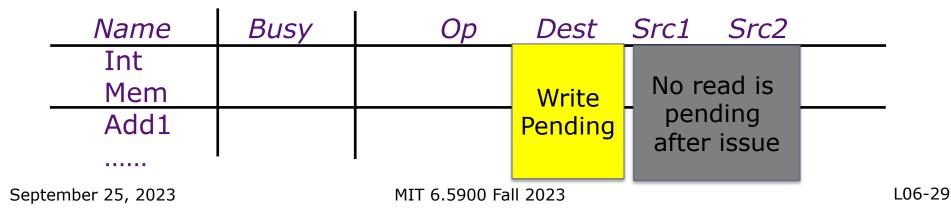

### Simplifying the Data Structure Assuming In-order Issue

- Suppose the instruction is not dispatched by the Issue stage

- If a RAW hazard exists

- or if the required FU is busy

- Suppose operands are latched by the functional unit on issue

- Can the dispatched instruction cause a

WAR hazard? NO: Operands read at issue WAW hazard? YES: Out-of-order completion

| _     | Name          | Busy | Ор            | Dest    | Src1  | Src2   |        |

|-------|---------------|------|---------------|---------|-------|--------|--------|

|       | Int           |      |               |         |       |        |        |

| _     | Mem           |      |               | Write   |       | ead is |        |

| _     | Add1          |      |               | Pending | pen   | ding   |        |

|       |               |      |               |         | after | issue  |        |

| Septe | mber 25, 2023 |      | MIT 6.5900 Fa | L 2023  |       |        | L06-28 |

# Simplifying the Data Structure

- No WAR hazard

⇒ no need to keep src1 and src2

- The Issue stage does not dispatch an instruction in case of a WAW hazard

⇒ a register name can occur at most once in the *dest* column

Can be encoded as a bit vector

### Scoreboard for In-order Issues

Busy[FU#] : a bit-vector to indicate FU's availability. (FU = Int, Add, Mult, Div) These bits are hardwired to FU's.

Issue checks the instruction (opcode dest src1 src2) against the scoreboard (Busy & WP) to dispatch

FU available? RAW? WAR? WAW?

Busy[FU#] WP[src1] or WP[src2] cannot arise WP[dest]

### **Scoreboard Dynamics**

| Issue<br>time                                | Functional Unit Status<br>Int(1) Add(1) Mult(3) Div(4) WB |     |    |            |    |            |            |        |            |           | Registers Reserved WB<br>for Writes |

|----------------------------------------------|-----------------------------------------------------------|-----|----|------------|----|------------|------------|--------|------------|-----------|-------------------------------------|

| t0 <i>I</i> 1                                |                                                           |     |    |            |    | f6         |            |        |            |           | f6                                  |

| t1 <i>I</i> <sub>2</sub>                     | f2                                                        |     |    |            |    |            | f6         |        |            |           | <mark>f6</mark> , f2                |

| t2                                           |                                                           |     |    |            |    |            |            | f6     |            | f2        | f6, f2 <u>I</u> 2                   |

| t3 <i>I</i> 3                                |                                                           |     | fO |            |    |            |            |        | <b>f6</b>  |           | <mark>f6</mark> , f0                |

| t4                                           |                                                           |     |    | f0         |    |            |            |        |            | f6        | f6, f0 <u>I</u> 1                   |

| t5 <u>I</u> 4                                |                                                           |     |    |            | fO | <b>f</b> 8 |            |        |            |           | f0, <mark>f8</mark>                 |

| t6                                           |                                                           |     |    |            |    |            | f8         |        |            | fO        | f0, f8 <u>I</u> 3                   |

| t7 <i>I</i> 5                                |                                                           | f10 |    |            |    |            |            | f8     |            |           | <mark>f8</mark> , f10               |

| t8                                           |                                                           |     |    |            |    |            |            |        | <b>f</b> 8 | f10       | f8, f10 <u>I</u> 5                  |

| t9                                           |                                                           |     |    |            |    |            |            |        |            | f8        | f8 <u>I</u> 4                       |

| t10 <i>I</i> 6                               |                                                           | f6  |    |            |    |            |            |        |            |           | f6                                  |

| t11                                          |                                                           |     |    |            |    |            |            |        |            | <b>f6</b> | f6 <u>I</u> 6                       |

| $egin{array}{c} I_1 \ I_2 \end{array}$       | FDIV.                                                     | D   |    | f6,        |    |            | f6,        |        |            | f4        |                                     |

| $I_2$                                        | FLD                                                       |     |    | f2,        |    |            | 45         | -      | -          | £٨        | Check Busy[Fu#]                     |

| $I_3$<br>$I_4$                               | FMUL<br>FDIV                                              |     |    | f0,<br>f8, |    |            | f2,<br>f6, |        |            | f4<br>f2  | Check WP[src1, src2]                |

| $I_{5}$                                      | FSUE                                                      |     |    | f10        |    |            | f0,        |        |            | f6        | Check WP[dest]                      |

| $I_6$                                        | FADD                                                      | D.D |    | f6,        | -  |            | f8,        |        |            | f2        |                                     |

| September 25, 2023      MIT 6.5900 Fall 2023 |                                                           |     |    |            |    |            | 2023       | L06-31 |            |           |                                     |

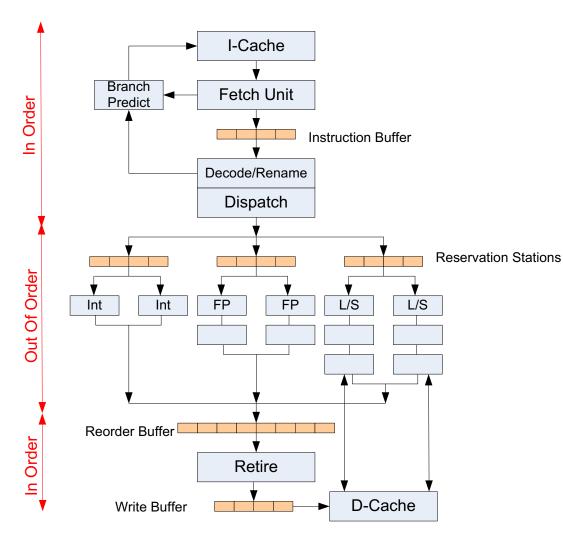

### Preview: Anatomy of a Modern Outof-Order Superscalar Core

- L06 (Today): Complex pipes w/ in-order issue

- L07: Out-of-order exec & renaming

- L08: Branch prediction

- L09: Speculative execution and recovery

- L10: Advanced Memory Ops