## 6.823 SPring15 Quiz 2 Review (L09-L14)

TA: Po-An Tsai, Hsin-Jung Yang

### Lecture 9-14 are all about ILP

- Instruction-level parallelism (ILP)

- Execute as many instructions as possible at the same time to maximize throughput and hide long latency by memory/ALU

- Why this is not easy?

- Dependencies between instructions

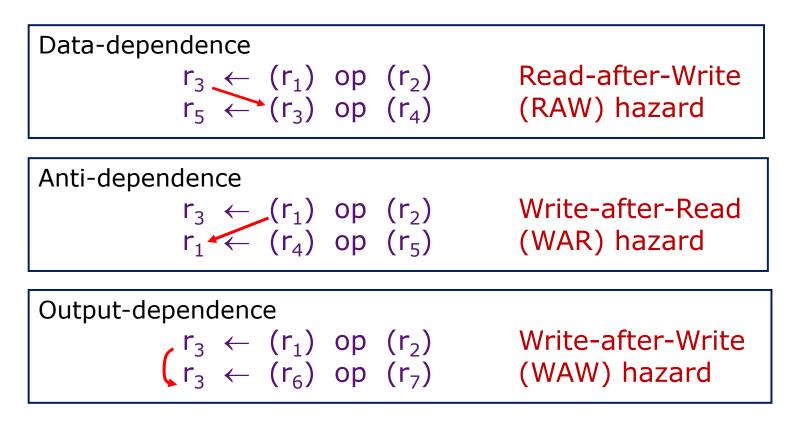

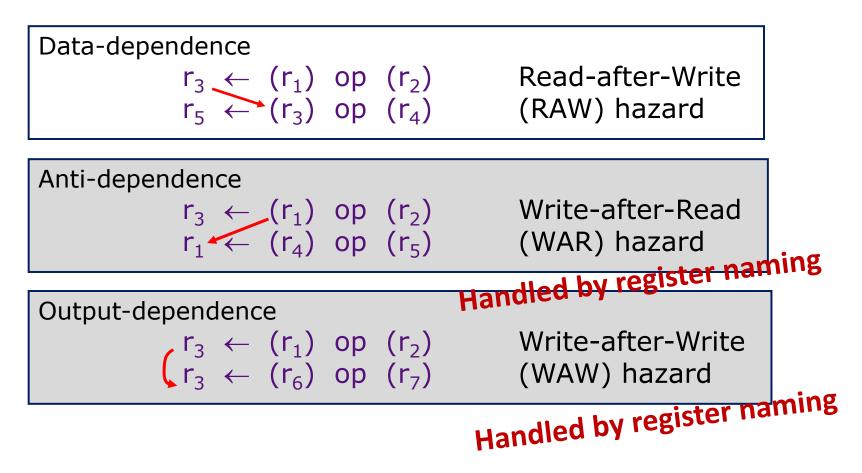

## Dependency

• Data dependency

- RAW WAR WAW

Control dependency

Branch jump

Structural dependency

Only one ALU

## **Ways to Solve Dependency**

- For false dependency

- Indirection

- For true dependency

- Stall

- Bypass

- Speculate => best if you speculate mostly correctly

## **Ways to Solve Dependency**

- Data dependency

- RAW WAR WAW

- => Scoreboard (L9) ROB, Register renaming (L10), Store queue(L13)

- Control dependency

- Branch jump

- => Branch prediction (L11)

- Structural dependency

- Only one ALU

- => Superscalar (L9)

### **Speculation**

- We speculate a lot!

- Branch

- No exceptions

- Addresses for load/store are not the same

How to manage old and new values?

– Greedy/lazy (L12)

### **Mis-speculation**

- Recovery according to your policy(L12)

- Snapshot

- Rollback

## **Hide Long Latency**

- A cache miss takes 100 cycles

- A divide takes 20 cycles

Execute following instructions, but hold them until those long-latency instruction finish.

Use Little's law to calculate how many instruction in flight

## **Hide Long Latency**

- A cache miss takes 100 cycles

- A divide takes 20 cycles

- Switch to another independent thread until they finish (L14)

Use Little's law to calculate how many threads needed

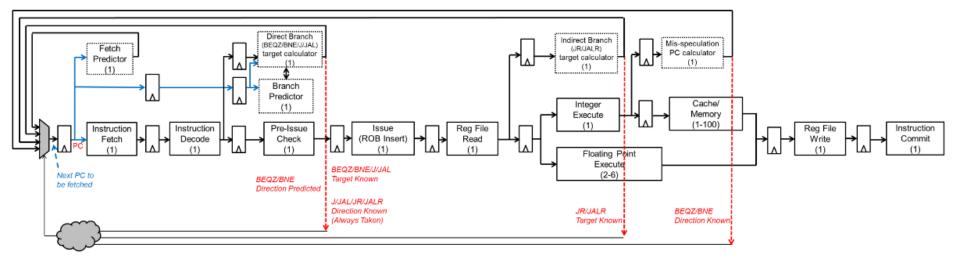

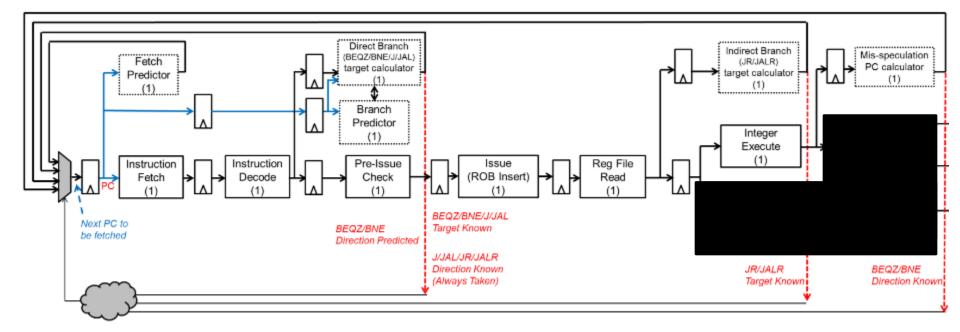

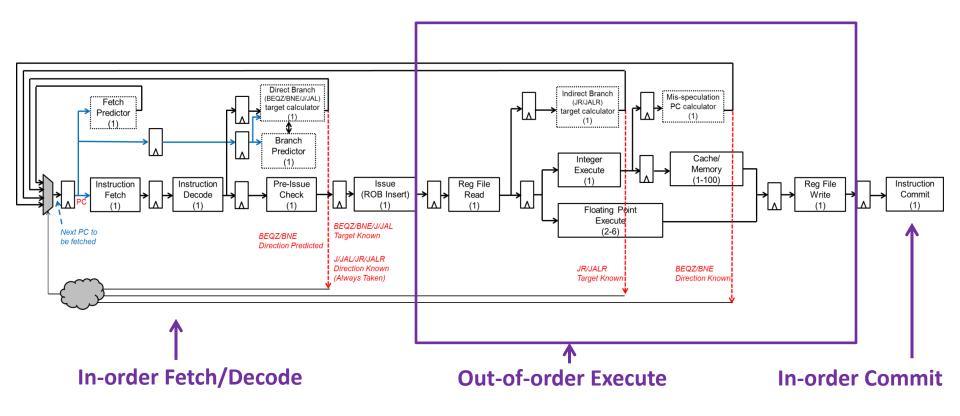

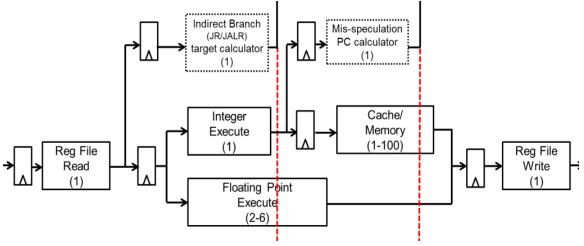

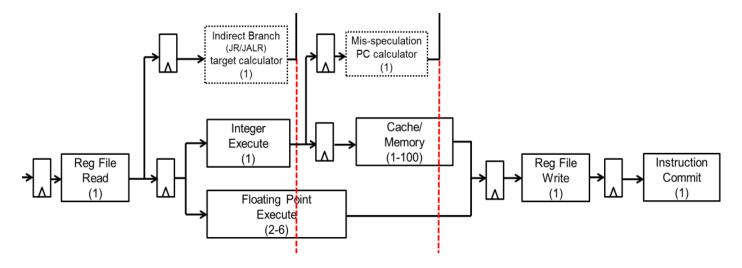

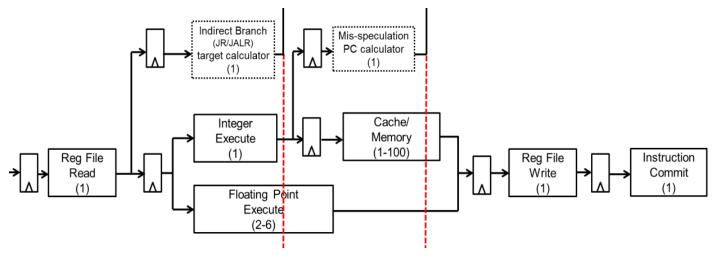

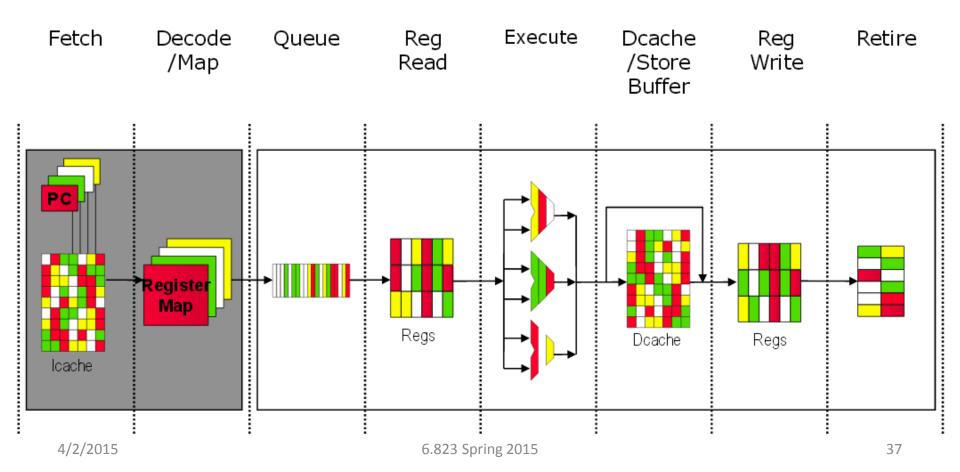

### **Example OoO Pipeline**

Figure 1: Out-of-order Pipeline

### **Branch Prediction**

#### Figure 1: Out-of-order Pipeline

## **Branch Prediction**

- Speculate what the next instruction is

- Static

- 1 bit predictor

- 2 bit predictor

- Global history (a history register and lots of predictor)

- Local history (many history registers and lots of predictor)

- Combined local and global history

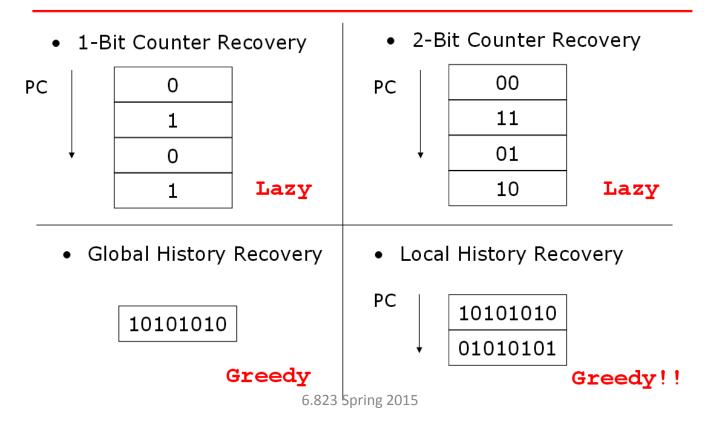

## **Branch Prediction**

- Data management

- **Branch Predictor Recovery**

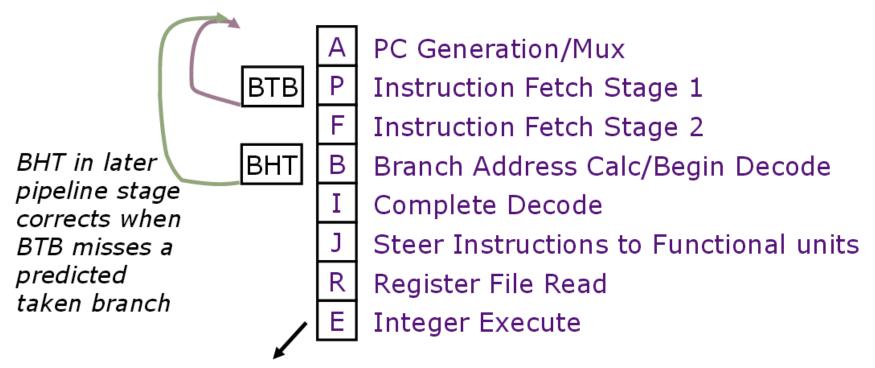

## **Branch Target Buffer**

Store the next PC of branch/jmp instructions seen last time

• Get address earlier than predictor

## Combine BTB and Predictor(BHT)

BTB/BHT only updated after branch resolves in E stage

When can we execute an instruction out-of-order? **Need to consider data dependency** (register dependency, memory dependency)

6.823 Spring 2015

• Register Dependency

• Register Dependency

Memory Dependency

st r1, 4(r2) ld r3, 8(r4)

When is the load dependent on the store?

When (r2 + 4) == (r4 + 8)

Do we know this issue when the instruction is decoded? No

Memory Dependency

st r1, 4(r2) ld r3, 8(r4)

### Solution:

- (1) **Stall:** can execute load before store only if the addresses are known to be different

- (2) Address speculation: guess r2+4 != r4+8 and execute load before store

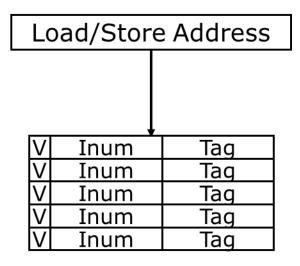

### **Speculative Load Buffer**

### Speculative Load Buffer

#### Speculation check:

Detect if a load has executed before an earlier store to the same address – missed RAW hazard

On load execute: mark entry valid, instruction number and tag On load commit: clear valid bit On load abort: clear valid bit On store execute: if tag matches and the instruction is younger than the store -> Abort!

### • When do we do speculation?

- Branch prediction

- Assume no exceptions/interrupts

- Assume no memory dependency

- ...

- How do we manage speculative data?

- Greedy (or Eager) Update

- Update the value in place

- Maintain a log of old values to use for recovery

- Lazy Update

- Buffer the new value and leave the old value in place

- Replace the old value only at 'commit' time

### • Type of speculative data

### Branch prediction

• history registers, prediction counters (see P.13)

### Register values

- Lazy update: store new values in the ROB and update registers during commit

- Hybrid: store both new and old values in the unified physical register file

#### Store values to memory

Laze update: store new values in the speculative store buffer and write to non-speculative store buffer/cache/memory during commit

### • Register Value Management

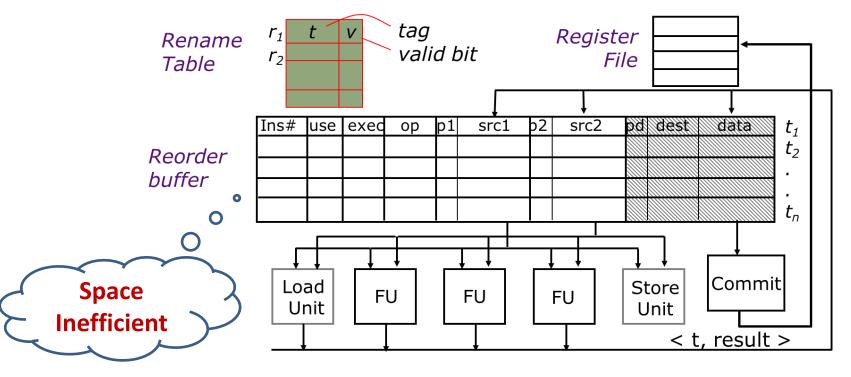

Approach 1: store new values in the ROB and update registers during commit

### Register Value Management

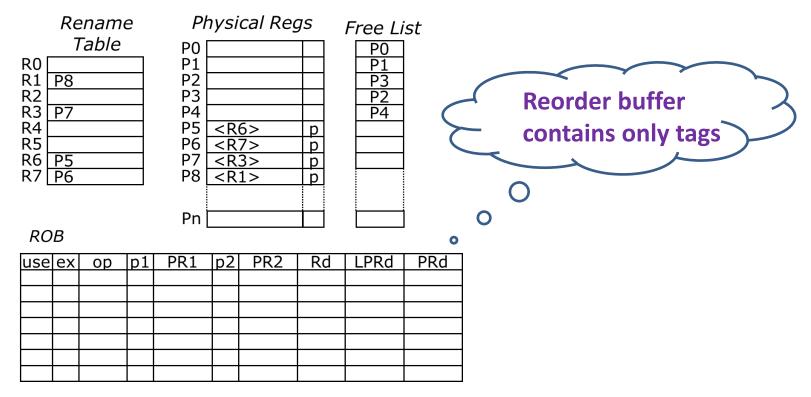

- Approach 2: keep all data values in a physical register file

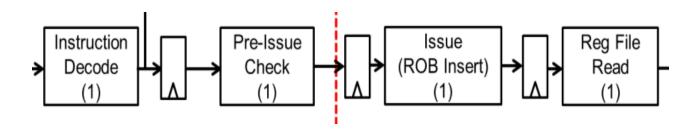

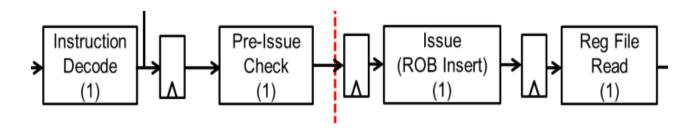

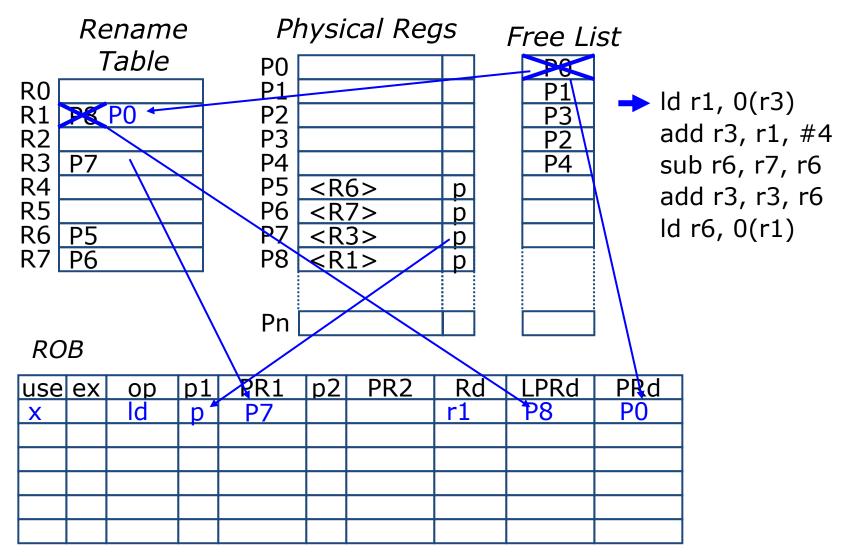

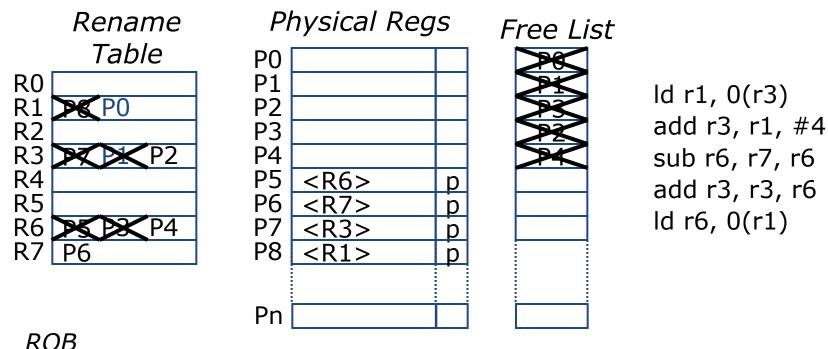

### **Pre-Issue Check:**

- The ROB is checked for available slots

- The free list is checked for free rename registers (if necessary)

- For store instructions, the non-speculative store buffer is checked for available slots

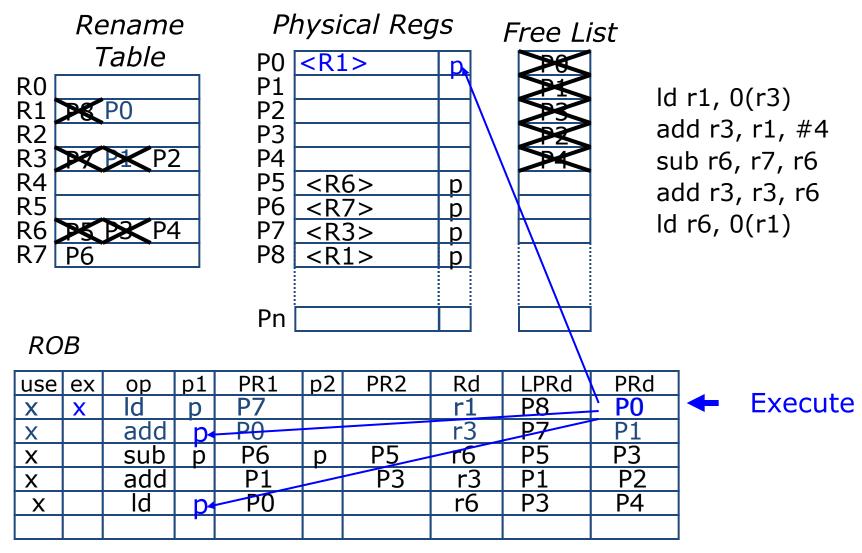

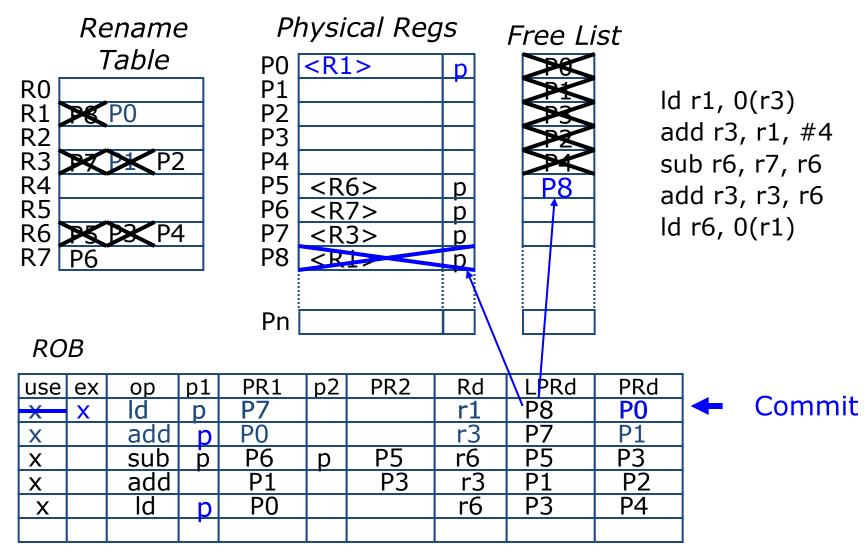

### **ROB Insert:**

- The instruction is inserted into the ROB only if all the checks in the previous cycle (Pre-Issue check) pass

- The destination register is renamed

|     |    |     |    |     |    |     |    |      |     | , |

|-----|----|-----|----|-----|----|-----|----|------|-----|---|

| use | ex | ор  | p1 | PR1 | p2 | PR2 | Rd | LPRd | PRd |   |

| X   |    | ld  | р  | P7  |    |     | r1 | P8   | P0  |   |

| X   |    | add |    | P0  |    |     | r3 | P7   | P1  |   |

| X   |    | sub | р  | P6  | p  | P5  | r6 | P5   | P3  |   |

| X   |    | add |    | P1  |    | P3  | r3 | P1   | P2  |   |

| X   |    | ld  |    | P0  |    |     | r6 | P3   | P4  |   |

|     |    |     |    |     |    |     |    |      |     |   |

#### eady to execute

### **Reg File Read:**

- Operand values are read from the unified physical register file

### **Execute:**

- Integer and floating point operations are sent to the appropriate functional units

- Stores enter the speculative store buffer

- Loads read from the store buffer or cache/memory

### **Reg File Write:**

The output from the functional units/memory is written into the unified register file and the ROB is notified.

### Commit:

- Instructions are committed in-order

- Free the previously mapped physical register

- Data is written to cache/memory/non-speculative store buffer when a store is committed

- The ROB entry is freed after commit

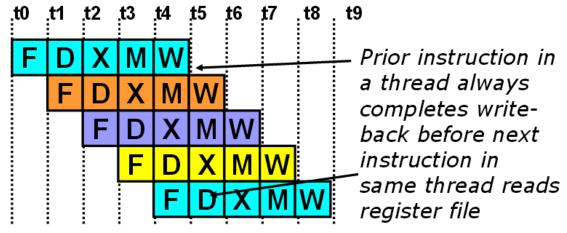

## **Multithreading**

How can we guarantee no dependencies between instructions in a pipeline?

# Take instructions from different programs

Interleave 4 threads, T1-T4, on non-bypassed 5-stage pipe

T1: LW r1, 0(r2) T2: ADD r7, r1, r4 T3: XORI r5, r4, #12 T4: SW 0(r7), r5 T1: LW r5, 12(r1)

## **Scheduling Policy**

- Fine-grained multithreading

- Context switch among threads every cycle

- Coarse-grained multithreading

- Context switch among threads every few cycles, e.g., on:

- Function unit data hazard,

- L1 miss,

- L2 miss...

## Simultaneous Multithreading (SMT)

• Share OOO structures between threads

### The end

### Good luck!! 🙂