# 6.823 Computer System Architecture Prerequisite Self-Assessment Test

Assigned Feb 4, 2015

Due Feb 9, 2015

http://csg.csail.mit.edu/6.823/

This self-assessment test is intended to help you determine your level of preparation for 6.823 by going through some of the background material we expect you to have seen already. We also hope working through the problem set will help refresh your memory on these topics. We will only have a short review of this material in 6.823.

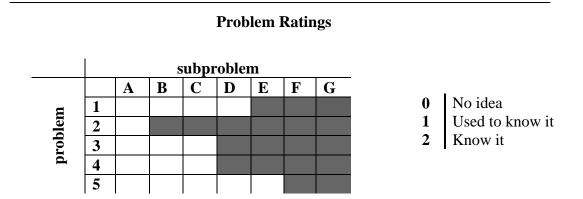

For each question, we ask that you fill out the table at the end of the problem set handout indicating your level of confidence with each assigned problem and hand this in with your solutions. If you have never seen the material before, then please enter "0". If you have seen the material, and think you should know it, but can't answer the question without spending time studying your old notes, then please enter "1". If you are very comfortable with the material, then enter "2". You should turn in solutions for problems where you entered "1" and "2", but do not have to turn in solutions for problems for which you entered a "0".

If you have more than 6 or 7 "0"s in the table, or feel uncomfortable with your background preparation or our expectations for the course, then you should arrange a meeting with a lecturer to discuss your particular situation before the third week of class. Our experience is that most students with some background in logic design or assembly-level computer programming can complete the course successfully.

For this test only, you must work individually and turn in your own solutions. Do not discuss the problems with others.

#### Problem 1

Construct the following logic functions using only two-input NAND gates (please use hierarchy where possible to simplify your designs):

a) inverterb) two-input XOR gatec) 2-to-1 multiplexerd) 2-to-4 decoder

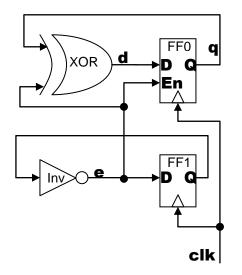

The questions below refer to the following circuit and its associated timing parameters. The flip-flops are positive-edge triggered, and FF0 has an enable input (Q only changes if En is high). Assume that all timing parameters are positive.

Fill out the state transition diagram for the sequential logic drawn above.

| FF0 | FF1 | FF0' | FF1' |

|-----|-----|------|------|

|     |     |      |      |

|     |     |      |      |

|     |     |      |      |

|     |     |      |      |

The followings are two code segments written in MIPS64 assembly language:

| Segm  | ent A: |              |                                  |

|-------|--------|--------------|----------------------------------|

| Loop: | LD     | r5, 0(r1)    | # r5 ← Mem[r1+0]                 |

|       | LD     | r6, 0(r2)    | # r6 ← Mem[r2+0]                 |

|       | DADD   | r5, r5, r6   | # r5 ← r5 + r6                   |

|       | SD     | r5, 0(r3)    | # Mem[r3+0] ← r5                 |

|       | LD     | r5, 0(r1)    | # r5 ← Mem[r1+0]                 |

|       | LD     | r6, 0(r2)    | # r6 ← Mem[r2+0]                 |

|       | DSUB   | r5, r5, r6   | # r5 ← r5 - r6                   |

|       | SD     | r5, 0(r4)    | # Mem[r4+0] ← r5                 |

|       | DADDUI | r1, r1, 8    | # r1 ← r1 + 8                    |

|       | DADDUI | r2, r2, 8    | # r2 ← r2 + 8                    |

|       | DADDUI | r3, r3, 8    | # r3 ← r3 + 8                    |

|       | DADDUI | r4, r4, 8    | # r4 ← r4 + 8                    |

|       | BNE    | r1, r9, Loop | # branch to Loop if $r1 \neq r9$ |

| Segme | ent B: |              |                                  |

| Loop: | LD     | r5, 0(r1)    | # r5 ← Mem[r1+0]                 |

|       | LD     | r6, 0(r2)    | # r6 ← Mem[r2+0]                 |

|       | DADD   | r7, r5, r6   | # r7 ← r5 + r6                   |

|       | DSUB   | r8, r5, r6   | # r8 ← r5 - r6                   |

|       | SD     | r7, 0(r3)    | # Mem[r3+0] ← r7                 |

|       | SD     | r8, 0(r4)    | # Mem[r4+0] ← r8                 |

|       | DADDUI | r1, r1, 8    | # r1 ← r1 + 8                    |

|       | DADDUI | r2, r2, 8    | # r2 ← r2 + 8                    |

|       | DADDUI | r3, r3, 8    | # r3 ← r3 + 8                    |

|       | DADDUI | r4, r4, 8    | # r4 ← r4 + 8                    |

|       | BNE    | r1, r9, Loop | # branch to Loop if $r1 \neq r9$ |

In both segments, assume r1, r2, r3, r4 initially hold valid memory addresses. Register r9 is pre-computed to be 80 larger than the initial value of r1. All instructions operate on 64bit doubleword values and the memory address space is byte-addressable.

- a) If both segments are expected to perform the same task, can you guess what the task is? You can write the answer in C-like pseudo code.

- b) In general, which segment do you expect to perform better when executed?

- c) Do the two segments always produce the same results in all situations? If not, can you specify a situation which makes them behave differently?

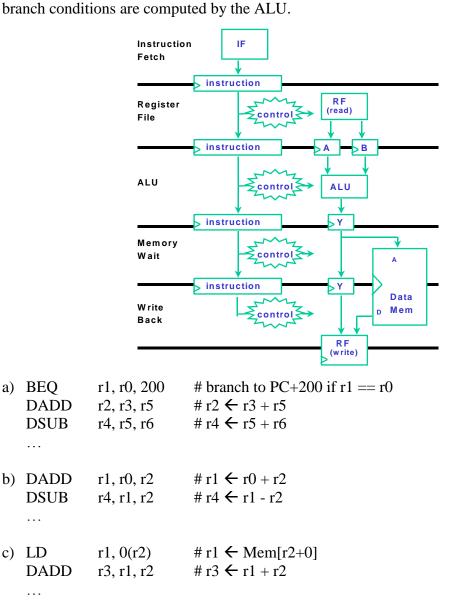

The following figure shows a 5-stage pipelined processor. The pipelined processor should always compute the same results as an unpipelined processor. Answer the following questions for each of the instruction sequences below:

- Why does the sequence require special handling (what could go wrong)?

- What are the minimal hardware mechanisms required to ensure correct behavior?

- What additional hardware mechanisms, if any, could help preserve performance? Assume that the architecture does not have any branch delay slots, and assume that

Describe the operation of a data cache. Your description should include discussion of the following:

- a) Spatial and temporal locality.

- b) Valid bits.

- c) Direct mapped versus set-associative structures. Show how cache indexing and tag match works for both direct mapped and 2-way set-associative cache configurations assuming one word per cache line. What are the advantages and disadvantages of direct mapped versus set-associative structures?

- d) Multiple-word cache lines. What are the advantages and disadvantages of multipleword cache lines? Describe how they are implemented for a direct mapped cache.

- e) LRU and random replacement policies. What are their relative advantages and disadvantages?