# Microcoding, VLIW and Vector Computers

Suvinay Subramanian

6.823 Spring 2016

#### Microcoding

- » Abstraction layer between hardware and architecture of computer

- i.e. separates ISA from actual hardware implementation details.

- » Layer of hardware-level instructions that implement higher-level (i.e. ISA) instructions

## Benefits of Microcoding

- » Originally developed as a simpler method for developing control logic

- Direct combinational logic for powerful instruction set can be complex, prone to bugs/difficult to debug

- Multi-step addressing modes, varied length instructions etc.

- » Enables complex ISAs

- Reduced instruction fetch bandwidth; smaller code footprint

- » Same ISA, different implementations

- Flexibility in how data paths, micro-arch. blocks designed

- IBM 360: Model 30, Model 40 etc.

- » Allows for "patching" in the field

- » New instructions supported without modifying datapath

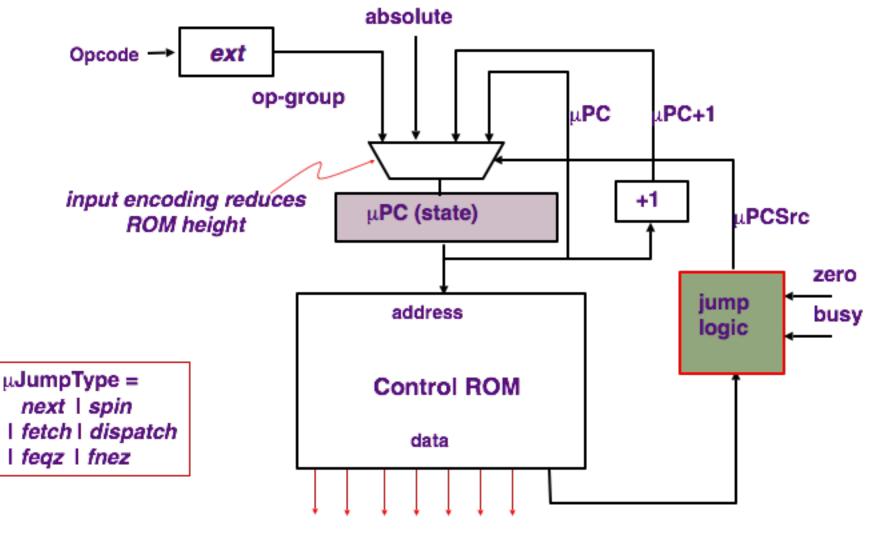

#### Microcode Implementation

Control Signals (17)

#### Microcode Fragments

| State                                                        | Control points                                  | next-state            |

|--------------------------------------------------------------|-------------------------------------------------|-----------------------|

| fetch <sub>0</sub>                                           | $MA \leftarrow PC$                              | next                  |

| fetch <sub>1</sub>                                           | $IR \leftarrow Memory$                          | spin                  |

| fetch <sub>2</sub>                                           | $A \leftarrow PC$                               | next                  |

| fetch <sub>3</sub>                                           | $PC \leftarrow A + 4$                           | dispatch              |

| <br>ALU <sub>0</sub><br>ALU <sub>1</sub><br>ALU <sub>2</sub> | A ← Reg[rs]<br>B ← Reg[rt]<br>Reg[rd]←func(A,B) | next<br>next<br>fetch |

| ALUi <sub>0</sub>                                            | A ← Reg[rs]                                     | next                  |

| ALUi <sub>1</sub>                                            | B ← sExt <sub>16</sub> (Imm)                    | next                  |

| ALUi <sub>2</sub>                                            | Reg[rd]← Op(A,B)                                | fetch                 |

#### VLIW

» Premise: Static instruction scheduling + superscalar execution to extract ILP.

- » Tradeoff: Complex hardware vs Complex compiler "Conservation of complexity"

- OoO processors do dynamic scheduling

Figure out independent instructions on-the-fly

- VLIW machines: Compilers figure out independent instructions and schedules them suitably

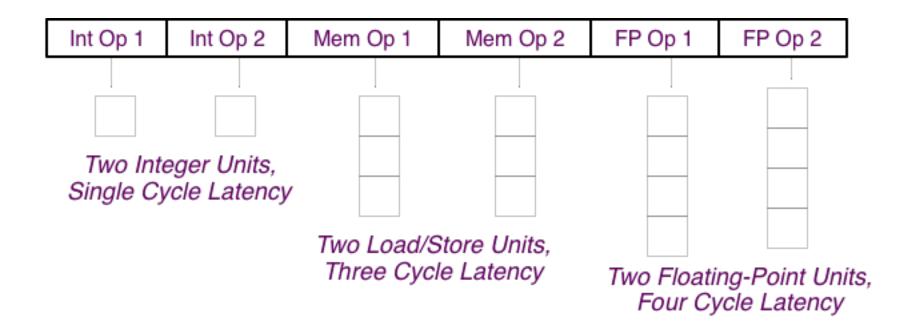

#### VLIW Hardware

- Multiple operations packed into one instruction

- Each operation slot is for a fixed function

- Constant operation latencies are specified

#### VLIW Software

- » Key Questions:

- How do we find independent instructions to fetch/execute?

- How to enable more compiler optimizations?

- » Key Ideas:

- Get rid of control flow

- Predicated execution, loop unrolling

- Optimize frequently executed code-paths

- Trace scheduling

- Others: Software pipelining, speculative execution

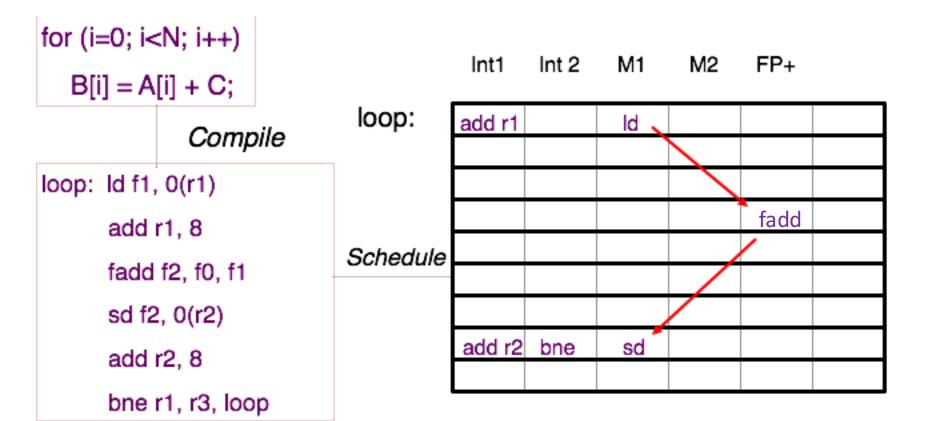

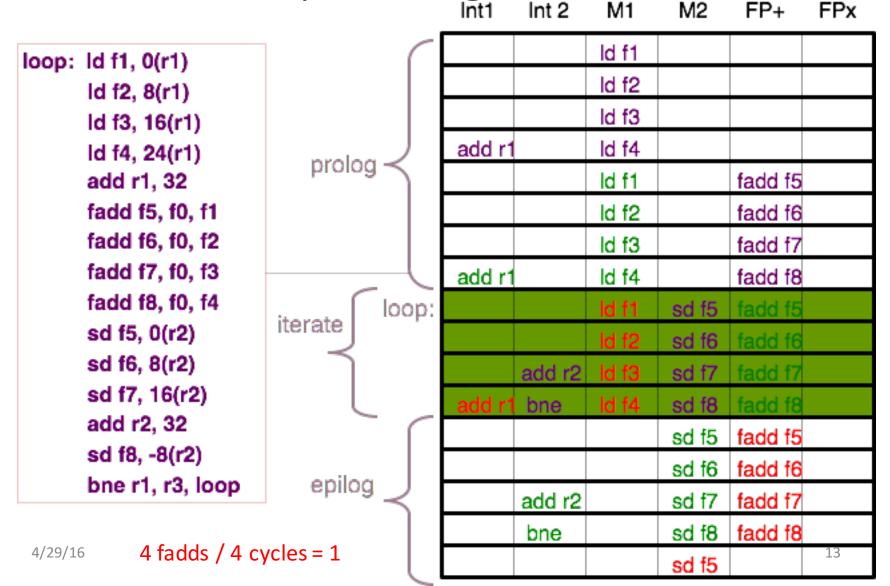

How many FP ops/cycle?

```

1 fadd / 8 cycles = 0.125

```

9

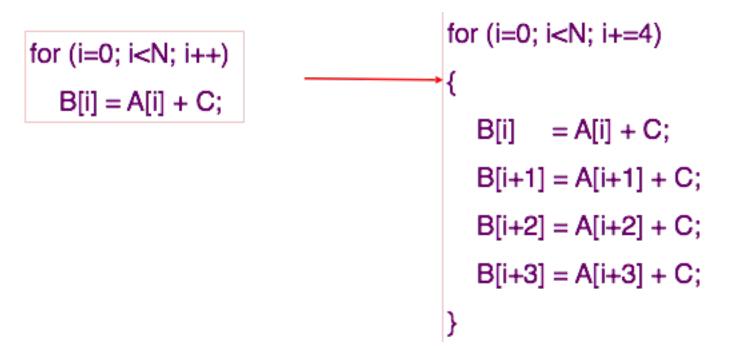

» Unroll loop to perform M iterations at once

- Get more independent instructions

- Need to be careful about case where M is not a multiple of number of loop iterations

|                                |          | Inti   | Int 2 | M1    | M2 | FP+     | FРX |

|--------------------------------|----------|--------|-------|-------|----|---------|-----|

| loop: ld f1, 0(r1)             |          |        |       |       |    |         |     |

| ld f2, 8(r1)                   | loop:    |        |       | ld f1 |    |         |     |

| ld f3, 16(r1)                  |          |        |       | ld f2 |    |         |     |

| ld f4, 24(r1)                  |          |        |       | ld f3 |    |         |     |

| add r1, 32                     |          | add r1 |       | ld f4 |    | fadd f5 |     |

| fadd f5, f0, f1                | Schedule |        |       |       |    | fadd f6 |     |

| fadd f6, f0, f2                | Schedule |        |       |       |    | fadd f7 |     |

| fadd f7, f0, f3                |          |        |       |       | /  | fadd f8 |     |

| fadd f8, f0, f4                |          |        |       | sd f5 |    |         |     |

| sd f5, 0(r2)                   |          |        |       | sd f6 |    |         |     |

| sd f6, 8(r2)                   |          |        |       | sd f7 |    |         |     |

| sd f7, 16(r2)                  |          | add r2 | bne   | sd f8 |    |         |     |

| sd f8, 24(r2)                  |          |        |       |       |    |         |     |

| add r2, 32<br>bne r1, r3, loop |          |        |       |       |    |         |     |

Int1

Int O

114

140

ED.

4 fadds / 11 cycles = 0.36

EDv

- 1. Combine M iterations of loop

- 2. Pipeline schedule to reduce RAW stalls

- In the example above, notice that we move (re-order) loads to the top

- 3. Rename registers

- f1, f2, f3, f4

## Software Pipelining

#### Loop Unrolling Limitations

» Code growth

» Does not handle inter-iteration dependences well

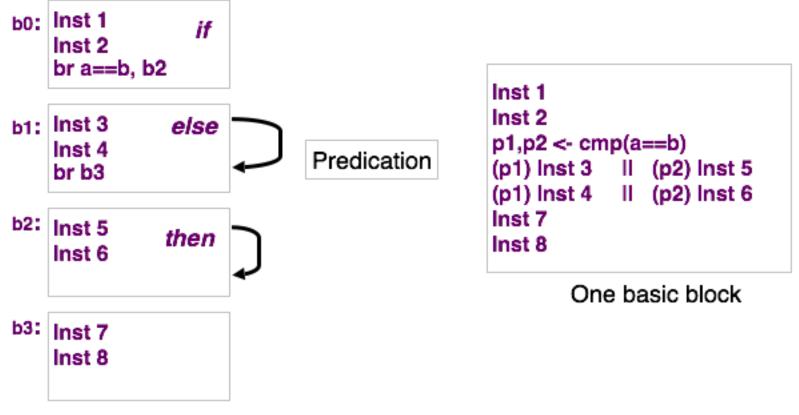

#### Predicated Execution

- » Limited ILP within a basic-block; branches limit available ILP

- » Idea: Eliminate hard-to-predict branches by converting control dependence to data dependence

- Each instruction (within the branch basic block) has a predicate bit set

- Only instructions with true predicates are executed and committed. Others are treated as nops.

#### **Predicated Execution**

Four basic blocks

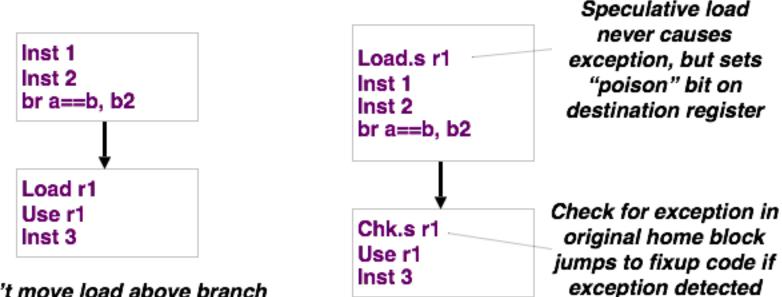

#### Speculative Execution

» Move instructions above branches to explore more ILP options

Can't move load above branch because might cause spurious exception

#### Speculative Execution

```

int32_t calculateSomething(int32_t *a, int32_t *b) {

int32_t result;

if (m_p > m_q + 1) {

result = a[*b];

} else {

result = defaultValue;

}

return result;

}

```

Speculative execute load of a[\*b] before branch condition is resolved. Say: m\_p, m\_q are bound checks.

1. What if m\_p < m\_q + 1? Say, b = nullptr.

Exception!</pre>

But exceptions can arise in other ways. What if a[\*b] is valid, but there

is a page-fault? Exception! Trap to OS routine.

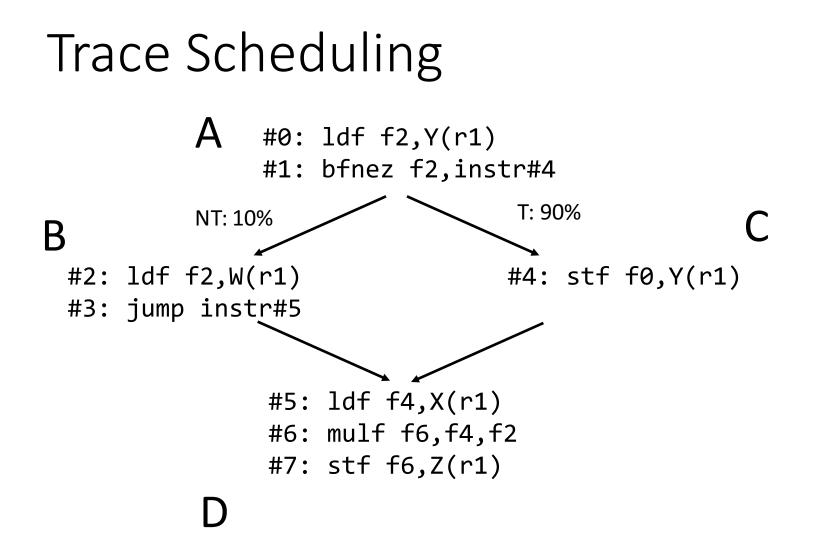

#### Trace Scheduling

» Idea: For non-loop situations:

- Find common path in program trace

- Re-align basic blocks to form straight-line trace

- Trace: Fused basic-block sequence

- Schedule trace

- Create fixup code in case trace != actual path

- Can be nasty

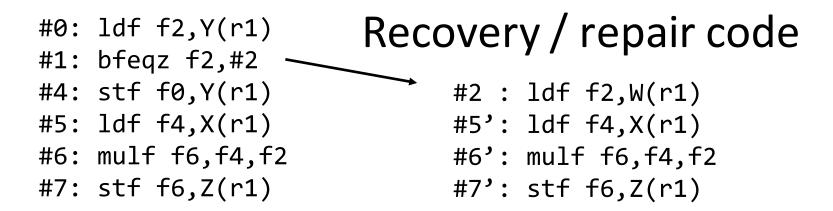

#### Trace Scheduling

A = Y[i] If (A == 0) A = W[i] Else: Y[i] = 0 Z[i] = A \* X[i]

- #0: ldf f2,Y(r1)

- #1: bfnez f2,instr#4

- #2: ldf f2,W(r1)

- #3: jump instr#5

- #4: stf f0,Y(r1)

- #5: ldf f4,X(r1)

- #6: mulf f6,f4,f2

- #7: stf f6,Z(r1)

#### Trace Scheduling

#### A, C, D superblock (trace)

#### » Trace scheduling can be combined with other techniques:

- What if we moved #5, #6 before #4? Speculative load issue

- What if we moved #5, #6 even further, above #1?

- What if branch was biased the other way?

- What if branch was evenly biased 50%, 50%? 4/29/16

Predication 22

#### VLIW Summary

- » Loop unrolling

- Reduces branch frequency

- Tighter packing of instructions

- Dependences b/w iterations; handling "extra" iterations

- » Predicated execution, speculative execution

- Control-flow

- Control-flow, Load-store speculation

- » Trace scheduling

- Recovery code

- Combined with other techniques above; moving code upward/downward may provide benefits

#### Vector Computers

» Idea: Operate on vectors instead of scalars

- ISA is more expressive, therefore captures more information

- » Advantages:

- No dependences within a vector

- Reduced instruction fetch bandwidth

- (Sometimes) regular memory access pattern

- No need to explicitly code loops

- » Pitfalls:

- Only works if code sequence (or parallelism) is regular

#### **Vector Computers**

To program a vector machine, the compiler or hand coder must make the data structures in the code fit nearly exactly the regular structure built into the hardware. That's hard to do in first place, and just as hard to change. One tweak, and the low-level code has to be rewritten by a very smart and dedicated programmer who knows the hardware and often the subtleties of the application area. Often the rewriting is unsuccessful; it's back to the drawing boards again. Many

#### Vector Computers

Terminology:

- » Vector length register (VLR)

- » Conditional execution using vector mask (VM)

- » Vector lanes

- » Vector chaining

#### 4/29/16

## That's all folks!