## 6.823 Computer System Architecture L-MIPS ISA and Single-Cycle Datapath

http://csg.csail.mit.edu/6.823/

Ben Bitdiddle is unhappy with the performance of the MIPS processor discussed in the 6.823 lecture. He wants to extend the MIPS ISA with a new class of instructions, LOAD-ALU (L), described in Table 1. He calls his new ISA the L-MIPS ISA.

|              | 31 26 25 21 20 16 15 11 10                                                                                                                                                                                                                                                                                                                                                                                                                             |      |    |    |    |     | 0 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|----|----|-----|---|

|              | орсо                                                                                                                                                                                                                                                                                                                                                                                                                                                   | de r | ſS | rt | rd | imm |   |

| Instruction  | Format and Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |    |    |    |     |   |

| Load and ALU | <ul> <li>ALUM rd, offset(base), rt<br/>rd ← Mem[(rs) + SignExt(imm)] op (rt)</li> <li>Performs an ALU operation with one register and one<br/>memory operand. The effective address of the first operand<br/>is computed by adding the contents of register <i>rs</i> (base) to<br/>the sign-extended 11-bit <i>immediate</i> field (offset). The second<br/>operand is the contents of register <i>rt</i>.</li> <li>eg: ADDM R1, 4(R3), R2</li> </ul> |      |    |    |    |     |   |

|              | XORM R1, -7(R1), R1                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |    |    |    |     |   |

Table 1. L-MIPS LOAD-ALU(L) instruction type.

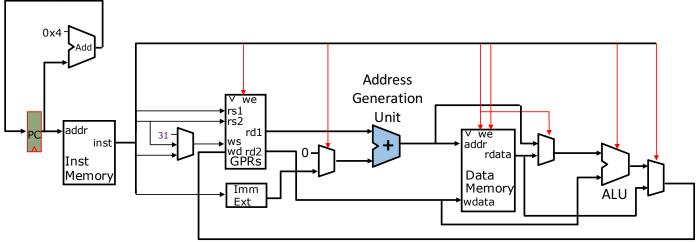

To implement the L-MIPS ISA, Ben modifies the datapath of the single-cycle MIPS processor as shown in Figure H-1. He adds an address generation unit, and moves the ALU unit after the data memory. Loads, stores and L-type instructions use the address generation unit before querying the memory, while other instructions use the ALU unit after the memory. Note that the address generation unit comprises only an adder.

Figure H-1: L-MIPS single-cycle datapath.