# **Problem M14.1: Microprogramming and Bus-Based Architectures**

In this problem, we explore microprogramming by writing microcode for the bus-based implementation of the MIPS machine described in Handout (Bus-Based MIPS Implementation). Read the instruction fetch microcode in Table H14-3 which has been reproduced at the end of this problem (Worksheet M14.1-1) for the readers' convenience. Make sure that you understand how different types of data and control transfers are achieved by setting the appropriate control signals before attempting this problem.

In order to further simplify this problem, ignore the busy signal and assume that the memory is as fast as the register file.

The final solution should be elegant and efficient (e.g. number of new states needed, amount of new hardware added).

Problem M14.1.A

Implementing Memory-to-Memory Add

For this problem, you are to implement a new memory-memory add operation. The new instruction has the following format.

## $ADDm r_d, r_s, r_t$

ADDm performs the following operation.

# $M[r_d] \leftarrow M[r_s] + M[r_t]$

Fill in Worksheet M14.1-1 with the microcode for ADDm. Use *don't cares* (\*) for fields where it is safe to use don't cares. Study the hardware description well, and make sure all your microinstructions are legal.

Please comment your code clearly. If the pseudo-code for a line does not fit in the space provided, or if you have additional comments, you may write in the margins as long as you do it neatly. Your code should exhibit "clean" behavior and not modify any registers (except  $r_d$ ) in the course of executing the instruction.

Finally, make sure that the instruction fetches the next instruction (by doing a microbranch to FETCH0 as discussed above).

## Problem M14.1.B

#### **Implementing DBNEZ Instruction**

DBNEZ stands for Decrease Branch Not Equal Zero. This instruction uses the same encoding as conditional branch instructions on MIPS.

| 6      | 5  | 5 | 16     |

|--------|----|---|--------|

| opcode | rs |   | Offset |

DBNEZ decrements register **rs** by 1, writes the result back to **rs** and branches to (**PC**+4)+**offset**, if result in **rs** is not equal to 0. Offset is sign extended to allow for backward branches. This instruction can be used for efficiently implementing loops.

Your task is to fill out Worksheet M14.1-2 for DBNEZ instruction. You should try to optimize your implementation for minimum number of cycles necessary and for maximum number of don't-care signals. You do not have to worry about the busy signal.

(Note that the microcode for the fetch stage has changed slightly from the one in Problem M14.1.A, to allow for a more efficient implementation of some instructions.)

| Problem     | M14.1.C |

|-------------|---------|

| I I UNIVIII |         |

#### Implementing RETZ Instruction

In this question we ask you to implement a special return instruction, *return on zero* (**retz**), which uses the same encoding as a conditional branch instruction on MIPS.

|      | retz Rs, Rt |    |        |  |  |  |  |  |  |  |  |  |

|------|-------------|----|--------|--|--|--|--|--|--|--|--|--|

| 6    | 5           | 5  | 16     |  |  |  |  |  |  |  |  |  |

| Retz | Rs          | Rt | Unused |  |  |  |  |  |  |  |  |  |

retz instruction provides fast return from a subroutine call using  $\mathbf{Rt}$  as the stack pointer. The instruction first tests the value of register  $\mathbf{Rs}$ . If it is **not** zero, simply proceed to the next instruction at **PC+4**. If it is zero, the instruction does the following: (1) it reads the return address from memory at the address in register  $\mathbf{Rt}$ , (2) increments  $\mathbf{Rt}$  by 4 and (3) jumps to the return address.

Fill out Worksheet M14.1-3 for the retz instruction. You should try to optimize your implementation for minimum number of cycles necessary and for maximum number of don't-care signals. You do not have to worry about the busy signal. You may not need all the lines in the table for your solution.

You are allowed to introduce *at most* one new  $\mu$ Br target (Next State) for J (Jump) or Z (branchif-Zero) other than FETCH0. In this question you will implement a new complex CALL instruction, which uses the same encoding as a conditional branch instruction on MIPS.

| 6      | 5  | 5 | 16     |

|--------|----|---|--------|

| opcode | ra |   | Offset |

CALL stores the return address, PC+4, to memory at the address in register **ra** (i.e., in **M[ra]**), decrements **ra** by 4, saves the new value back to **ra** and branches to (PC+4)+offset. This instruction provides fast subroutine calls, using register **ra** as the stack pointer.

Your task is to fill out Worksheet M14.1-4 for the CALL instruction. You should optimize your implementation to execute in the minimum number of cycles and to have the most signals set to don't care. You do not have to worry about the busy signal from memory. You may not need all the lines in the table for your solution.

## Problem M14.1.E

## **Instruction Execution Times**

How many cycles does it take to execute the following instructions in the microcoded MIPS machine? Use the states and control points from the MIPS microcontroller in Lecture 20 and assume Memory will not assert its busy signal.

| Instruc | tion     |   |     |     |    | Cycles |

|---------|----------|---|-----|-----|----|--------|

| SUB     | R3,R2,R1 |   |     |     |    |        |

| SUBI    | R2,R1,#4 |   |     |     |    |        |

| SW      | R1,0(R2) |   |     |     |    |        |

| BEQZ    | R1,label | # | (R1 | ==  | 0) |        |

| BNEZ    | R1,label | # | (R1 | ! = | 0) |        |

| J       | label    |   |     |     |    |        |

| JR      | R1       |   |     |     |    |        |

| JAL     | label    |   |     |     |    |        |

| JALR    | R1       |   |     |     |    |        |

Which instruction takes the most cycles to execute? Which instruction takes the fewest cycles to execute?

# Problem M14.1.F

Exponentiation

Ben Bitdiddle needs to compute the power function for small numbers. Realizing there is no multiply instruction in the microcoded MIPS machine, he uses the following code to calculate the result when an unsigned number m is raised to the nth power, where n is another unsigned number.

```

if (m == 0) {

result = 0;

}

else {

result = 1;

i = 0;

while (i < n) {

temp = result;

j = 1;

while (j < m) {

result += temp;

j++;

}

i++;

}

}

```

The variables i, j, m, n, temp and result are unsigned 32-bit values.

Write the MIPS assembly that implements Ben's code. Use only the MIPS instructions that can be executed on the microcoded MIPS machine (ALU, ALUi, LW, SW, J, JAL, JR, JALR, BEQZ and BNEZ). The microcoded MIPS machine does not have branch delay slots. Use R1 for m, R2 for n and R3 for result. At the end of your code only R3 must have the correct value. The values of all other registers do not have to be preserved.

How many MIPS instructions are executed to calculate the power function? How many cycles does it take to calculate the power function? Again, use the states and control points from the MIPS microcontroller in Lecture 20 and assume Memory will not assert its busy signal.

| m, n | Instructions | Cycles |

|------|--------------|--------|

| 0, 1 |              |        |

| 1,0  |              |        |

| 2, 2 |              |        |

| 3, 4 |              |        |

| M, N |              |        |

## Problem M14.1.G

## Microcontroller Jump Logic

Now we will fill in a gap in the microcontroller implementation. In the lecture on microprogramming, we did not explain the implementation of the jump logic of the microcontroller. Your task in this problem is to implement that logic. Use AND gates, OR gates and inverters to implement the combinational logic that realizes the control equations for the jump logic of the MIPS microcontroller below. The control equations for the jump logic are

# μPCSrc = *Case* μJumpTypes

| next     | => | μPC+1                         |

|----------|----|-------------------------------|

| spin     | => | μPC.busy + (μPC+1).~busy      |

| fetch    | => | absolute                      |

| dispatch | => | op-group                      |

| feqz     | => | absolute.zero + (µPC+1).~zero |

| fnez     | => | absolute.~zero + (µPC+1).zero |

The selection bits for each input of the  $\mu$ PCSrc mux, as well as the  $\mu$ JumpTypes encoding are given in the tables below. Your task is to create combinational logic that translates between them, according to the control equations. Assume that the busy and zero signals follow positive logic (so they are true if the wire is carrying a 1 and false if the wire is carrying a 0). Your design will be judged for its correctness, clarity and organization. These factors are more important than the efficiency of your design.

| μJumpTypes | Encoding |

|------------|----------|

| next       | 000      |

| spin       | 001      |

| feqz       | 110      |

| fnez       | 111      |

| fetch      | 010      |

| dispatch   | 100      |

Table M14.1-2: µJumpTypes Encoding

| μPCSrc   | Selection bits |

|----------|----------------|

| µPC+1    | 00             |

| μPC      | 01             |

| absolute | 10             |

| op-group | 11             |

Table M14.1-1: µPCSrc Selection bits

| State   | PseudoCode                    | ld<br>IR | Reg<br>Sel | Reg<br>W | en<br>Reg | ld<br>A | ld<br>B | ALUOp   | en<br>ALU | ld<br>MA | Mem<br>W | en<br>Mem | Ex<br>Sel | en<br>Imm | μB<br>r | Next State |

|---------|-------------------------------|----------|------------|----------|-----------|---------|---------|---------|-----------|----------|----------|-----------|-----------|-----------|---------|------------|

| FETCH0: | MA <- PC;<br>A <- PC          | 0        | PC         | 0        | 1         | 1       | *       | *       | 0         | 1        | *        | 0         | *         | 0         | N       | *          |

|         | IR <- Mem                     | 1        | *          | *        | 0         | 0       | *       | *       | 0         | 0        | 0        | 1         | *         | 0         | Ν       | *          |

|         | PC <- A+4                     | 0        | PC         | 1        | 1         | 0       | *       | INC_A_4 | 1         | *        | *        | 0         | *         | 0         | D       | *          |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

| NOP0:   | microbranch<br>back to FETCH0 | 0        | *          | *        | 0         | *       | *       | *       | 0         | *        | *        | 0         | *         | 0         | J       | FETCH0     |

| ADDM0:  |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

| State   | PseudoCode                    | ld<br>IR | Reg<br>Sel | Reg<br>W | en<br>Reg | ld<br>A | ld<br>B | ALUOp   | en<br>ALU | Ld<br>MA | Mem<br>W | en<br>Mem | Ex<br>Sel | en<br>Imm | μB<br>r | Next State |

|---------|-------------------------------|----------|------------|----------|-----------|---------|---------|---------|-----------|----------|----------|-----------|-----------|-----------|---------|------------|

| FETCH0: | MA <- PC;<br>A <- PC          | *        | PC         | 0        | 1         | 1       | *       | *       | 0         | 1        | *        | 0         | *         | 0         | Ν       | *          |

|         | IR <- Mem                     | 1        | *          | *        | 0         | 0       | *       | *       | 0         | *        | 0        | 1         | *         | 0         | Ν       | *          |

|         | PC <- A+4;<br>B <- A+4        | 0        | PC         | 1        | 1         | *       | 1       | INC_A_4 | 1         | *        | *        | 0         | *         | 0         | D       | *          |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

| NOP0:   | microbranch<br>back to FETCH0 | *        | *          | *        | 0         | *       | *       | *       | 0         | *        | *        | 0         | *         | 0         | J       | FETCH0     |

| DBNEZ:  |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

# *Last updated:* 4/30/2020

| State   | PseudoCode                    | Ld<br>IR | Reg<br>Sel | Reg<br>W | en<br>Reg | ld<br>A | ld<br>B | ALUOp   | en<br>ALU | Ld<br>MA | Mem<br>W | en<br>Mem | Ex<br>Sel | en<br>Im<br>m | μBr | Next State |

|---------|-------------------------------|----------|------------|----------|-----------|---------|---------|---------|-----------|----------|----------|-----------|-----------|---------------|-----|------------|

| FETCH0: | MA <- PC;<br>A <- PC          | *        | PC         | 0        | 1         | 1       | *       | *       | 0         | 1        | *        | 0         | *         | 0             | N   | *          |

|         | IR <- Mem                     | 1        | *          | *        | 0         | 0       | *       | *       | 0         | *        | 0        | 1         | *         | 0             | Ν   | *          |

|         | PC <- A+4;<br>B <- A+4        | 0        | PC         | 1        | 1         | *       | 1       | INC_A_4 | 1         | *        | *        | 0         | *         | 0             | D   | *          |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

| NOP0:   | microbranch<br>back to FETCH0 | *        | *          | *        | 0         | *       | *       | *       | 0         | *        | *        | 0         | *         | 0             | J   | FETCH0     |

| retz0   |                               |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

# *Last updated:* 4/30/2020

| State   | PseudoCode                    | ld<br>IR | Reg<br>Sel | Reg<br>W | en<br>Reg | ld<br>A | ld<br>B | ALUOp   | en<br>ALU | Ld<br>MA | Mem<br>W | en<br>Mem | Ex<br>Sel | en<br>Imm | μB<br>r | Next State |

|---------|-------------------------------|----------|------------|----------|-----------|---------|---------|---------|-----------|----------|----------|-----------|-----------|-----------|---------|------------|

| FETCH0: | MA <- PC;<br>A <- PC          | *        | PC         | 0        | 1         | 1       | *       | *       | 0         | 1        | *        | 0         | *         | 0         | Ν       | *          |

|         | IR <- Mem                     | 1        | *          | *        | 0         | 0       | *       | *       | 0         | *        | 0        | 1         | *         | 0         | Ν       | *          |

|         | PC <- A+4;<br>B <- A+4        | 0        | PC         | 1        | 1         | *       | 1       | INC_A_4 | 1         | *        | *        | 0         | *         | 0         | D       | *          |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

| NOP0:   | microbranch<br>back to FETCH0 | *        | *          | *        | 0         | *       | *       | *       | 0         | *        | *        | 0         | *         | 0         | J       | FETCH0     |

| CALL:   |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

|         |                               |          |            |          |           |         |         |         |           |          |          |           |           |           |         |            |

# **Problem M14.2: VLIW Programming**

Ben Bitdiddle and Louis Reasoner have started a new company called Transbeta<sup>®</sup> and are designing a new processor named Titanium<sup>TM</sup>. The Titanium processor is a single-issue in-order VLIW processor with:

- 2 load/store units. There is no cache and a load has a latency of 4 cycles but is fully pipelined.

- 1 integer ALU: single cycle

- 1 floating-point multiplier: 3 cycles, fully pipelined

- 1 floating-point adder: 2 cycles, fully pipelined

- 1 branch unit with no delay slots and 100% branch prediction accuracy

- 128 GPRs and 128 FPRs

A single Titanium instruction can issue to all the above units simultaneously. By definition, the operations in a Titanium instruction are independent. Every operation in a Titanium instruction reads the operands and issues simultaneously. Thus, if one operation is waiting for a result of a previous Titanium instruction, the entire Titanium instruction is stalled in the decode stage.

Everything is fully bypassed. Each functional unit has a dedicated writeback port, so there is never any contention. Writing to the same register multiple times in the same instruction is disallowed in the Titanium ISA. WAW hazards will also cause stalls. The Titanium ISA resembles MIPS, except that there can be up to 6 instructions on each line separated by semicolons.

You have been hired to work on some hand-optimized math libraries. The most important of these is the dot-product, given by  $\Sigma(X_n \times Y_n)$ .

## Problem M14.2.A

Ben has translated dot-product from MIPS to the Titanium ISA

```

// R1 - pointer to X

// R2 - pointer to Y

// R5 - n

// R3 - temp

// F4 - temp

// F6 - result

MOVI2FP F6,R0

loop:

L.S F3,0(R1); L.S F4,0(R2); ADDI R5,R5,#-1

MUL.S F3,F3,F4; ADDI R1,R1,#4

ADD.S F6,F6,F3; ADDI R2,R2,#4; BNEZ R5,loop

```

Each iteration takes 9 cycles but the program averages 8 cycles per vector element. Alyssa P. Hacker says that it can be done in 1 cycle per vector element for long vectors. Show Ben and Louis what the code should be. Louis isn't too bright so make sure your code is well commented.

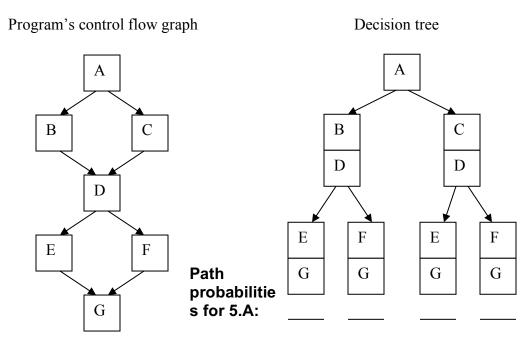

# **Problem M14.3: Trace Scheduling**

Trace scheduling is a compiler technique that increases ILP by removing control dependencies, allowing operations following branches to be moved up and speculatively executed in parallel with operations before the branch. It was originally developed for statically scheduled VLIW machines, but it is a general technique that can be used in different types of machines and in this question we apply it to a single-issue MIPS processor.

Consider the following piece of C code (% is modulus) with basic blocks labeled.

| A: | if (data | 00 | 8 == | 0) |

|----|----------|----|------|----|

| В: | X = V0   | /  | V1;  |    |

|    | else     |    |      |    |

| C: | X = V2   | /  | V3;  |    |

| D: | if (data | 00 | 4 == | 0) |

| Е: | Y = V0   | *  | V1;  |    |

|    | else     |    |      |    |

| F: | Y = V2   | *  | V3;  |    |

| G: |          |    |      |    |

Assume that **data** is a uniformly distributed integer random variable that is set sometime before executing this code.

The control flow graph and the decision tree both show the possible flows of execution through basic blocks. However, the control flow graph captures the static structure of the program, while the decision tree captures the dynamic execution (history) of the program.

# Problem M14.3.A

On the decision tree, label each path with the probability of traversing that path. For example, the leftmost block will be labeled with the total probability of executing the path ABDEG. (Hint: you might want to write out the cases). Circle the path that is most likely to be executed.

## Problem M14.3.B

This is the MIPS code (no delay slots):

```

A:

r1, data

lw

andi r2, r1, 7 ;; r2 <- r1%8

bnez r2, C

div r3, r4, r5 ;; X <- V0/V1

B:

i

D

r3, r6, r7 ;; X <- V2/V3

C:

div

andi r2, r1, 3 ;; r2 <- r1%4

D:

bnez r2, F

r8, r4, r5 ;; Y <- V0*V1

Е:

mul

j

G

r8, r6, r7 ;; Y <- V2*V3

F:

mul

G:

```

This code is to be executed on a single-issue processor **without** branch speculation. Assume that the memory, divider, and multiplier are all separate, long latency, **unpipelined** units that can run in parallel. Rewrite the above code using trace scheduling. Optimize only for the most common path. Just get the other paths to work. Don't spend your time performing any other optimizations. Ignore the possibility of exceptions. (Hint: Write the most common path first and then add fix-up code.)

# Problem M14.3.C

Assume that the load takes x cycles, divide takes y cycles, and multiply takes z cycles. Approximately how many cycles does the original code take? (Ignore small constants.) Approximately how many cycles does the new code take in the best case?

# **Problem M14.4: VLIW Machines**

The program we will use for this problem is listed below. (In all questions, you should assume that arrays  $\mathbf{A}$ ,  $\mathbf{B}$  and  $\mathbf{C}$  do not overlap in memory.)

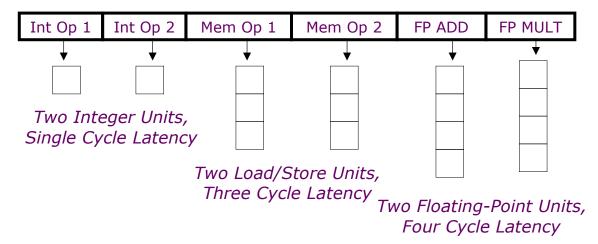

In this problem, we will deal with the code sample on a VLIW machine. Our machine will have six execution units.

- two ALU units: latency one cycle, also used for branch operations

- two memory units: latency three cycles, fully pipelined, each unit can perform either a store or a load

- two FPU units: latency four cycles, fully pipelined, one unit can perform **fadd** operations, the other **fmul** operations.

Our machine has no interlocks. The result of an operation is written to the register file immediately after it has gone through the corresponding execution unit: one cycle after issue for ALU operations, three cycles for memory operations and four cycles for FPU operations. The old values can be read from the registers until they have been overwritten.

Below is a diagram of our VLIW machine.

| loop: | 1.  | ld f1, 0(r1)    | ; $f1 = A[i]$    |

|-------|-----|-----------------|------------------|

|       | 2.  | ld f2, 0(r2)    | ; $f2 = B[i]$    |

|       | 3.  | fmul f4, f2, f1 | ; $f4 = f1 * f2$ |

|       | 4.  | st f4, 0(r1)    | ; $A[i] = f4$    |

|       | 5.  | ld f3, 0(r3)    | ; $f3 = C[i]$    |

|       | 6.  | fadd f5, f4, f3 | ; $f5 = f4 + f3$ |

|       | 7.  | st f5, 0(r3)    | ; $C[i] = f5$    |

|       | 8.  | add r1, r1, 4   | ; i++            |

|       | 9.  | add r2, r2, 4   |                  |

|       | 10. | add r3, r3, 4   |                  |

|       | 11. | add r4, r4, -1  |                  |

|       |     | bnez r4, loop   | ; loop           |

The program for this problem translates to the following VLIW operations:

## Problem M14.4.A

**Table M14.4-1**, on the next page, shows our program rewritten for our VLIW machine, with some operations missing (instructions 2, 6 and 7). We have rearranged the instructions to execute as soon as they possibly can, but ensuring program correctness. Please fill in the missing operations. (Note, you may not need all the rows.)

## Problem M14.4.B

How many cycles are required to complete one iteration of the loop in steady state? What is the performance (flops/cycle) of the program?

## Problem M14.4.C

How many VLIW instructions would the smallest software pipelined loop require? Explain briefly. Ignore the prologue and the epilogue. Note: You do not need to write the software pipelined version. (You may consult **Table M14.4-1** for help.)

## Problem M14.4.D

What would be the performance (flops/cycle) of the program? How many iterations of the loop would we have executing at the same time?

| ALU1          | ALU2           | MU1          | MU2           | FADD | FMUL            |

|---------------|----------------|--------------|---------------|------|-----------------|

| Add r1, r1, 4 | add r2, r2, 4  | ld f1, 0(r1) |               |      |                 |

| Add r3, r3, 4 | add r4, r4, -1 | ld f3, 0(r3) |               |      |                 |

|               |                |              |               |      |                 |

|               |                |              |               |      | fmul f4, f2, f1 |

|               |                |              |               |      |                 |

|               |                |              |               |      |                 |

|               |                |              |               |      |                 |

|               |                |              | st f4, -4(r1) |      |                 |

|               |                |              |               |      |                 |

|               |                |              |               |      |                 |

|               |                |              |               |      |                 |

|               | bnez r4, loop  |              |               |      |                 |

|               |                |              |               |      |                 |

|               |                |              |               |      |                 |

|               |                |              |               |      |                 |

Table M14.4-1: VLIW Program

## Problem M14.4.E

If we unrolled the loop once, would that give us better performance? How many VLIW instructions would we need for optimal performance? How many flops/cycle would we get? Explain.

#### Problem M14.4.F

What is the optimal performance in flops/cycle for this program on this architecture? Explain.

#### Problem M14.4.G

If our machine had a rotating register file, could we use fewer instructions than in *Problem M14.4.F* and still achieve optimal performance? Explain.

## Problem M14.4.H

Imagine that memory latency has just increased to 100 cycles. How many instructions (approximately) an optimal loop would require? (There is no rotating register file, and ignore prologue/epilogue). Explain briefly.

5 50 100 200

## Problem M14.4.I

Now our processor still has a memory latency of up to 100 cycles when it needs to retrieve data from main memory, but only 3 cycles if the data comes from the cache. Thus a memory operation can complete and write its result to a register anywhere between 3 and 100 cycles after being issued. Since our processor has no interlocks, other instructions will continue being issued. Thus, given two instructions, it is possible for the instruction issued second to complete and write back its result first. Circle how many instructions (approximately) are required for an optimal loop. Explain briefly.

5 50 100 200

# Problem M14.5: VLIW & Vector Coding

Ben Bitdiddle has the following C loop, which takes the absolute value of elements within a vector.

```

for (i = 0; i < N; i++) {

if (A[i] < 0)

A[i] = -A[i];

}</pre>

```

## Problem M14.5.A

Ben is working with an in-order VLIW processor, which issues two MIPS-like operations per instruction cycle. Assume a five-stage pipeline with two single-cycle ALUs, memory with one read and one write port, and a register file with four read ports and two write ports. Also assume that there are no branch delay slots, and loads and stores only take one cycle to complete. Turn Ben's loop into VLIW code. A[i's] and N are 32-bit signed integers. Initially, R1 contains N and R2 points to A[0]. You do not have to preserve the register values. Optimize your code to improve performance but do not use loop unrolling or software pipelining. What is the average number of cycles per element for this loop, assuming data elements are equally likely to be negative and non-negative?

## Problem M14.5.B

Ben wants to remove the data-dependent branches in the assembly code by using predication. He proposes a new set of predicated instructions as follows.

- 1) Augment the ISA with a set of 32 predicate bits P0-P31.

- 2) Every standard non-control instruction now has a predicated counterpart, with the following syntax:

(pbit1) OPERATION1 ; (pbit2) OPERATION2

(Execute the first operation of the VLIW instruction if pbit1 is set and execute the second operation of the VLIW instruction if pbit2 is set.)

3) Include a set of compare operations that conditionally set a predicate bit.

CMPLTZ pbit,reg ; set pbit if reg < 0

CMPGEZ pbit,reg ; set pbit if reg >= 0

CMPEQZ pbit,reg ; set pbit if reg == 0

CMPNEZ pbit,reg ; set pbit if reg != 0

Eliminate all forward branches from Question M14.5.A with the new predicated operations. Try to optimize your code but do not use software pipelining or loop unrolling.

What is the average number of cycles per element for this new loop? Assume that the predicateset compare instructions have a single cycle latency (i.e., they behave similarly to a regular ALU instruction including, full bypassing of the predicate bit).

# Problem M14.5.C

Unroll the predicated VLIW code to perform two iterations of the original loop before each backward branch. You should use software pipelining to optimize the code for both performance and code density. What is the average number of cycles per element for a large value of N?

## Problem M14.5.D

Now Ben wants to work with a vector processor with two lanes, each of which has a single-cycle ALU and a vector load-store unit. Write-back to the vector register file takes a single cycle. Assume for this part that each vector register has at least N elements.

Ben can also eliminate branches from his code by using vector masks. He wants to introduce a vector mask register as follows.

- 1) Augment the ISA with a vector mask register, VM.

- 2) Every vector instruction now executes each element operation only if the corresponding bit in the mask register is set.

- 3) Include compare operations that conditionally set the mask register.

S--VV1, V2Compare the elements (EQ,NE,GT,LT,GE,LE) in V1 and V2. If condition isS--SVF0, V1true, put a 1 in the corresponding bit vector; otherwise put 0. Put the<br/>resulting bit vector in a vector-mask register (VM). The instruction S--SV<br/>performs the same compare but using a scalar value as one operand.

Vectorize Ben's C loop, and replace all branches using vector masks. What is the average number of cycles per element for this loop in steady state for a very large value of N?

## Problem M14.5.E

Modify the code from Part M14.5.D to handle the case when each vector register has *m* elements, where *m* may be less than N and is not necessarily a factor of N.

# **Problem M14.6: Predication and VLIW**

## Problem M14.6.A

Consider the following code.

l.s f1, 0(r1) ; f1 = \*r1seq.s r5, f10, f1 ; bneq f1, f10, else ; if f1==f10 add.s f2, f1, f11 ; f2 = f1 + f11; else if end b add.s f2, f1, f12 f2 = f1 + f12else: ; if end: s.s f2, 0(r2) ; \*r2 = f2

Convert the code above to use predication rather than conditional branches. You should use the CMPLTZ, CMPGEZ, CMPEQZ or CMPNEZ instruction from Problem M5.8.B for predication. You may use negative predication for instructions, e.g.

(p1) add r1, r2, r3 ; if (p1) r1 = r2 + r3(!p1) add r1, r2, r3 ; if (!p1) r1 = r2 + r3

## Problem M14.6.B

Our VLIW processor, called Adamantium, is very similar to the Titanium processor from Problem M14.2. Below are the details of our machine. Bold parts are different from Titanium.

- 1 load/store unit: There is no cache and a load has a latency of 2 cycles and is fully pipelined.

- 1 integer ALU: Single cycle latency

- no floating-point multiplier unit

- 1 floating-point adder: 2 cycles, fully pipelined

- 1 branch unit with no delay slots and 100% branch prediction accuracy

- 128 GPRs, 128 FPRs and 128 predicate registers

Consider the following simple loop written in predicated MIPS assembler.

```

loop: l.s f1, 0(r1) ; f1 = *r1

cmpnez p1, f1 ; p1 = (f1 != 0)

(p1) add.s f2, f1, f1 ; if (p1) f2 = f1+f1

(p1) s.s f2, 0(r1) ; if (p1) *r1 = f2

addi r1, r1, #4 ; r1 += 4

bneq r1, r2, loop ; if (r1!=r2) goto loop

end:

```

On the next page, in Table M14.6-1, we have converted the code above into Adamantium code and unrolled it twice. Complete a software pipelined version of this loop for Adamantium below in Table M14.6-2. You should assume that the number of times the loop needs to execute is divisible by the unrolling factor, thus the loop doesn't need any fix-up code.

| Label | integer op      | floating point add    | memory op           | branch            |

|-------|-----------------|-----------------------|---------------------|-------------------|

| loop: |                 |                       | l.s f1,0(r1)        |                   |

|       |                 |                       | 1.s f3,4(r1)        |                   |

|       | addi r1, r1, #8 | cmpnez p1, f1         |                     |                   |

|       |                 | cmpnez p3, f3         |                     |                   |

|       |                 | (p1) add.s f2, f1, f1 |                     |                   |

|       |                 | (p3) add.s f4, f3, f3 |                     |                   |

|       |                 |                       | (p1) s.s f2, -8(r1) |                   |

|       |                 |                       | (p3) s.s f4, -4(r1) | bneq r1, r2, loop |

# Table M14.6-1

| label   | integer op      | floating point add | memory op    | Branch             |

|---------|-----------------|--------------------|--------------|--------------------|

|         |                 |                    | l.s f1,0(r1) |                    |

|         |                 |                    | l.s f3,4(r1) |                    |

|         | addi r1, r1, #8 | cmpnez p1, f1      |              |                    |

|         |                 | cmpnez p3, f3      |              | beq r1, r2, epilog |

| loop:   |                 |                    |              |                    |

|         |                 |                    |              |                    |

|         |                 |                    |              |                    |

|         |                 |                    |              | bneq ,loop         |

| epilog: |                 | (p1) add.s         |              |                    |

|         |                 | (p3) add.s         |              |                    |

|         |                 |                    | (p1) s.s     |                    |

|         |                 |                    | (p3) s.s     |                    |

Table M14.6-2

# **Problem M14.7: Vector Machines**

In this problem, we analyze the performance of vector machines. We start with a baseline vector processor with the following features.

- 32 elements per vector register

- 8 lanes

- One ALU per lane: 1 cycle latency

- One MULT per lane: 2 cycle latency, fully pipelined

- One LOAD/STORE unit per lane: 4 cycle latency, fully pipelined

- No dead time

- No support for chaining

- Scalar instructions execute on a separate 5-stage fully-bypassed pipeline

To simplify the analysis, we assume a **magic memory system** with no bank conflicts and no cache misses. Also, scalar operands of vector instructions are read in the Decode stage.

The program we will use for this problem is listed below. (In all questions, you should assume that arrays  $\mathbf{A}$ ,  $\mathbf{B}$  and  $\mathbf{C}$  do not overlap in memory.)

C code

for (i=0; i<328; i++) {

A[i] = A[i] \* B[i];

C[i] = C[i] + A[i];

}</pre>

# Problem M14.7.A

Consider the implementation of the C-code on the vector machine that executes it in the least number of cycles. Assuming the following initial values, insert vector instructions to complete the implementation.

| 0<br>0 | R2 poi<br>R3 poi | ints to A[0]<br>ints to B[0]<br>ints to C[0]<br>ntains the va | lue 328 |   |                      |

|--------|------------------|---------------------------------------------------------------|---------|---|----------------------|

|        | ANDI             | R5, R4,                                                       | 31      | # | 328 mod 32           |

|        | MTC1             | VLR, R5                                                       |         | # | set VLR to remainder |

| loop   | :                |                                                               |         |   |                      |

|        | LV               | V1, R1                                                        |         | # | load A               |

|        | LV               | V2, R2                                                        |         | # | load B               |

|        | SLL              | R7, R5,                                                       | 2       |   |                      |

|        | ADD              | R1, R1,                                                       | R7      | # | increment A ptr      |

|        | ADD              | R2, R2,                                                       | R7      | # | increment B ptr      |

|        | ADD              | R3, R3,                                                       | R7      | # | increment C ptr      |

|        | SUB              | R4, R4,                                                       | R5      | # | update loop counter  |

|        | LI               | R5, 32                                                        |         | # | reset VLR to max     |

|        | MTC1             | VLR, R5                                                       |         |   |                      |

|        | BGTZ             | R4, looj                                                      | þ       |   |                      |

## Problem M14.7.B

Complete the pipeline diagram below with the loop code from Question M14.7.A on the baseline vector processor for one loop iteration. Do not fill in scalar instructions. Assume the scalar registers are available immediately, whenever needed. You may not require the entire length of the table.

#### The following supplementary information explains the diagram.

Scalar instructions execute in 5 cycles: fetch (F), decode (D), execute (X), memory (M), and writeback (W). A vector instruction is also fetched (F) and decoded (D). Then, it stalls (—) until its required vector functional unit is available. With no chaining, a dependent vector instruction stalls until the previous instruction finishes writing back ALL of its elements. A vector instruction is pipelined across all the lanes in parallel. For each element, the operands are read (R) from the vector register file, the operation executes on the load/store unit (M) or the ALU (X) or the MUL (Y), and the result is written back (W) to the vector register file. Assume that there is no structural conflict on the writeback port. A stalled vector instruction does not block a scalar instruction from executing.

| •               |          |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    | cyc | cle |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|-----------------|----------|---|---|----|----------|----|----|----|----|-------------|----|------|----------|----------|----|----|----|----|----|-----|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| instr.          | 1        | 2 | 3 | 4  | 5        | 6  | 7  | 8  | 9  | 10          | 11 | 12   | 13       | 14       | 15 | 16 | 17 | 18 | 19 | 20  | 21  | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 |

| $LV_1$          | F        | D | R | M1 | M2       | М3 | M4 | W  |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| $LV_1$          |          |   |   | R  | M1       | М2 | М3 | M4 | W  |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| $LV_1$          |          |   |   |    | R        | M1 | M2 | М3 | M4 | 4 W         |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| $LV_1$          |          |   |   |    |          | R  | M1 | M2 | M3 | <b>3</b> M4 | W  |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| $LV_2$          | 1        | F | D |    |          |    |    |    |    |             |    | W    |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| $LV_2$          |          |   |   |    |          |    |    | -  | -  | -           | -  | 6 M4 | -        |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| LV <sub>2</sub> |          |   |   |    |          |    |    |    |    |             |    | 2 МЗ |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| $LV_2$          |          |   |   |    |          |    |    |    |    |             |    | M2   |          |          | w  |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| LVZ             |          |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                 |          |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                 |          |   |   |    |          |    |    |    |    |             | -  | -    |          |          |    | -  |    | -  |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    | -  |    |    |    |    |

|                 | ╢        |   |   | -  |          |    |    |    |    |             |    | -    | -        | -        |    | -  |    | -  |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    | -  |    |    |    |    |

|                 |          |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                 |          |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                 |          |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                 |          |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | _  |    |    |

|                 |          |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                 |          |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                 |          |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                 |          |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                 |          |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                 |          |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                 |          |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                 |          |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | _  |

|                 |          |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | -  |

|                 | i –      |   |   |    |          |    |    |    |    | -           | 1  | 1    | -        | -        |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    | -  |    |    |    | -  |

|                 |          |   |   | -  |          |    | -  |    |    |             | -  | -    | -        | -        | -  |    | -  |    |    |     |     |    | -  |    |    |    |    |    |    |    | -  | -  |    |    |    | -  |    |    |    |    |

|                 | -        | - |   |    | -        |    | -  | -  | -  | -           | -  | -    | -        | -        | -  | -  | -  | -  | -  | -   | -   |    |    | -  | -  |    |    |    | -  |    |    | -  | -  | -  |    | -  |    |    |    | -  |

|                 | ╢        |   |   | -  |          |    |    |    |    |             |    | -    | -        | -        |    | -  |    | -  |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    | -  |    |    |    | _  |

|                 | -        |   |   |    |          |    |    |    |    |             |    |      | -        | -        |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                 | -        |   |   |    | -        |    |    |    |    | -           |    |      | -        | -        |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                 | <b> </b> |   |   |    |          |    |    |    |    |             | -  | -    | -        | -        |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    | -  |    |    | _  |    |

|                 | L        |   |   |    | <u> </u> |    |    |    |    |             |    |      | <u> </u> | <u> </u> |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                 | Į        |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|                 |          |   |   |    |          |    |    |    |    |             |    |      |          |          |    |    |    |    |    |     |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

$LV_1$  and  $LV_2$  refer to the first and second LV instructions in the loop.

# Problem M14.7.C

In this question, we analyze the performance benefits of chaining.

Vector chaining is done through the register file. An element can be read  $(\mathbf{R})$  on the same cycle in which it is written back  $(\mathbf{W})$ , or it can be read on any later cycle (chaining is *flexible*).

Complete the pipeline diagram below, with loop code from Question M14.7.A on a chained vector processor for one loop iteration. Do not fill in scalar instructions. Assume the scalar registers are available immediately, whenever needed. You may not require the entire length of the table.

| •                                  |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    | (  | cy | cle |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

|------------------------------------|---|---|---|----|----|------|-----|------------|------------|------|----|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----------|------|----|----|----------|----|

| instr.                             |   | 2 |   |    |    |      |     |            |            | 10   | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21  | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35       | 5 36 | 37 | 38 | 39       | 40 |

| $LV_1$                             | F | D | R | M1 | Mź | 2M3  | 8M4 | W          |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

| LV <sub>1</sub>                    |   |   |   | R  | M  | I M2 | 2M3 | <b>M</b> 4 | W          |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

| LV <sub>1</sub><br>LV <sub>1</sub> |   |   |   |    | R  | M1   | M2  | 2 M3       | <b>M</b> 4 | W    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

| LV <sub>1</sub>                    |   |   |   |    |    | R    | M1  | M2         | 2 M3       | 8 M4 | w  |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

| LV <sub>2</sub>                    |   | F | D |    |    |      | -   | -          | -          | 2М3  | _  | w  |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          | _  |

| LV <sub>2</sub>                    |   |   |   |    |    |      |     |            |            | M2   |    |    | w  |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          | _  |

| LV <sub>2</sub>                    |   |   |   |    |    |      |     |            |            |      | -  |    | M4 | w  |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          | _  |

| LV <sub>2</sub>                    |   |   |   |    |    |      |     |            |            |      | -  |    | М3 |    | w  |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

| 1112                               |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

|                                    |   |   |   |    |    | +    | 1   | 1          | +          | 1    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    | -  | -  |    |    |    | -  | -  |          | -    | -  |    | $\vdash$ |    |

|                                    |   |   |   |    |    | -    |     |            | -          |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    | -  |    | $\vdash$ | -    |    |    |          | -  |

|                                    |   |   |   |    |    | +    | -   | -          | -          | -    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    | -  |    | -        |      |    |    |          | _  |

|                                    |   |   |   |    |    | -    |     |            | -          |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    | -  |    | -        |      |    |    |          | _  |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          | -  |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    | -        |      |    |    |          |    |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          | _  |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          | _  |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          | _    |    |    |          | _  |

|                                    |   |   |   |    |    | -    |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          | _  |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          | _  |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          | _    |    |    |          | _  |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          | _    |    |    |          | _  |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

|                                    |   |   |   |    |    |      |     |            | -          |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |          |      |    |    |          |    |

|                                    |   |   |   |    |    | -    |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    | 1        |      |    |    |          |    |

|                                    |   |   |   |    |    |      |     |            |            |      |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    | 1  |    |          |      |    |    |          | _  |

# Problem M14.7.D

What is the performance (flops/cycle) of the program with chaining?

# Problem M14.7.E

Would loop unrolling of the assembly code improve performance without chaining? Explain. (You may rearrange the instructions when performing loop unrolling.)

# **Problem M14.8: Vector Machines**

In this problem, we analyze the performance of vector machines. We start with a baseline vector processor with the following features.

- 32 elements per vector register

- 8 lanes

- One ALU per lane: 1 cycle latency

- One load/store unit per lane: 4 cycle latency, fully pipelined

- No dead time

- No support for chaining

- Scalar instructions execute on a separate 5-stage pipeline

To simplify the analysis, we assume a magic memory system with no bank conflicts and no cache misses.

We consider the execution of the following loop.

| <u>C code</u>                                                       | assembly code                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>for (i=0; i&lt;320; i++) {     C[i] = A[i] + B[i] - 1; }</pre> | <pre># initial conditions:<br/># R1 points to A[0]<br/># R2 points to B[0]<br/># R3 points to C[0]<br/># R4 = 1<br/># R5 = 320</pre>                                                                                                                                                                                                              |

|                                                                     | <pre>loop:<br/>LV V1, R1 # load A<br/>LV V2, R2 # load B<br/>ADDV V3, V1, V2 # add A+B<br/>SUBVS V4, V3, R4 # subtract 1<br/>SV R3, V4 # store C<br/>ADDI R1, R1, 128 # incr. A pointer<br/>ADDI R2, R2, 128 # incr. B pointer<br/>ADDI R3, R3, 128 # incr. C pointer<br/>SUBI R5, R5, 32 # decr. count<br/>BNEZ R5, loop # loop until done</pre> |

## Problem M14.8.A

Complete the pipeline diagram of the baseline vector processor running the given code.

#### The following supplementary information explains the diagram:

Scalar instructions execute in 5 cycles: fetch (**F**), decode (**D**), execute (**X**), memory (**M**), and writeback (**W**). A vector instruction is also fetched (**F**) and decoded (**D**). Then, it stalls (—) until its required vector functional unit is available. With no chaining, a dependent vector instruction stalls until the previous instruction finishes writing back all of its elements. A vector instruction is pipelined across all the lanes in parallel. For each element, the operands are read (**R**) from the vector register file, the operation executes on the load/store unit (**M**) or the ALU (**X**), and the result is written back (**W**) to the vector register file. A stalled vector instruction does not block a scalar instruction from executing.

$LV_1$  and  $LV_2$  refer to the first and second LV instructions in the loop.

|                 |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | C  | cyc | le |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | ٦  |

|-----------------|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| instr.          | 1 | 2 | 3 | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 |    |     |    | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 |

| LV <sub>1</sub> | F | D | R | M1 | M2 | М3 | M4 | W  |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| LV <sub>1</sub> |   |   |   | R  | M1 | M2 | М3 | M4 | W  |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| LV <sub>1</sub> |   |   |   |    | R  | M1 | M2 | М3 | M4 | W  |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| LV <sub>1</sub> |   |   |   |    |    | R  | M1 | M2 | М3 | M4 | W  |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| LV <sub>2</sub> |   | F | D |    |    |    | R  | M1 | M2 | М3 | M4 | W  |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| LV <sub>2</sub> |   |   |   |    |    |    |    | R  | M1 | M2 | М3 | M4 | W  |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| LV <sub>2</sub> |   |   |   |    |    |    |    |    | R  | M1 | M2 | М3 | M4 | W  |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| LV <sub>2</sub> |   |   |   |    |    |    |    |    |    | R  | M1 | M2 | M3 | M4 | W  |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| ADDV            |   |   | F | D  |    |    |    | —  | —  |    |    |    |    |    |    | R  | X1 | W  |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| ADDV            |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    | R  | X1 | W  |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| ADDV            |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    | R  | X1 | W   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| ADDV            |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | R  | X1  | W  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| SUBVS           |   |   |   | F  | D  |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| SUBVS           |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| SUBVS           |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| SUBVS           |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| SV              |   |   |   |    | F  | D  |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| SV              |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| SV              |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| SV              |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| ADDI            |   |   |   |    |    | F  | D  | Х  | М  | W  |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| ADDI            |   |   |   |    |    |    | F  | D  | Х  | М  | W  |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| ADDI            |   |   |   |    |    |    |    | F  | D  | Х  | М  | W  |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| SUBI            |   |   |   |    |    |    |    |    | F  | D  | X  | М  | W  |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| BNEZ            |   |   |   |    |    |    |    |    |    | F  | D  | Χ  | М  | W  |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| LV <sub>1</sub> |   |   |   |    |    |    |    |    |    |    | F  | D  |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| LV <sub>1</sub> |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| LV <sub>1</sub> |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |