### **Complex Pipelining**

#### Daniel Sanchez Computer Science and Artificial Intelligence Laboratory M.I.T.

Instruction pipelining becomes complex when we want high performance in the presence of

- Multi-cycle operations, for example:

- Full or partially pipelined floating-point units, or

- Long-latency operations, e.g., divides

- Variable-latency operations, for example:

- Memory systems with variable access time

- Replicated function units, for example:

- Multiple floating-point or memory units

### CDC 6600 Seymour Cray, 1963

- A fast pipelined machine with 60-bit words

- 128 Kword main memory capacity, 32 banks

- Ten functional units (parallel, unpipelined)

- Floating Point: adder, 2 multipliers, divider

- Integer: adder, 2 incrementers, ...

- Hardwired control

- Dynamic scheduling of instructions using a scoreboard

- Ten Peripheral Processors for Input/Output

- A fast multi-threaded 12-bit integer ALU

- Very fast clock, 10 MHz (FP add in 4 clocks)

- >400,000 transistors, 750 sq. ft., 5 tons, 150 kW, new freon-based cooling technology

- Fastest machine in world for 5 years (until CDC 7600)

- Over 100 sold (\$7-10M each)

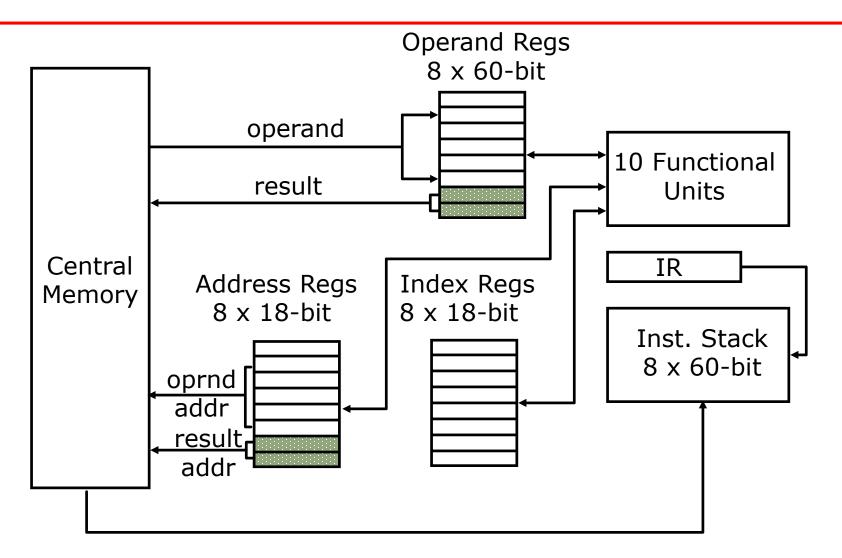

### CDC 6600: Datapath

### CDC 6600: A Load/Store Architecture

- Separate instructions to manipulate three types of reg.

- 8 60-bit data registers (X)

- 8 18-bit address registers (A)

- 8 18-bit index registers (B)

- All arithmetic and logic instructions are reg-to-reg

$Ri \leftarrow (Rj) op (Rk)$

• Only Load and Store instructions refer to memory!

- Touching address registers 1 to 5 initiates a load

6 to 7 initiates a store

- very useful for vector operations

### CDC6600: Vector Addition

B1  $\leftarrow$  - n loop: JZE B1, exit A1  $\leftarrow$  B1 + a1 A2  $\leftarrow$  B1 + b1 X6  $\leftarrow$  X1 + X2 A6  $\leftarrow$  B1 + c1 B1  $\leftarrow$  B1 + 1 jump loop

*load into X1 load into X2*

store X6

Ai = address register Bi = index register Xi = data register

more on vector processing later...

### We will present complex pipelining issues more abstractly ...

Interaction between the Floating point datapath and the Integer datapath is determined largely by the ISA

### MIPS ISA

- separate register files for FP and Integer instructions the only interaction is via a set of move instructions (some ISAs don't even permit this)

- separate load/store for FPR's and GPR's but both use GPR's for address calculation

- separate conditions for branches

FP branches are defined in terms of condition codes

Much more hardware than an integer unit

Single-cycle floating point unit is a bad idea - why?

- it is common to have several floating point units

- it is common to have different types of FPUs *Fadd, Fmul, Fdiv, ...*

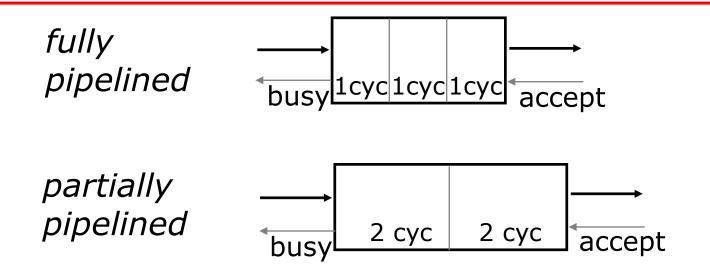

- an FPU may be pipelined, partially pipelined or not pipelined

To operate several FPUs concurrently the register file needs to have more read and write ports

### **Functional Unit Characteristics**

Functional units have internal pipeline registers

- ⇒ operands are latched when an instruction enters a functional unit

- ⇒ inputs to a functional unit (e.g., register file) can change during a long latency operation

### Realistic Memory Systems

Latency of access to the main memory is usually much higher than one cycle and often unpredictable *Solving this problem is a central issue in computer architecture*

# Common approaches to improving memory performance

- separate instruction and data memory ports

- $\Rightarrow$  no self-modifying code

- caches

- single cycle except in case of a miss  $\Rightarrow$  stall

- interleaved memory multiple memory accesses ⇒ bank conflicts

- split-phase memory operations

- ⇒ out-of-order responses

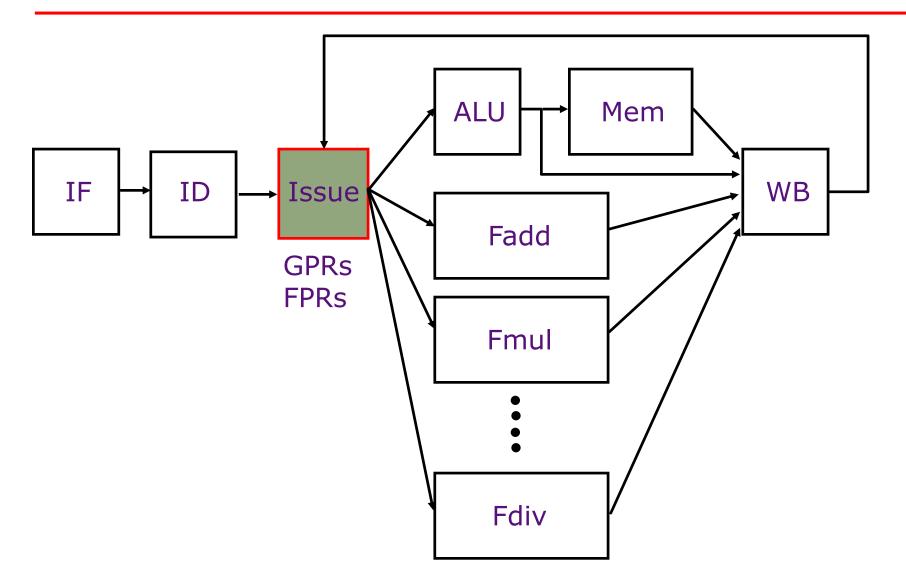

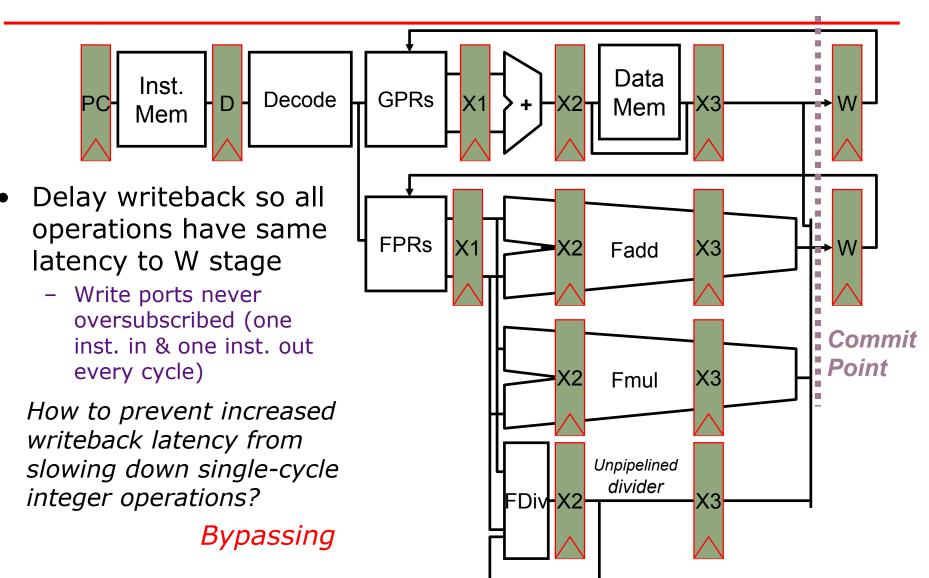

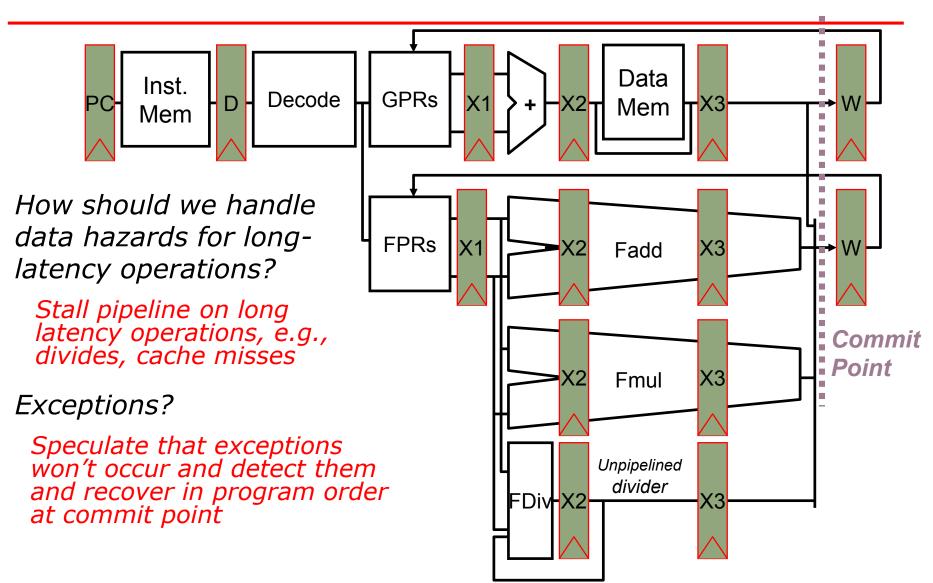

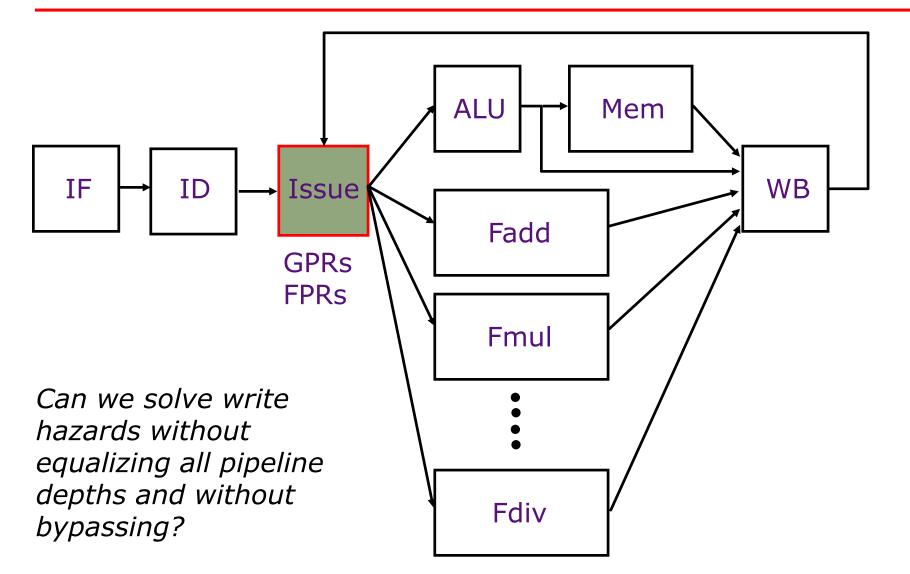

### **Complex Pipeline Structure**

### **Complex Pipeline Control Issues**

- Structural hazards at the execution stage if some FPU or memory unit is not pipelined and takes more than one cycle

- Structural hazards at the write-back stage due to variable latencies of different function units

- Out-of-order write hazards due to variable latencies of different function units

- How to handle exceptions?

# **Complex In-Order Pipeline**

# **Complex In-Order Pipeline**

March 16, 2021

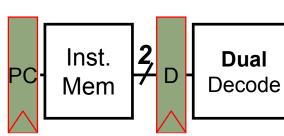

# Superscalar In-Order Pipeline

- Fetch two instructions per cycle; issue both simultaneously *if* one is integer/memory and other is floating-point

- Inexpensive way of increasing throughput

- Examples: Alpha 21064 (1992) MIPS R5000 series (1996)

- Can be extended to wider issue but register file ports and bypassing costs grow quickly

- E.g., 4-issue UltraSPARC

March 16, 2021

### **Dependence Analysis**

Needed to Exploit Instruction-level Parallelism

### Types of Data Hazards

# Consider executing a sequence of $r_k \leftarrow (r_i)$ op $(r_j)$ type of instructions

Data-dependenceRead-after-Write $r_3 \leftarrow (r_1)$  op  $(r_2)$ Read-after-Write $r_5 \leftarrow (r_3)$  op  $(r_4)$ (RAW) hazard

### **Detecting Data Hazards**

Range and Domain of instruction i

- R(i) = Registers (or other storage) modified by instruction i

- D(i) = Registers (or other storage) read by instruction i

Suppose instruction j follows instruction i in the program order. Executing instruction j before the effect of instruction i has taken place can cause a

| RAW hazard if | $R(i) \cap D(j) \neq \emptyset$ |

|---------------|---------------------------------|

| WAR hazard if | $D(i) \cap R(j) \neq \emptyset$ |

| WAW hazard if | $R(i) \cap R(j) \neq \emptyset$ |

### Register vs. Memory Data Dependences

- Data hazards due to register operands can be determined at the decode stage *but*

- Data hazards due to memory operands can be determined only after computing the effective address

| store | $M[(r1) + disp1] \leftarrow (r2)$ |

|-------|-----------------------------------|

| load  | $r3 \leftarrow M[(r4) + disp2]$   |

Does(r1) + disp1 == (r4) + disp2?

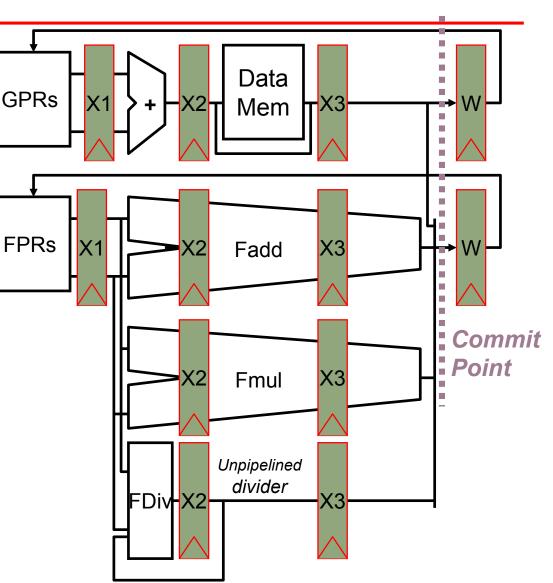

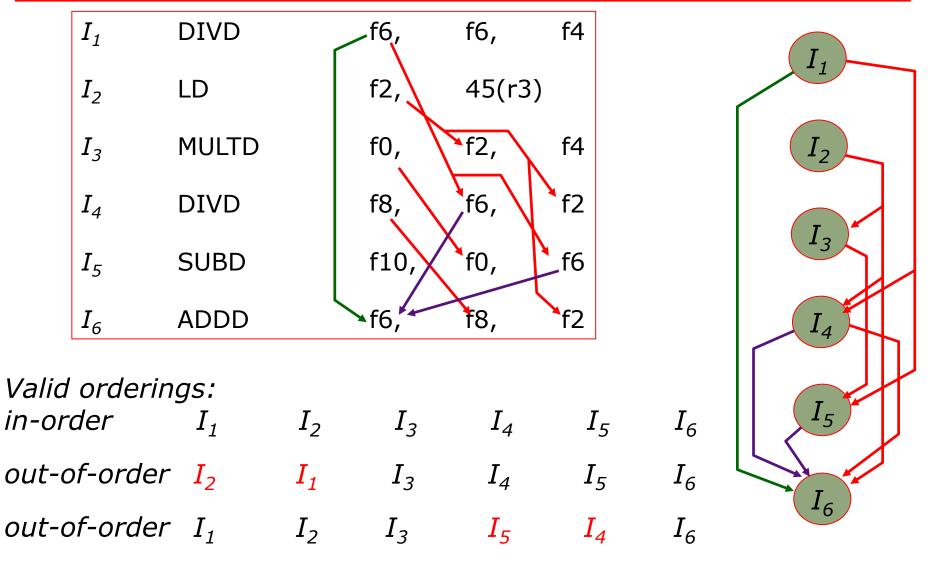

### Data Hazards: An Example

RAW Hazards WAR Hazards WAW Hazards

MIT 6.823 Spring 2021

### **Instruction Scheduling**

March 16, 2021

MIT 6.823 Spring 2021

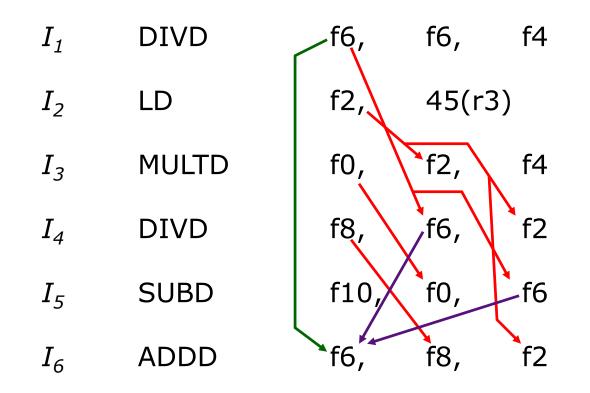

# Out-of-order Completion

|            |          |         |      |      |          |       |          |          |          |    |          |             |    | La       | ten | су       |          |

|------------|----------|---------|------|------|----------|-------|----------|----------|----------|----|----------|-------------|----|----------|-----|----------|----------|

|            | $I_1$    | DIVD    |      |      | f        | 6,    |          | f6,      |          | f4 |          |             |    |          | 4   | -        |          |

|            | $I_2$    | LD      |      |      | f        | 2,    |          | 45(      | (r3)     |    |          |             |    |          | 1   |          |          |

|            | $I_3$    | MULTD   |      |      | f        | 0,    |          | f2,      |          | f4 |          |             |    |          | 3   |          |          |

|            | $I_4$    | DIVD    |      |      | f        | 8,    |          | f6,      |          | f2 |          |             |    |          | 4   |          |          |

|            | $I_5$    | SUBD    |      |      | f        | 10,   |          | f0,      |          | f6 |          |             |    |          | 1   |          |          |

|            | $I_6$    | ADDD    |      |      | f        | 6,    |          | f8,      |          | f2 |          |             |    |          | 1   |          |          |

| cycle      |          |         | 1    | 2    | 3        | 4     | 5        | 6        | 7        | 8  | 9        | 10          | 11 | 12       | 13  | 14       | 15       |

| in-orde    | er comp  |         | 1    | 2    |          |       | <u>1</u> | <u>2</u> | 3        | 4  |          | <u>3</u>    | 5  | <u>4</u> | 6   | <u>5</u> | <u>6</u> |

| out-of-    | order co | тр      | 1    | 2    | <u>2</u> | 3     | <u>1</u> | 4        | <u>3</u> | 5  | <u>5</u> | <u>4</u>    | 6  | <u>6</u> |     |          |          |

| What p     | roblems  | can out | -of- | -orc | ler      | con   | пр о     | caus     | se?      |    |          | haz<br>ptio |    | ls       |     |          |          |

| rch 16 202 | 1        |         |      | м    | тε       | 272 0 | nrin     | a 202    | 1        |    |          |             |    |          |     |          | 108-2    |

March 16, 2021

MIT 6.823 Spring 2021

### Scoreboard: A Hardware Data Structure to Detect Hazards Dynamically

### **Complex Pipeline**

### When is it Safe to Issue an Instruction?

- Approach: Stall issue until sure that issuing will cause no dependence problems...

- Suppose a data structure keeps track of all the instructions in all the functional units

- The following checks need to be made before the Issue stage can dispatch an instruction

- Is the required function unit available?

- Is the input data available?  $\Rightarrow$  RAW?

- Is it safe to write the destination?  $\Rightarrow$  WAR? WAW?

- Is there a structural conflict at the WB stage?

### A Data Structure for Correct Issues Keeps track of the status of Functional Units

| Name  | Busy | Ор | Dest | Src1 | Src2 |

|-------|------|----|------|------|------|

| Int   |      |    |      |      |      |

| Mem   |      |    |      |      |      |

| Add1  |      |    |      |      |      |

| Add2  |      |    |      |      |      |

| Add3  |      |    |      |      |      |

| Mult1 |      |    |      |      |      |

| Mult2 |      |    |      |      |      |

| Div   |      |    |      |      |      |

The instruction i at the Issue stage consults this table

| FU available? | check the busy column                         |

|---------------|-----------------------------------------------|

| RAW?          | search the dest column for i's sources        |

| WAR?          | search the source columns for i's destination |

| WAW?          | search the dest column for i's destination    |

An entry is added to the table if no hazard is detected; An entry is removed from the table after Write-Back March 16, 2021 NIT 6.823 Spring 2021 L08-27

### Simplifying the Data Structure Assuming In-order Issue

- Suppose the instruction is not dispatched by the Issue stage

- If a RAW hazard exists

- or if the required FU is busy

- Suppose operands are latched by the functional unit on issue

Can the dispatched instruction cause a WAR hazard? NO: Operands read at issue

WAW hazard? YES: Out-of-order completion

# Simplifying the Data Structure

- No WAR hazard

⇒ no need to keep src1 and src2

- The Issue stage does not dispatch an instruction in case of a WAW hazard

$\Rightarrow$  a register name can occur at most once in the *dest* column

- WP[reg#]: a bit-vector to record the registers for which writes are pending

- These bits are set to true by the Issue stage and set to false by the WB stage

⇒ Each pipeline stage in the FU's must carry the *dest* field and a flag to indicate if it is valid "the (we, ws) pair"

### Scoreboard for In-order Issues

Busy[FU#] : a bit-vector to indicate FU's availability. (FU = Int, Add, Mult, Div) These bits are hardwired to FU's.

WP[reg#] : a bit-vector to record the registers for which writes are pending. These bits are set to true by the Issue stage and set to false by the WB stage

Issue checks the instruction (opcode dest src1 src2) against the scoreboard (Busy & WP) to dispatch

FU available? RAW? WAR? WAW?

Busy[FU#] WP[src1] or WP[src2] *cannot arise* WP[dest]

### **Scoreboard Dynamics**

|                                        |    |      | l Unit Status<br>(1) Mult(3) Div(4) WB |    |    |            |            |          |           |      | Registers Reserved<br>for Writes |

|----------------------------------------|----|------|----------------------------------------|----|----|------------|------------|----------|-----------|------|----------------------------------|

| t0 I <sub>1</sub>                      |    |      |                                        |    |    | f6         |            |          |           |      | f6                               |

| $t\overline{1} I_2$                    | f2 |      |                                        |    |    |            | <b>f6</b>  |          |           |      | <mark>f6,</mark> f2              |

| t2                                     |    |      |                                        |    |    |            |            | f6       |           | f2   | f6, f2 <u>I</u> 2                |

| t3 <i>I</i> 3                          |    |      | fO                                     |    |    |            |            |          | f6        |      | <mark>f6</mark> , f0             |

| t4                                     |    |      |                                        | f0 |    |            |            |          |           | f6   | f6, f0 <u>I</u> 1                |

| t5 <i>I</i> 4                          |    |      |                                        |    | fO | <b>f</b> 8 |            |          |           |      | f0, <mark>f8</mark>              |

| t <mark>6</mark>                       |    |      |                                        |    |    |            | <b>f</b> 8 |          |           | fO   | f0, f8 <u>I</u> <sub>3</sub>     |

| t7 <i>I</i> <sub>5</sub>               |    | f10  |                                        |    |    |            |            | f8       |           |      | <mark>f8</mark> , f10            |

| t8                                     |    |      |                                        |    |    |            |            |          | <b>f8</b> | f10  | f8, f10 <u>I</u> 5               |

| t9                                     |    |      |                                        |    |    |            |            |          |           | f8   | f8 <u>I</u> 4                    |

| t10 I <sub>6</sub>                     |    | f6   |                                        |    |    |            |            |          |           |      | f6                               |

| t11                                    |    |      |                                        |    |    |            |            |          |           | f6   | f6 <u>I</u> <sub>6</sub>         |

| $I_1$                                  |    |      |                                        |    |    |            |            |          |           | 4    |                                  |

| $egin{array}{c} I_2 \ I_3 \end{array}$ |    |      |                                        |    |    | 2,         |            |          | 5(r:      | -    |                                  |

| $I_3$                                  |    |      |                                        |    |    | ),<br>3,   |            | f2<br>f6 | -         |      | 2<br>2                           |

| $egin{array}{c} I_4 \ I_5 \end{array}$ |    | SUBD |                                        |    |    | 5,<br>10,  |            | f        | - T       |      | 6                                |

| $I_6$                                  |    | ADDD |                                        |    |    | 5,         |            | f8       | •         |      | 2                                |

| March 16, 202                          | 1  |      |                                        |    |    |            | .823       | 8 Sp     | ring      | 2021 |                                  |

L08-31

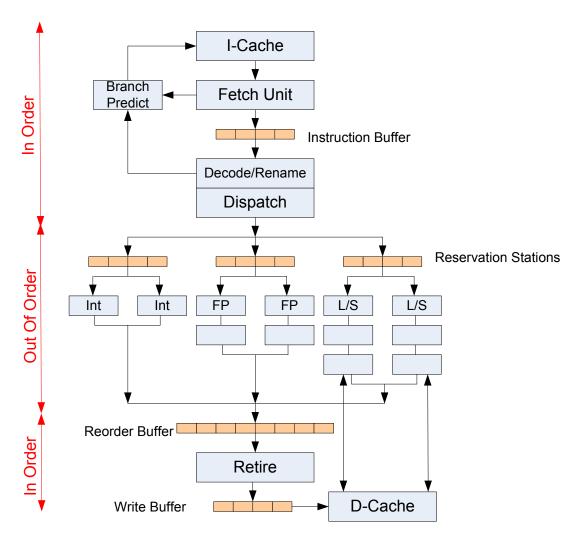

### Preview: Anatomy of a Modern Outof-Order Superscalar Core

- L08 (Today): Complex pipes w/ in-order issue

- L09: Out-of-order exec & renaming

- L10: Branch prediction

- L11: Speculative execution and recovery

- L12: Advanced Memory Ops