# **Problem M14.1: Microprogramming and Bus-Based Architectures**

#### Problem M14.1.A

**Memory-to-Memory Add**

Worksheet M14.1-1 shows one way to implement ADDm in microcode.

Note that to maintain "clean" behavior of your microcode, no registers in the register file should change their value during execution (unless they are written to). This does not refer to the registers in the datapath (IR, A, B, MA). Thus, using asterisks for the load signals (ldIR, ldA, ldB, and ldMA) is acceptable as long as the correctness of your microcode is not affected.

#### **Problem M14.1.B**

**Implementing DBNEZ Instruction**

The question asked to jump to PC+4+offset. This ignores that the immediate value needs to be shifted left by 2 before it can be added to PC+4, to make sure we don't run into alignment problems. We did this because the data path given doesn't really have facilities for shifting.

Worksheet M14.1-2 shows one way to implement DBNEZ in microcode.

#### **Problem M14.1.C**

**Implementing RETZ Instruction**

Worksheet M14.1-3 shows one way to implement RETZ in microcode.

#### Problem M14.1.D

**Implementing CALL Instruction**

Worksheet M14.1-4 shows one way to implement CALL in microcode.

#### Problem M14.1.E

**Instruction Execution Times**

| Instruction    |             | Cycles    |

|----------------|-------------|-----------|

| SUB R3,R2,R1   |             | 3 + 3 = 6 |

| SUBI R2,R1,#4  |             | 3 + 3 = 6 |

| SW R1,0(R2)    |             | 3 + 5 = 8 |

| BNEZ R1, label | # (R1 == 0) | 3 + 2 = 5 |

| BNEZ R1, label | # (R1 != 0) | 3 + 5 = 8 |

| BEQZ R1, label | # (R1 == 0) | 3 + 5 = 8 |

| BEQZ R1, label | # (R1 != 0) | 3 + 2 = 5 |

| J label        |             | 3 + 3 = 6 |

| JR R1          |             | 3 + 2 = 5 |

| JAL label      |             | 3 + 4 = 7 |

| JALR R1        |             | 3 + 4 = 7 |

As discussed in Lecture 21, instruction execution includes the number of cycles needed to fetch the instruction. The lecture notes used 4 cycles for the fetch phase, while Worksheet 1 shows that this phase can actually be implemented in 3 cycles —either answer is fine. The above table uses 3 cycles for the fetch phase. Overall, SW, BNEZ (for a taken branch), and BEQZ (for a taken branch) take the most cycles to execute (8), while BNEZ (for a not-taken branch) and JR take the fewest cycles (5).

| PseudoCode                    | Ld<br>IR                                                                                                                           | Reg<br>Sel                                                               | Reg<br>W                                                                                     | en<br>Rea                                                                                                            | ld<br>A                                                                       | ld B                                                                                    | ALUOp                                                                                | en<br>ALU                                                                       | ld<br>MA                                                                                         | Mem<br>W                              | en<br>Mem                                                                                                                                                                                                                                           | Ex<br>Sel                                                                                                                         | en<br>Imm                                                                                                                                     | μBr                                                                                                                                                       | Next State                 |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| MA <- PC; A <- PC             | 0                                                                                                                                  | PC                                                                       | 0                                                                                            | 1                                                                                                                    | 1                                                                             | *                                                                                       | *                                                                                    | 0                                                                               | 1                                                                                                | *                                     | 0                                                                                                                                                                                                                                                   | *                                                                                                                                 | 0                                                                                                                                             | N                                                                                                                                                         | *                          |

| IR <- Mem                     | 1                                                                                                                                  | *                                                                        | *                                                                                            | 0                                                                                                                    | 0                                                                             | *                                                                                       | *                                                                                    | 0                                                                               | *                                                                                                | 0                                     | 1                                                                                                                                                                                                                                                   | *                                                                                                                                 | 0                                                                                                                                             | N                                                                                                                                                         | *                          |

| PC <- A+4;<br>dispatch        | 0                                                                                                                                  | PC                                                                       | 1                                                                                            | 1                                                                                                                    | *                                                                             | *                                                                                       | INC_A_4                                                                              | 1                                                                               | *                                                                                                | *                                     | 0                                                                                                                                                                                                                                                   | *                                                                                                                                 | 0                                                                                                                                             | D                                                                                                                                                         | *                          |

|                               |                                                                                                                                    |                                                                          |                                                                                              |                                                                                                                      |                                                                               |                                                                                         |                                                                                      |                                                                                 |                                                                                                  |                                       |                                                                                                                                                                                                                                                     |                                                                                                                                   |                                                                                                                                               |                                                                                                                                                           |                            |

| microbranch<br>Back to FETCH0 | 0                                                                                                                                  | *                                                                        | *                                                                                            | 0                                                                                                                    | *                                                                             | *                                                                                       | *                                                                                    | 0                                                                               | *                                                                                                | *                                     | 0                                                                                                                                                                                                                                                   | *                                                                                                                                 | 0                                                                                                                                             | J                                                                                                                                                         | FETCH0                     |

|                               |                                                                                                                                    |                                                                          |                                                                                              |                                                                                                                      |                                                                               |                                                                                         |                                                                                      |                                                                                 |                                                                                                  |                                       |                                                                                                                                                                                                                                                     |                                                                                                                                   |                                                                                                                                               |                                                                                                                                                           |                            |

| MA <- R[rs]                   | 0                                                                                                                                  | rs                                                                       | 0                                                                                            | 1                                                                                                                    | *                                                                             | *                                                                                       | *                                                                                    | 0                                                                               | 1                                                                                                | *                                     | 0                                                                                                                                                                                                                                                   | *                                                                                                                                 | 0                                                                                                                                             | N                                                                                                                                                         | *                          |

| A <- Mem                      | 0                                                                                                                                  | *                                                                        | *                                                                                            | 0                                                                                                                    | 1                                                                             | *                                                                                       | *                                                                                    | 0                                                                               | *                                                                                                | 0                                     | 1                                                                                                                                                                                                                                                   | *                                                                                                                                 | 0                                                                                                                                             | N                                                                                                                                                         | *                          |

| MA <- R[rt]                   | 0                                                                                                                                  | rt                                                                       | 0                                                                                            | 1                                                                                                                    | 0                                                                             | *                                                                                       | *                                                                                    | 0                                                                               | 1                                                                                                | *                                     | 0                                                                                                                                                                                                                                                   | *                                                                                                                                 | 0                                                                                                                                             | N                                                                                                                                                         | *                          |

| B <- Mem                      | 0                                                                                                                                  | *                                                                        | *                                                                                            | 0                                                                                                                    | 0                                                                             | 1                                                                                       | *                                                                                    | 0                                                                               | *                                                                                                | 0                                     | 1                                                                                                                                                                                                                                                   | *                                                                                                                                 | 0                                                                                                                                             | N                                                                                                                                                         | *                          |

| MA <- R[rd]                   | *                                                                                                                                  | rd                                                                       | 0                                                                                            | 1                                                                                                                    | 0                                                                             | 0                                                                                       | *                                                                                    | 0                                                                               | 1                                                                                                | *                                     | 0                                                                                                                                                                                                                                                   | *                                                                                                                                 | 0                                                                                                                                             | N                                                                                                                                                         | *                          |

| Mem <- A+B; fetch             | *                                                                                                                                  | *                                                                        | *                                                                                            | 0                                                                                                                    | *                                                                             | *                                                                                       | ADD                                                                                  | 1                                                                               | *                                                                                                | 1                                     | 1                                                                                                                                                                                                                                                   | *                                                                                                                                 | 0                                                                                                                                             | J                                                                                                                                                         | FETCH0                     |

|                               |                                                                                                                                    |                                                                          |                                                                                              |                                                                                                                      |                                                                               |                                                                                         |                                                                                      |                                                                                 |                                                                                                  |                                       |                                                                                                                                                                                                                                                     |                                                                                                                                   |                                                                                                                                               |                                                                                                                                                           |                            |

|                               | MA <- PC; A <- PC IR <- Mem PC <- A+4; dispatch  microbranch Back to FETCH0  MA <- R[rs] A <- Mem MA <- R[rt] B <- Mem MA <- R[rd] | IR   MA <- PC; A <- PC   0   IR <- Mem   1   PC   <- A+4;   0   dispatch | IR   Sel   MA <- PC; A <- PC   0   PC   IR <- Mem   1   *   PC   <- A+4;   0   PC   dispatch | IR   Sel   W     MA <- PC; A <- PC   0   PC   0     IR <- Mem   1   *   *     PC   <- A+4;   0   PC   1     dispatch | IR   Sel   W   Reg   MA <- PC; A <- PC   0   PC   0   1     IR <- Mem   1   * | IR   Sel   W   Reg   A     MA <- PC; A <- PC   0   PC   0   1   1     IR <- Mem   1   * | IR         Sel         W         Reg         A         B           MA <- PC; A <- PC | IR   Sel   W   Reg   A   B   MA <- PC; A <- PC   0   PC   0   1   1   *   *   * | IR         Sel         W         Reg         A         B         ALU           MA <- PC; A <- PC | IR   Sel   W   Reg   A   B   ALU   MA | IR   Se    W   Reg   A   B   ALU   MA   W     MA <- PC; A <- PC   0   PC   0   1   1   *   *   *   0   1   *     IR <- Mem   1   *   *   0   0   *   *   0   0   *     PC   <- A+4;   0   PC   1   1   *   *   *   INC_A_4   1   *   *     dispatch | IR         Sel         W         Reg         A         B         ALU         MA         W         Mem           MA <- PC; A <- PC | IR         Sel         W         Reg         A         B         ALU         MA         W         Mem         Sel           MA <- PC; A <- PC | IR         Sel         W         Reg         A         B         ALU         MA         W         Mem         Sel         Imm           MA <- PC; A <- PC | IR   Sel   W   Reg   A   B |

Worksheet M14.1-1: Implementation of the ADDm instruction

| State   | PseudoCode                             | ld<br>IR | Reg<br>Sel | Reg<br>W | en<br>Reg | ld<br>A | ld<br>B | ALUOp   | en<br>ALU | Ld<br>MA | Mem<br>W | en<br>Mem | Ex<br>Sel | en<br>Imm | μBr | Next State |

|---------|----------------------------------------|----------|------------|----------|-----------|---------|---------|---------|-----------|----------|----------|-----------|-----------|-----------|-----|------------|

| FETCH0: | MA <- PC;<br>A <- PC                   | *        | PC         | 0        | 1         | 1       | *       | *       | 0         | 1        | *        | 0         | *         | 0         | N   | *          |

|         | IR <- Mem                              | 1        | *          | *        | 0         | 0       | *       | *       | 0         | *        | 0        | 1         | *         | 0         | Ν   | *          |

|         | PC <- A+4;<br>B <- A+4                 | 0        | PC         | 1        | 1         | *       | 1       | INC_A_4 | 1         | *        | *        | 0         | *         | 0         | D   | *          |

|         |                                        |          |            |          |           |         |         |         |           |          |          |           |           |           |     |            |

| NOP0:   | microbranch<br>back to FETCH0          | *        | *          | *        | 0         | *       | *       | *       | 0         | *        | *        | 0         | *         | 0         | J   | FETCH0     |

| DBNEZ:  | A <- rs                                | 0        | rs         | 0        | 1         | 1       | 0       | *       | 0         | *        | *        | 0         | *         | 0         | N   | *          |

|         | rs <- A – 1<br>μB to FETCH0 if<br>zero | 0        | rs         | 1        | 1         | *       | 0       | DEC_A_1 | 1         | *        | *        | 0         | *         | 0         | Z   | FETCH0     |

|         | A <- sExt16(IR)                        | *        | *          | *        | 0         | 1       | 0       | *       | 0         | *        | *        | 0         | sExt16    | 1         | N   | *          |

|         | PC <- A+B<br>jump to<br>FETCH0         | *        | PC         | 1        | 1         | *       | *       | ADD     | 1         | *        | *        | 0         | *         | 0         | J   | FETCH0     |

|         |                                        |          |            |          |           |         |         |         |           |          |          |           |           |           |     |            |

Worksheet M14.1-2: Implementation of the DBNEZ Instruction

| State   | PseudoCode                                      | Ld<br>IR | Reg<br>Sel | Reg<br>W | en<br>Reg | ld<br>A | ld<br>B | ALUOp   | en<br>ALU | Ld<br>MA | Mem<br>W | en<br>Mem | Ex<br>Sel | en<br>Im<br>m | μBr | Next State |

|---------|-------------------------------------------------|----------|------------|----------|-----------|---------|---------|---------|-----------|----------|----------|-----------|-----------|---------------|-----|------------|

| FETCH0: | MA <- PC;<br>A <- PC                            | *        | PC         | 0        | 1         | 1       | *       | *       | 0         | 1        | *        | 0         | *         | 0             | N   | *          |

|         | IR <- Mem                                       | 1        | *          | *        | 0         | 0       | *       | *       | 0         | *        | 0        | 1         | *         | 0             | N   | *          |

|         | PC <- A+4;<br>B <- A+4                          | 0        | PC         | 1        | 1         | *       | 1       | INC_A_4 | 1         | *        | *        | 0         | *         | 0             | D   | *          |

|         |                                                 |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

| NOP0:   | microbranch<br>back to FETCH0                   | *        | *          | *        | 0         | *       | *       | *       | 0         | *        | *        | 0         | *         | 0             | J   | FETCH0     |

| retz0   | A <- Reg[Rs]                                    | 0        | Rs         | 0        | 1         | 1       | *       | *       | 0         | *        | *        | 0         | *         | 0             | N   | *          |

| retz1   | A <- Reg[Rt] MA <- Reg[Rt] uBr to retz3 if zero | 0        | Rt         | 0        | 1         | 1       | *       | COPY_A  | 0         | 1        | *        | 0         | *         | 0             | Z   | retz3      |

| retz2   |                                                 | *        | *          | *        | 0         | *       | *       | *       | 0         | *        | *        | 0         | *         | 0             | J   | FETCH0     |

| retz3   | PC <- MEM                                       | 0        | PC         | 1        | 1         | 0       | *       | *       | 0         | *        | 0        | 1         | *         | 0             | N   | *          |

| retz4   | Reg[Rt] < A+4                                   | *        | Rt         | 1        | 1         | *       | *       | INC_A_4 | 1         | *        | *        | 0         | *         | 0             | J   | FETCH0     |

|         |                                                 |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

|         |                                                 |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

|         |                                                 |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

|         |                                                 |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

|         |                                                 |          |            |          |           |         |         |         |           |          |          |           |           |               |     |            |

Worksheet M14.1-3: Implementation of the RETZ Instruction

| State   | PseudoCode                    | ld<br>IR | Reg<br>Sel | Reg<br>W | en<br>Reg | ld<br>A | ld<br>B | ALUOp   | en<br>ALU | Ld<br>MA | Mem<br>W | en<br>Me<br>m | Ex<br>Sel | en<br>Imm | μBr | Next State |

|---------|-------------------------------|----------|------------|----------|-----------|---------|---------|---------|-----------|----------|----------|---------------|-----------|-----------|-----|------------|

| FETCH0: | MA <- PC;<br>A <- PC          | *        | PC         | 0        | 1         | 1       | *       | *       | 0         | 1        | *        | 0             | *         | 0         | N   | *          |

|         | IR <- Mem                     | 1        | *          | *        | 0         | 0       | *       | *       | 0         | *        | 0        | 1             | *         | 0         | N   | *          |

|         | PC <- A+4;<br>B <- A+4        | 0        | PC         | 1        | 1         | *       | 1       | INC_A_4 | 1         | *        | *        | 0             | *         | 0         | D   | *          |

|         |                               |          |            |          |           |         |         |         |           |          |          |               |           |           |     |            |

| NOP0:   | microbranch<br>back to FETCH0 | *        | *          | *        | 0         | *       | *       | *       | 0         | *        | *        | 0             | *         | 0         | J   | FETCH0     |

| CALL:   | MA <- R[ra];<br>A <- R[ra]    | 0        | ra         | 0        | 1         | 1       | 0       | *       | 0         | 1        | *        | 0             | *         | 0         | N   | *          |

|         | Mem <- B                      | 0        | *          | *        | 0         | 0       | 0       | COPY_B  | 1         | *        | 1        | 1             | *         | 0         | N   | *          |

|         | R[ra] <- A - 4                | 0        | ra         | 1        | 1         | *       | 0       | DEC_A_4 | 1         | *        | *        | 0             | *         | 0         | N   | *          |

|         | A <- sExt16(IR)               | *        | *          | *        | 0         | 1       | 0       | *       | 0         | *        | *        | 0             | sExt16    | 1         | N   | *          |

|         | PC <- A+B;<br>jump to FETCH0  | *        | РС         | 1        | 1         | *       | *       | ADD     | 1         | *        | *        | 0             | *         | 0         | J   | FETCH0     |

|         |                               |          |            |          |           |         |         |         |           |          |          |               |           |           |     |            |

|         |                               |          | (7 1 1     |          |           |         |         |         | 1 64      |          |          |               |           |           |     |            |

Worksheet M14.1-4: Implementation of the CALL Instruction

Problem M14.1.F Exponentiation

In the given code, 'm' and 'n' are always nonnegative integers. Therefore, we don't have to worry about the cases where 'i' is larger than 'n' or 'j' is larger than 'm'. Also, for this problem, 0 raised to any power is just 0, while any nonzero value raised to the  $0^{th}$  power is 1. Note that the pseudo code that is given returns a value of 0 when 0 is raised to the  $0^{th}$  power. However, the actual pow() function in the standard C library returns a value of 1 for this case. We present the solution that implements the pseudo code given in the problem rather than C's pow() function.

```

# R5: temp, R6: j

R3, R0, R0

ADD

; put 0 in result

R1, END I

; if m is 0, end

BEQZ

R3, R0, #1

; put 1 in result

ADDI

R2, END I

; if n is 0, the loop is over; we set

BEQZ

; i equal to n and count down to 0-since

; R2 does not have to be preserved, we

; use it for i

SUBI

R5, R1, #1

; temp = m - 1

R5, _END I

; if m is 1, the result will be 1,

BEQZ

; so end the program

_START_I:

R5, R0, R3

ADD

; temp = result

R6, R1, #1

; j = m - 1 (the number of times to

SUBI

; execute the second loop)

START J:

R3, R3, R5

ADD

; result += temp

SUBI

R6, R6, #1

; j--

R6, START J

; Re-execute loop until j reaches 0

BNEZ

END J:

R2, R2, #1

SUBI

; i--

BNEZ

R2, _START_I

; Re-execute loop until i reaches 0

END I:

```

To compute the number of instructions and cycles to execute this code, let us consider subsets of the code.

|           | Code         | # of instructions           | # of cycles                                                   |

|-----------|--------------|-----------------------------|---------------------------------------------------------------|

| ADD       | R3, R0, R0   | 2                           | $6 \times 1 + 8 \times 1 = 14 \text{ (m = 0)}$                |

| BEQZ      | R1, _END_I   |                             | $6 \times 1 + 5 \times 1 = 11 \text{ (m > 0)}$                |

| ADDI      | R3, R0, #1   | 2 (if m > 0)                | $6 \times 1 + 8 \times 1 = 14 $ (n = 0)                       |

| BEQZ      | R2, _END_I   |                             | $6 \times 1 + 5 \times 1 = 11 \ (n > 0)$                      |

| SUBI      | R5, R1, #1   | 2 (if $m > 0$ and $n > 0$ ) | $6 \times 1 + 8 \times 1 = 14 \text{ (m = 1)}$                |

| BEQZ      | R5, _END_I   |                             | $6 \times 1 + 5 \times 1 = 11 \text{ (m > 1)}$                |

| _START_I: |              |                             |                                                               |

| ADD       | R5, R0, R3   | 2n  (if  m > 1  and  n > 0) | $(6\times2)\times n = 12n$                                    |

| SUBI      | R6, R1, #1   | <b> </b>                    |                                                               |

| _START_J: |              |                             |                                                               |

| ADD       | R3, R3, R5   | 3n(m-1)                     | $(6\times2+5\times1)\times n + (6\times2+8\times1)\times (m-$ |

| SUBI      | R6, R6, #1   | (if m > 1 and n > 0)        | $2)\times n = 17n + 20n(m-2)$                                 |

| BNEZ      | R6, START J  |                             |                                                               |

| _END_J:   |              |                             |                                                               |

| SUBI      | R2, R2, #1   | 2n  (if  m > 1  and  n > 0) | $(6+8)\times n-3=14n-3$                                       |

| BNEZ      | R2, _START_I |                             |                                                               |

From the above table, we can complete the table given in the problem.

| m,n                 | Instructions | Cycles          |

|---------------------|--------------|-----------------|

| 0, 1                | 2            | 14              |

| 1, 0                | 4            | 25              |

| 2, 2                | 20           | 116             |

| 3, 4                | 46           | 282             |

| M, N (M = 0)        | 2            | 14              |

| M, N (M > 0, N = 0) | 4            | 25              |

| M, N (M = 1, N > 0) | 6            | 36              |

| M, N (M > 1, N > 0) | 3N(M-1)+4N+6 | 20N(M-2)+43N+30 |

## Problem M14.1.G

# **Microcontroller Jump Logic**

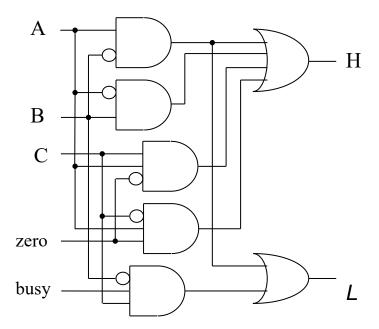

One way to start designing the microcontroller jump logic is to write out a table of the input signals and the output bits. For clarity, the bits that encode the µJumpTypes are labeled A, B and C, from left to right. The output bits are labeled H and L, also from left to right. So the table we need to implement is the following (where asterisks are for the input bits that we don't care about).

| Input bits |   |   | Output bits |      |   |   |

|------------|---|---|-------------|------|---|---|

| A          | В | С | Zero        | Busy | Н | L |

| 0          | 0 | 0 | *           | *    | 0 | 0 |

| 0          | 0 | 1 | *           | 0    | 0 | 0 |

| 0          | 0 | 1 | *           | 1    | 0 | 1 |

| 0          | 1 | 0 | *           | *    | 1 | 0 |

| 1          | 0 | 0 | *           | *    | 1 | 1 |

| 1          | 1 | 0 | 0           | *    | 0 | 0 |

| 1          | 1 | 0 | 1           | *    | 1 | 0 |

| 1          | 1 | 1 | 0           | *    | 1 | 0 |

| 1          | 1 | 1 | 1           | *    | 0 | 0 |

Writing out boolean equations for the H and L output bits (by directly recognizing only the lines which have logical ones as output) we find

$$H = A\overline{BC} + \overline{ABC} + AB\overline{C} \cdot zero + ABC \cdot \overline{zero}$$

$$L = \overline{ABC} \cdot busy + A\overline{BC}$$

Also, we do not care about the output when the  $\mu$ Jump type is 011 or 101, since those are invalid encodings. Thus we can simplify the equations to

$$H = A\overline{B} + \overline{AB} + A\overline{C} \cdot zero + AC \cdot \overline{zero}$$

$$L = \overline{BC} \cdot busy + A\overline{B}$$

Drawing this out as gates we get

# **Problem M14.2: VLIW Programming**

#### Problem M14.2.A

To get 1 cycle per vector element performance, we need to use loop unrolling and software pipelining. The original loop is unrolled four times and software pipelined. Two registers (**F3** and **F7**) are used for saving partial sums, which are summed at the end.

At the start of the program n may be any value. By making successive checks and providing fixup code, n can be guaranteed to be positive and a multiple of 4 by the prolog.

```

// R1 - points to X

// R2 - points to Y

// R5 - n

// F7 - result

// clear partial sum registers

MOVI2FP F3, R0

MOVI2FP F7, R0

// clear temporary registers used for multiply results

MOVI2FP F2, R0

MOVI2FP F6, R0

MOVI2FP F10,R0

MOVI2FP F14,R0

// n must be greater than 0

SGT R3, R5, R0

BEQZ

R3,end

// if !(n>0) goto end

// n must be greater than 0

ANDI R3, R5, #3

BEQZ R3, prolog

// (n>0) && ((n%4)!=0)

SUB R5, R5, R3

L1:

L.S F3,0(R1); L.S F4,0(R2); SUBI R3,R3,#1

MUL.S F3, F3, F4; ADDI R1, R1, #4;

ADD.S F7, F7, F3; ADDI R2, R2, #4; BNEZ R3, L1

BEQZ R5, end

// (n>=4) && ((n%4)==0)

prolog:

L.S F0, 0(R1); L.S F1, 0(R2); SUBI R5,R5,#4

L.S F4, 4(R1); L.S F5, 4(R2); ADDI R1,R1,#16

L.S F8,-8(R1); L.S F9, 8(R2); ADDI R2,R2,#16

L.S F12,-4(R1); L.S F13,-4(R2); BEQZ R5,epilog

L.S F0, O(R1); L.S F1, O(R2); MUL.S F2, F0, F1; SUBI R5, R5, #4

L.S F4, 4(R1); L.S F5, 4(R2); MUL.S F6, F4, F5; ADDI R1,R1,#16

L.S F8,-8(R1); L.S F9, 8(R2); MUL.S F10, F8, F9; ADDI R2,R2,#16

L.S F12,-4(R1); L.S F13,-4(R2); MUL.S F14,F12,F13; BEQZ R5,epilog

```

```

loop:

L.S F0, 0(R1); L.S F1, 0(R2); MUL.S F2, F0, F1; ADD.S F3,F3, F2; SUBI R5,R5,#4

L.S F4, 4(R1); L.S F5, 4(R2); MUL.S F6, F4, F5; ADD.S F7,F7, F6; ADDI R1,R1,#16

L.S F8,-8(R1); L.S F9, 8(R2); MUL.S F10, F8, F9; ADD.S F3,F3,F10; ADDI R2,R2,#16

L.S F12,-4(R1); L.S F13,-4(R2); MUL.S F14,F12,F13; ADD.S F7,F7,F14; BNEZ R5,loop

epilog:

MUL.S F2, F0, F1; ADD.S F3,F3, F2

MUL.S F6, F4, F5; ADD.S F7,F7, F6

MUL.S F10, F8, F9; ADD.S F3,F3,F10

MUL.S F14,F12,F13; ADD.S F7,F7,F14

ADD.S F3,F3, F2

ADD.S F3,F3,F10

ADD.S F7,F7,F14

ADD.S F7,F7,F3

end:

```

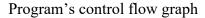

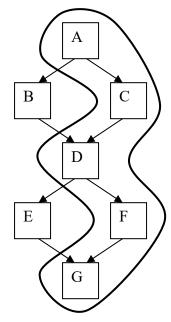

# **Problem M14.3: Trace Scheduling**

## Problem M14.3.A

# Decision tree

#### **Problem M14.3.B**

```

ACF: 1d

r1, data

div

r3, r6, r7 ;; X <- V2/V3

mul r8, r6, r7 ;; Y <- V2*V3

D:

andi r2, r1, 3 ;; r2 <- r1%4

bnez r2, G

andi r2, r1, 7 ;; r2 <- r1%8

A:

bnez r2, E

div r3, r4, r5 ;; X \leftarrow V0/V1

B:

E:

mul

r8, r4, r5 ;; Y <- V0*V1

G:

```

## Problem M14.3.C

Assume that the load takes x cycles, divide takes y cycles, and multiply takes z cycles. Approximately how many cycles does the original code take? (ignore small constants)

# x+max(y,z)

Approximately how many cycles does the new code take in the best case? max(x,y,z)

## **Problem M14.4: VLIW machines**

## Problem M14.4.A

See **Table M14.4-1** on the next page.

#### **Problem M14.4.B**

12 cycles, 2/12=0.17 flops per cycle

#### **Problem M14.4.C**

3 instructions, because there are 5 memory ops and 5 ALU ops, and we can only issue 2 of them per instruction. (OR 4 instructions, because the slowest operation has a 4-cycle latency.)

Here is the resulting code.

| add r1, r1, 4 | add r2, r2, 4  | ld f1, 0(r1)  | ld f2, 0(r2)   |                 | fmul f4, f2, f1 |

|---------------|----------------|---------------|----------------|-----------------|-----------------|

| add r3, r3, 4 | add r4, r4, -1 | ld f3, -4(r3) | st f4, -8(r1)  | fadd f5, f4, f3 |                 |

|               | bnez r4, loop  |               | st f5, -12(r3) |                 |                 |

for a particular instruction, white background corresponds to first iteration of the loop, grey background to the second iteration, yellow background to third, and blue to fourth. Note, one does not need to write the code to get an answer, because it's just a question of how many instructions are needed to express all the operations.

#### Problem M14.4.D

2/3=0.67 flops per cycle, 4 iterations at a time.

| ALU1          | ALU2           | MU1           | MU2           | FADD            | FMUL            |

|---------------|----------------|---------------|---------------|-----------------|-----------------|

| add r1, r1, 4 | add r2, r2, 4  | ld f1, 0(r1)  | ld f2, 0(r2)  |                 |                 |

| add r3, r3, 4 | add r4, r4, -1 | ld f3, 0(r3)  |               |                 |                 |

|               |                |               |               |                 |                 |

|               |                |               |               |                 | fmul f4, f2, f1 |

|               |                |               |               |                 |                 |

|               |                |               |               |                 |                 |

|               |                |               |               |                 |                 |

|               |                |               | st f4, -4(r1) | fadd f5, f4, f3 |                 |

|               |                |               |               |                 |                 |

|               |                |               |               |                 |                 |

|               |                |               |               |                 |                 |

|               | bnez r4, loop  | st f5, -4(r3) |               |                 |                 |

|               |                |               |               |                 |                 |

|               |                |               |               |                 |                 |

|               |                |               |               |                 |                 |

Table M14.4-1: VLIW Program

# Problem M14.4.E

We would need 5 instructions to execute two iterations and we would get 4/5=0.8 flops/cycle.

### Problem M14.4.F

Same as above - 0.8 flops/cycle. We are fully utilizing the memory units, so we can't execute more loops/cycle.

## Problem M14.4.G

No. We need to unroll the loop once to have an even number of memory ops. Use of the rotating registers would not allow us to squeeze in more memory ops per iteration, so we'd still need 5 instructions.

#### **Problem M14.4.H**

This is actually rather tricky. The correct answer is 5, because without interlocks, we can use the registers just as values come in for them, using the execution units to "store" the loops. The intuitive answer is 100 though.

### Problem M14.4.I

There are approximately 100 instructions required, because maximum latency will be 100 cycles.

# **Problem M14.5: VLIW & Vector Coding**

Ben Bitdiddle has the following C loop, which takes the absolute value of elements within a vector.

```

for (i = 0; i < N; i++) {

if (A[i] < 0)

A[i] = -A[i];

}</pre>

```

#### Problem M14.5.A

```

; Initial Conditions:

R1 = N

R2 = &A[0]

SGT R3, R1, R0

BEQZ R3, end

; R3 = (N > 0) | special case N \le 0

SUBI R1, R1, #1

loop: LW R4, 0(R2)

; R4 = A[i] | N--

SLT R5, R4, R0

ADDI R2, R2, #4

; R5 = (A[i] < 0) \mid R2 = &A[i+1]

BEQZ R5, next

; skip if (A[i]≥0)

SUB R4, R0, R4

; A[i] = -A[i]

SW R4, -4 (R2)

; store updated value of A[i]

next: BNEZ R1, loop

; continue if N > 0

end:

Average Number of Cycles: \frac{1}{2} \times (6 + 4) = 5

; SOLUTION #2

SGT R3, R1, R0

BNEZ R3, end

; R3 = (N > 0) | special case N \le 0

SUBI R1, R1, #1

loop: LW R4, 0(R2)

; R4 = A[i] \mid N--

ADDI R2, R2, #4

SLT R5, R4, R0

; R5 = (A[i] < 0) \mid R2 = &A[i+1]

SUB R4, R0, R4

BNEZ R5, next

; skip if (A[i] \ge 0) \mid A[i] = -A[i]

SW R4, -4(R2)

; store updated value of A[i]

next: BNEZ R1, loop

; continue if N > 0

end:

```

Average Number of Cycles:  $\frac{1}{2} \times (5+4) = 4.5$

NOTE: Although this solution minimizes code size and average number of cycles per element for this loop, it causes extra work because it subtracts regardless of whether it has to or not.

Average Number of Cycles:  $\frac{1}{2} \times (4 + 4) = 4$  Cycles

## **Problem M14.5.C**

```

; Initial Conditions:

R1 = N

R2 = &A[i]

R3 = N > 0

R4 = A[i]

R5 = N \text{ odd}

R6 = A[i+1]

SGT R3, R1, R0

BEQZ R3, end

ANDI R5, R1, #1

BEQZ R5, loop

LW R4, 0(R2)

CMPLTZ PO, R4

SUBI R1, R1, #1

ADDI R2, R2, #4

(P0) SUB R4, R0, R4

(P0) SW R4, -4(R2)

BEZ R1, end

loop: LW R4, 0(R2)

SUBI R1, R1, #2

CMPLTZ PO, R4

LW R6, 4(R2)

(P0) SUB R4, R0, R4

CMPLTZ P1, R6

(P0) SW R4, 0(R2)

(P1) SUB R6 R0, R6

(P1) SW R6 4(R2)

ADDI R2, R2, #8

BNEZ R1, loop

end:

```

Average Number of Cycles: 6 for 2 elements = 3 cycles per element

```

; Initial Conditions:

; R1 = N

; R2 = &A[i]

L.D F0, #0

MTC1 VLR R1  # operate on all N elements

CVM

LV V1, R2  # load A

SLTVS.D V1, F0  # setup the mask vector

SUBSV.D V1, F0, V1  # negate appropriate elements

SV R2, V1  # store back changes

```

Average Number of Cycles:  $\approx (N/2 + N/2) / N \approx 1$  cycle per element (assuming chaining)

Note: Because there is only one ALU per lane, only the load and the SLT (Set-Less-Than) can be chained together, while the subtract and the store can be chained together. Execution time (per element) of the other instructions is negligible when N is large.

#### **Problem M14.5.E**

```

; assume m = known vector length

; Initial Conditions:

R1 = N

R2 = &A[i]

L.D F0, #0

ANDI R3, R1, (m-1)

# get N%m - assume m is a power of 2

MTC1 VLR R3

# operate on first N%m elements

# load A

LV V1, R2

SLTVS.D V1, F0 # setup the mask vector SUBSV.D V1, F0, V1 # negate appropriate elements

# store back changes

# decrease i by N%m (i is divisible by m now)

# (we're counting i down)

SV R2, V1

SUB R1, R1, R3

SLLI R3, R3, #2

ADDI R2, R2, R3

# advance A pointer

# i == 0 -> done

BEQZ R1, end

ADDI R3, R0, m

MTC1 VLR R3

# operate on all elements

loop:

CVM

LV V1, R2

# load A

SLTVS.D V1, F0 # setup the mask vector

SUBSV.D V1, F0, V1 # negate appropriate elements

SV R2, V1 # store below

# advance A pointer

ADDI R2, R2, (m*4)

SUBI R1, R1, m

# decrease i by m

BNEZ R1, loop

# done?

```

end:

CVM

# **Problem M14.6: Predication and VLIW**

## Problem M14.6.A

```

1.s f1, 0(r1) ; f1 = *r1

seq.s r5, f10, f1 ; r5 = (f10==f1)

cmpnez p1, r5 ; p1 = (r5!=0)

(p1) add.s f2, f1, f11 ; if (p1) f2 = f1+f11

(!p1) add.s f2, f1, f12 ; if(!p1) f2 = f1+f12

s.s f2, 0(r2) ; *r2 = f2

```

# Problem M14.6.B

See the next page (Table M14.6-2).

| Label | integer op      | floating point add    | memory op           | branch            |

|-------|-----------------|-----------------------|---------------------|-------------------|

| loop: |                 |                       | 1.s f1,0(r1)        |                   |

|       |                 |                       | 1.s f3,4(r1)        |                   |

|       | addi r1, r1, #8 | cmpnez p1, f1         |                     |                   |

|       |                 | cmpnez p3, f3         |                     |                   |

|       |                 | (p1) add.s f2, f1, f1 |                     |                   |

|       |                 | (p3) add.s f4, f3, f3 |                     |                   |

|       |                 |                       | (p1) s.s f2, -8(r1) |                   |

|       |                 |                       | (p3) s.s f4, -4(r1) | bneq r1, r2, loop |

# **Table M14.6-1**

| label   | integer op      | floating point add    | memory op            | branch             |

|---------|-----------------|-----------------------|----------------------|--------------------|

|         |                 |                       | 1.s f1,0(r1)         |                    |

|         |                 |                       | 1.s f3,4(r1)         |                    |

|         | addi r1, r1, #8 | cmpnez p1, f1         |                      |                    |

|         |                 | cmpnez p3, f3         |                      | beq r1, r2, epilog |

| loop:   |                 | (p1) add.s f2, f1, f1 | 1.s f1,0(r1)         |                    |

|         |                 | (p3) add.s f4, f3, f3 | 1.s f3,4(r1)         |                    |

|         | addi r1, r1, #8 | cmpnez p1, f1         | (p1) s.s f2, -8(r1)  |                    |

|         |                 | cmpnez p3, f3         | (p3) s.s f4, -12(r1) | bneq r1, r2,loop   |

| epilog: |                 | (p1) add.s f2, f1, f1 |                      |                    |

|         |                 | (p3) add.s f4, f3, f3 |                      |                    |

|         |                 |                       | (p1) s.s f2, -8(r1)  |                    |

|         |                 |                       | (p3) s.s f2, -4(r1)  |                    |

**Table M14.6-2**

## **Problem M14.7: Vector Machines**

#### **Problem M14.7.A**

Consider the implementation of the C-code on the vector machine that executes in a minimum number of cycles. Assuming the following initial values, insert vector instructions to complete the implementation.

- o R1 points to A[0]

- o R2 points to B[0]

- o R3 points to C[0]

- o R4 contains the value 328

```

# 328 mod 32

ANDI R5, R4, 31

MTC1 VLR, R5

# set VLR to remainder

loop:

LV

V1, R1

# load A

LV

V2, R2

# load B

V3, R3

LV

# load C

MULV V4, V2, V1

# A * B

ADDV V5, V3, V4

#C+A

SV

# store A

V4, R1

V5, R3

# store C

SV

SLL

R7, R5, 2

ADD R1, R1, R7

# increment A ptr

ADD R2, R2, R7

# increment B ptr

ADD R3, R3, R7

# increment C ptr

SUB R4, R4, R5

# update loop counter

# reset VLR to max

LI

R5, 32

MTC1 VLR, R5

BGTZ R4, loop

```

## Problem M14.7.B

The following **supplementary information** explains the diagram.

Scalar instructions execute in 5 cycles: fetch (F), decode (D), execute (X), memory (M), and writeback (W). A vector instruction is also fetched (F) and decoded (D). Then, it stalls (—) until its required vector functional unit is available. With no chaining, a dependent vector instruction stalls until the previous instruction finishes writing back ALL of its elements. A vector instruction is pipelined across all the lanes in parallel. For each element, the operands are read (R) from the vector register file, the operation executes on the load/store unit (M) or the ALU (X) or the MUL (Y), and the result is written back (W) to the vector register file. Assume that there is no structural conflict on the writeback port. A stalled vector instruction does not block a scalar instruction from executing.

$LV_1$  and  $LV_2$  refer to the first and second LV instructions in the loop.

|                 |              |   |   |   |     |   |     |   |   |   |      |    |        |     |      |            |    |    |    |    |        |        |           | le |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    |   |

|-----------------|--------------|---|---|---|-----|---|-----|---|---|---|------|----|--------|-----|------|------------|----|----|----|----|--------|--------|-----------|----|----|----|----|-----|-----|-----|----|----|----|----|-----|--------|--------|-------|----|------------|----|----|----|----|---|

| instr.          | 1            | 2 | 3 | _ | 5   | _ | _   | 7 |   | 9 | 10   | 11 | 12     | 2 1 | 3    | 14         | 15 | 16 | 17 | 18 | 3 19   | 9 2    | 20        | 21 | 22 | 23 | 24 | 25  | 5 2 | 6 2 | 27 | 28 | 29 | 30 | 31  | 3      | 2 3    | 3     | 34 | 35         | 36 | 37 | 38 | 39 | 4 |

| $LV_1$          | $\mathbb{F}$ | D | R | _ | 1 M | _ | -   |   |   |   |      |    |        |     |      |            |    |    |    |    |        |        |           |    |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    | L |

| $LV_1$          |              |   |   | R | M   | _ | _   |   |   | - | _    |    |        |     |      |            |    |    |    |    |        |        |           |    |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    | _ |

| $LV_1$          |              |   |   |   | R   | _ | _   |   |   | - | 4 W  | +  |        |     |      |            |    |    |    |    |        |        |           |    |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    | L |

| $LV_1$          |              |   |   |   |     | F | _   | _ |   | - | 3 M  | _  | _      |     |      |            |    |    |    |    |        |        |           |    |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    | L |

| $LV_2$          |              | F | D | _ | _   |   | _   | R |   | _ | 2 M. | _  | _      | _   |      |            |    |    |    |    |        |        |           |    |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    | _ |

| $LV_2$          |              |   |   |   |     |   |     |   | R | - | 1 M  | _  | _      | _   | -    |            |    |    |    |    |        |        |           |    |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    | L |

| $LV_2$          |              |   |   |   |     |   |     |   |   | R | M    | _  | _      | _   | _    |            |    |    |    |    |        |        |           |    |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    | L |

| $LV_2$          |              |   |   |   |     |   |     |   |   |   | R    | M  | 1 M    | 2 N | 131  | <b>1</b> 4 | W  |    |    |    |        |        |           |    |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    | L |

| $LV_3$          |              |   | F | D | _   |   |     | _ | _ | - | -    | R  | M      | 1 N | 12 N | <b>/13</b> | M4 | W  |    |    |        |        |           |    |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    | L |

| LV <sub>3</sub> |              |   |   |   |     |   |     |   |   |   |      |    | F      | N   | 11 N | 12         | M3 | Μ4 | W  |    |        |        |           |    |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    | L |

| LV <sub>3</sub> |              |   |   |   |     |   |     |   |   |   |      |    |        | 1   | R    | <b>1</b> 1 | M2 | М3 | M  | W  | 7      |        |           |    |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    |   |

| LV <sub>3</sub> |              |   |   |   |     |   |     |   |   |   |      |    |        |     |      | R          | М1 | M2 | M3 | M  | 4 V    | V      |           |    |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    |   |

| MULV            |              |   |   | F | D   | - | _ - | _ | _ | - | -    | -  | - -    |     | _ -  | _          |    | R  | Y1 | Y  | 2 W    | V      |           |    |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    |   |

| MULV            |              |   |   |   |     |   |     |   |   |   |      |    |        |     |      |            |    |    | R  | Y  | 1 Y    | 2 \    | W         |    |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    |   |

| MULV            |              |   |   |   |     |   |     |   |   |   |      |    |        |     |      |            |    |    |    | R  | Y      | 1 \    | <b>′2</b> | W  |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    |   |

| MULV            |              |   |   |   |     |   |     |   |   |   |      |    |        |     |      |            |    |    |    |    | R      | ۲ ۲    | 71        | Y2 | W  |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    |   |

| ADDV            |              |   |   |   | F   | Ι | ) - | _ | _ |   |      | -  |        |     |      | _          | _  | _  | _  | _  |        |        | _         | _  |    | R  | X1 | W   | 7   |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    |   |

| ADDV            |              |   |   |   |     |   |     |   |   |   |      |    |        |     |      |            |    |    |    |    |        |        |           |    |    |    | R  | X   | 1 V | V   |    |    |    |    |     |        |        |       |    |            |    |    |    |    |   |

| ADDV            |              |   |   |   |     |   |     |   |   |   |      |    |        |     |      |            |    |    |    |    |        |        |           |    |    |    |    | R   | X   | 1 \ | W  |    |    |    |     |        |        |       |    |            |    |    |    |    |   |

| ADDV            |              |   |   |   |     |   |     |   |   |   |      |    |        |     |      |            |    |    |    |    |        |        |           |    |    |    |    |     | F   | X   | ζ1 | W  |    |    |     |        |        |       |    |            |    |    |    |    |   |

| SV <sub>1</sub> |              |   |   |   |     | I | F   | D | _ |   |      | .  |        |     |      | _          | _  | _  | _  |    | _      |        | _         | _  |    | R  | M  | 1 M | 2 M | 3 N | 14 | W  |    |    |     |        |        |       |    |            |    |    |    |    |   |

| SV <sub>1</sub> |              |   |   |   |     |   |     |   |   |   |      |    |        |     |      |            |    |    |    |    |        |        |           |    |    |    | R  | M   | 1 M | 2 N | 13 | M4 | W  |    |     |        |        |       |    |            |    |    |    |    |   |

| SV <sub>1</sub> |              |   |   |   |     |   |     |   |   |   |      |    |        |     |      |            |    |    |    |    |        |        |           |    |    |    |    | R   | M   | 1 N | 12 | М3 | Μ4 | W  |     |        |        |       |    |            |    |    |    |    |   |

| SV <sub>1</sub> |              |   |   |   |     |   |     |   |   |   |      |    |        |     |      |            |    |    |    |    |        |        |           |    |    |    |    |     | F   | R N | 11 | M2 | М3 | M  | 1 W | 7      |        |       |    |            |    |    |    |    |   |

| SV <sub>2</sub> |              |   |   |   |     |   |     | F | D | _ | _    | -  | _      |     |      | _          |    | _  | _  | _  | _      |        |           |    |    | _  |    | _   | - - | _ _ |    |    | R  | M1 | M   | 2 M    | 3 N    | 14    | W  |            |    |    |    |    | _ |

| SV <sub>2</sub> |              |   |   |   |     |   |     |   |   |   |      |    |        |     |      |            |    |    |    |    |        |        |           |    |    |    |    |     |     |     |    |    |    | R  | M   | 1 M    | 2 N    | 13 N  | И4 | W          |    |    |    |    | _ |

| SV <sub>2</sub> |              |   |   |   |     |   |     |   |   |   |      |    |        |     |      |            |    |    |    |    |        |        |           |    |    |    |    |     |     |     |    |    |    |    | R   | M      | 1 N    | 12 N  | И3 | <b>M</b> 4 | w  |    |    |    |   |

| SV <sub>2</sub> |              |   |   |   |     |   |     |   |   |   |      |    |        |     |      |            |    |    |    |    |        |        |           |    |    |    |    |     |     |     |    |    |    |    |     | R      | N      | I 1 N | M2 | M3         | M4 | W  |    |    | _ |

|                 |              |   |   |   |     |   |     |   |   |   |      |    |        |     |      |            |    |    |    |    |        |        |           |    |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    | _ |

|                 |              |   |   |   |     |   |     |   |   |   |      |    |        |     |      |            |    |    |    |    |        |        |           |    |    |    |    |     |     |     |    |    |    |    |     |        |        |       |    |            |    |    |    |    | _ |

|                 |              |   |   |   |     |   |     |   |   |   |      |    |        |     | T    |            |    |    |    |    |        |        |           |    |    |    |    |     |     |     |    |    |    |    |     |        |        | T     |    |            |    |    |    |    | _ |

|                 | l            |   |   |   |     |   |     |   |   |   |      |    |        |     | T    |            |    |    |    |    |        |        |           |    |    |    |    |     |     |     |    |    |    |    |     |        |        | T     |    |            |    |    |    |    | _ |

|                 | 1            |   |   |   |     |   | 1   |   |   | T |      |    | $\top$ |     | 1    |            |    |    |    |    | $\top$ | $\top$ |           |    |    |    |    |     |     |     |    |    |    |    |     | $\top$ | $\top$ | 1     |    |            |    |    |    |    | _ |

|                 |              |   |   |    |    |     |            |     |            |    |    |    |    |    |           |            |     |      |      | cy       | cl  | e    |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      |           |           |     |       |

|-----------------|--------------|---|---|----|----|-----|------------|-----|------------|----|----|----|----|----|-----------|------------|-----|------|------|----------|-----|------|----|----|----|----|------------------|----|-----------|-----|---|----|----|----|----|----|----|------|-----------|-----------|-----|-------|

| instr.          | 1            | 2 | 3 | 4  | 5  | 6   | 7          | 8   | 9          | 10 | 11 | 12 | 13 | 14 | 15        | 16         | 17  | 18   |      |          |     |      | 22 | 23 | 24 | 25 | 26               | 27 | 7 2       | 8 2 | 9 | 30 | 31 | 32 | 33 | 34 | 35 | 5 30 | 6 3       | 7 3       | 8 3 | 39 40 |

| $LV_1$          | $\mathbb{F}$ | D | R | М1 | M2 | 2M3 | <b>M</b> 4 | W   |            |    |    |    |    |    |           |            |     |      |      |          |     |      |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      |           |           |     |       |

| $LV_1$          |              |   |   | R  | M1 | M2  | М3         | M4  | W          |    |    |    |    |    |           |            |     |      |      |          |     |      |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      |           |           |     |       |

| $LV_1$          |              |   |   |    | R  | М1  | M2         | 2M3 | <b>M</b> 4 | W  |    |    |    |    |           |            |     |      |      |          |     |      |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      |           |           |     |       |

| $LV_1$          |              |   |   |    |    | R   | М1         | M2  | МЗ         | M4 | W  |    |    |    |           |            |     |      |      |          |     |      |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      |           |           |     |       |

| $LV_2$          |              | F | D | _  | _  | _   | R          | M1  | M2         | М3 | M4 | W  |    |    |           |            |     |      |      |          |     |      |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      |           |           |     |       |

| $LV_2$          |              |   |   |    |    |     |            | R   | M1         | M2 | М3 | M4 | W  |    |           |            |     |      |      |          |     |      |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      |           |           |     |       |

| $LV_2$          |              |   |   |    |    |     |            |     | R          | M1 | M2 | M3 | M4 | W  |           |            |     |      |      |          |     |      |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      |           |           |     |       |

| $LV_2$          |              |   |   |    |    |     |            |     |            | R  | M1 | M2 | М3 | M4 | W         |            |     |      |      |          |     |      |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      |           |           |     |       |

| LV <sub>3</sub> |              |   | F | D  | _  | _   |            | _   | _          | _  | R  | M1 | M2 | М3 | M4        | W          |     |      |      |          |     |      |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      |           |           |     |       |

| LV <sub>3</sub> |              |   |   |    |    |     |            |     |            |    |    | R  | M1 | М2 | М3        | M          | 1 W |      |      |          |     |      |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      |           |           |     |       |

| LV <sub>3</sub> |              |   |   |    |    |     |            |     |            |    |    |    | R  | М1 | M2        | M.         | 3M4 | ı W  | 7    |          |     |      |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      |           |           |     |       |

| LV <sub>3</sub> |              |   |   |    |    |     |            |     |            |    |    |    |    | R  | М1        | M          | 2M3 | M    | 4 W  | 7        |     |      |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      |           |           |     |       |

| MULV            |              |   |   | F  | D  | _   | _          | _   | _          | _  | _  | R  | Y1 | Y2 | w         |            |     |      |      |          |     |      |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      | T         |           |     |       |

| MULV            |              |   |   |    |    |     |            |     |            |    |    |    | R  | Y1 | <b>Y2</b> | W          |     |      |      |          |     |      |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      |           |           |     |       |

| MULV            |              |   |   |    |    |     |            |     |            |    |    |    |    |    | Y1        | -          | +   |      |      |          |     |      |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      | T         |           |     |       |

| MULV            |              |   |   |    |    |     |            |     |            |    |    |    |    |    | R         | <b>Y</b> 1 | Y2  | W    | 7    |          |     |      |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      | T         |           |     |       |

| ADDV            |              |   |   |    | F  | D   | _          | _   | _          | _  | _  | _  | _  | _  | _         | R          | X1  | W    | 7    |          |     |      |    |    |    |    |                  |    |           |     |   |    |    |    |    |    |    |      |           |           |     |       |