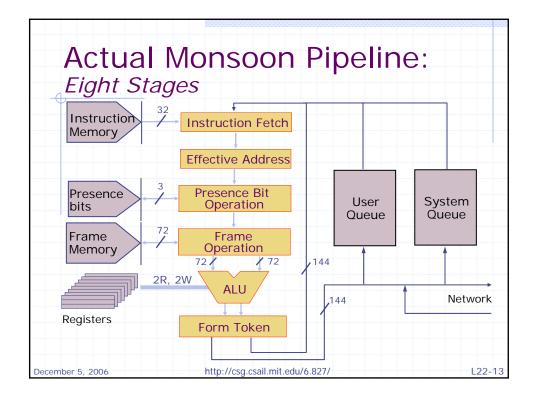

| Instructions directly control<br>the pipeline<br>The opcode specifies an operation for each pipeline stage:                                                                                                                                                    |                                               |                        |             |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------|-------------|--|

|                                                                                                                                                                                                                                                                | ode r                                         |                        | [dest2]     |  |

| <pre>EA WM RegOp ALU FormToken EA - effective address FP + r: frame relative r: absolute IP + r: code relative (not supported) WM - waiting matching Unary; Normal; Sticky; Exchange; Imperative PBs X port → PBs X Frame op X ALU inhibit Register ops:</pre> |                                               |                        |             |  |

| ALU:                                                                                                                                                                                                                                                           | ALU: $V_L X V_R \rightarrow V'_L X V'_R$ , CC |                        |             |  |

| Form token: $V_L \times V_R \times Tag_1 \times Tag_2 \times CC \rightarrow Token_1 \times Token_2$                                                                                                                                                            |                                               |                        |             |  |

| December 5, 2006                                                                                                                                                                                                                                               | http://                                       | /csg.csail.mit.edu/6.8 | 827/ L22-14 |  |

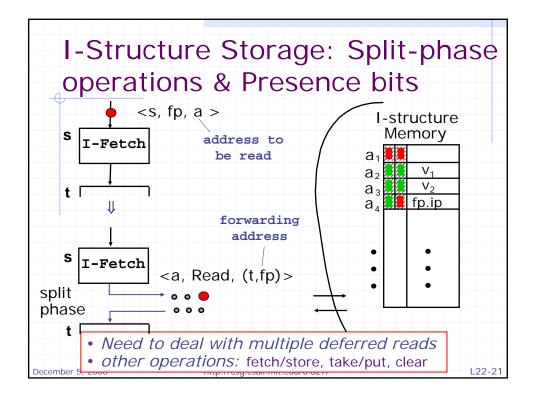

| Data Structures in E                                                                                                 | Dataflow                |

|----------------------------------------------------------------------------------------------------------------------|-------------------------|

| <ul> <li>Data structures reside in a structure store</li> <li>⇒ tokens carry pointers</li> </ul>                     | Memory<br>P ···· P<br>a |

| <ul> <li>I-structures: Write-once,</li> <li>Read multiple times or</li> <li>allocate, write, read,, read,</li> </ul> | I-fetch                 |

| deallocate<br>⇒ No problem if a reader<br>arrives before the writer at the<br>memory location                        | a V<br>I-store          |

| December 5, 2006 http://csg.csail.mit.edu/6.827/                                                                     | L22-20                  |