### Hardware Description Languages

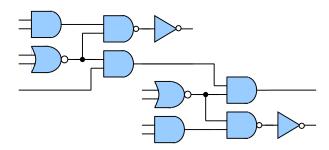

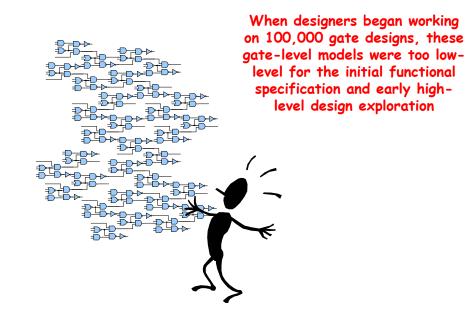

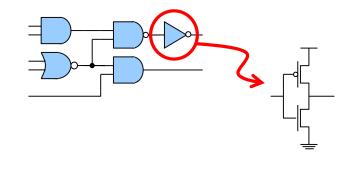

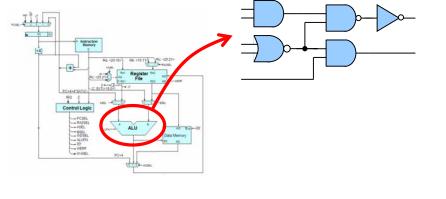

As designs grew larger and more complex, designers began using gate-level models described in a Hardware Description Language to help with verification before fabrication

### Hardware Description Languages

6.884 - Spring 2005

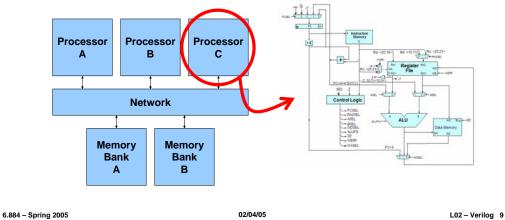

#### Hardware Description Languages Advantages of HDLs Allows designers to talk about what the hardware Designers again turned to HDLs for help - abstract behavioral should do without actually designing the hardware models written in an HDL itself, or in other words HDLs allow designers to provided both a precise separate behavior from implementation at various specification and a framework levels of abstraction for design exploration HDLs do this with modules and interfaces Control Logie + BSEL WASE 02/04/05 02/04/05 L02 – Verilog 6 6.884 - Spring 2005 L02 - Verilog 5 6.884 - Spring 2005

## Advantages of HDLs

Allows designers to talk about what the hardware should do without actually designing the hardware itself, or in other words HDLs allow designers to separate behavior from implementation at various levels of abstraction

### Advantages of HDLs

Allows designers to talk about what the hardware should do without actually designing the hardware itself, or in other words HDLs allow designers to separate behavior from implementation at various levels of abstraction

### Advantages of HDLs

Allows designers to talk about what the hardware should do without actually designing the hardware itself, or in other words HDLs allow designers to separate behavior from implementation at various levels of abstraction

## A Tale of Two HDLs

### VHDL

ADA-like verbose syntax, lots of redundancy

Extensible types and simulation engine

Design is composed of entities each of which can have multiple architectures

Gate-level, dataflow, and behavioral modeling. Synthesizable subset.

Harder to learn and use, DoD mandate

### Verilog

C-like concise syntax

Built-in types and logic representations

Design is composed of modules which have just one implementation

Gate-level, dataflow, and behavioral modeling. Synthesizable subset.

Easy to learn and use, fast simulation

## Advantages of HDLs

Allows designers to talk about what the hardware should do without actually designing the hardware itself, or in other words HDLs allow designers to separate behavior from implementation at various levels of abstraction

- Designers can develop an executable functional specification that documents the exact behavior of all the components and their interfaces

- Designers can make decisions about cost, performance, power, and area earlier in the design process

- Designers can create tools which automatically manipulate the design for verification, synthesis, optimization, etc.

### We will use Verilog ...

02/04/05

### Advantages

6.884 - Spring 2005

6.884 - Spring 2005

- Choice of many US design teams

- Most of us are familiar with C-like syntax

- Simple module/port syntax is familiar way to organize hierarchical building blocks and manage complexity

- With care it is well-suited for both verification and synthesis

### Disadvantages

- Some comma gotchas which catch beginners everytime

- C syntax can cause beginners to assume C semantics

- Easy to create very ugly code, good and consistent coding style is essential

L02 - Verilog 10

### An HDL is NOT a Software Programming Language

### Software Programming Language

- Language which can be translated into machine instructions and then executed on a computer

### Hardware Description Language

- Language with syntactic and semantic support for modeling the temporal behavior and spatial structure of hardware

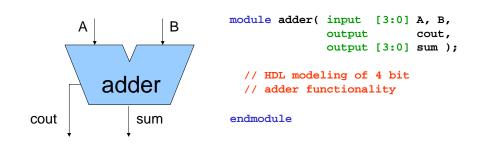

## Hierarchical Modeling with Verilog

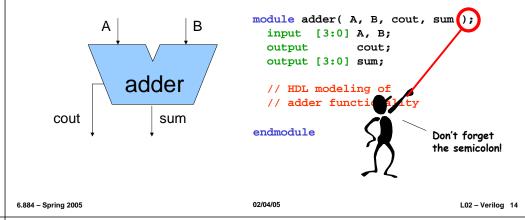

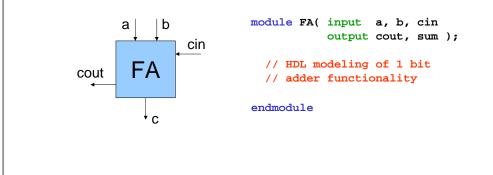

# A Verilog module includes a module name and an interface in the form of a port list

- Must specify direction and bitwidth for each port

- Verilog-2001 introduced a succinct ANSI C style portlist

## Hierarchical Modeling with Verilog

# A Verilog module includes a module name and an interface in the form of a port list

- Must specify direction and bitwidth for each port

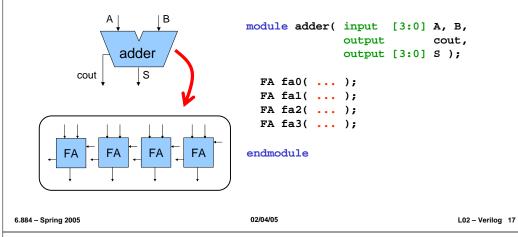

### Hierarchical Modeling with Verilog

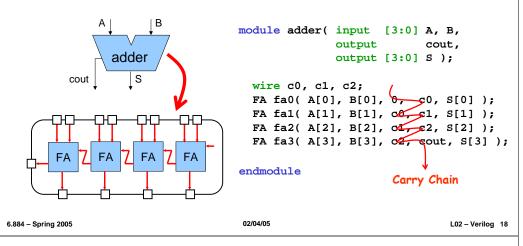

### A module can contain other modules through module instantiation creating a module hierarchy

- Modules are connected together with nets

- Ports are attached to nets either by position or by name

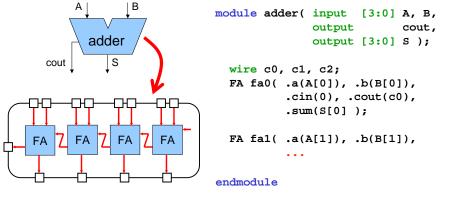

### Hierarchical Modeling with Verilog

### A module can contain other modules through module instantiation creating a module hierarchy

- Modules are connected together with nets

- Ports are attached to nets either by position or by name

### Hierarchical Modeling with Verilog

### A module can contain other modules through module instantiation creating a module hierarchy

- Modules are connected together with nets

- Ports are attached to nets either by position or by name

## Hierarchical Modeling with Verilog

### A module can contain other modules through module instantiation creating a module hierarchy

- Modules are connected together with nets

- Ports are attached to nets either by position

#### 6.884 – Spring 2005

02/04/05

6.884 - Spring 2005

#### Dataflow : 4-input Mux and Adder Dataflow : 4-input Multiplexer // Four input muxltiplexor module mux4( input a, b, c, d Dataflow style Verilog module mux4( input a, b, c, d input [1:0] sel, enables descriptions input [1:0] sel, output out ); output out ); which are more assign out = ( sel == 0 ) ? a : abstract than gatewire $t_0 =$ ( (sel[1] & c) | (~sel[1] & a) ); ( sel == 1 ) ? b : level Verilog wire t1 = ( (sel[1] & d) | (~sel[1] & b) ); (sel == 2) ? c : wire out = ( (t0 | sel[0]) & (t1 | ~sel[0]) ); ( sel == 3 ) ? d : 1'bx; endmodule endmodule An implicit continuous assignment combines the net declaration with an assign statement // Simple four bit adder and thus is more succinct module adder( input [3:0] op1, op2, output [3:0] sum ); assign sum = op1 + op2;endmodule 6.884 - Spring 2005 02/04/05 02/04/05 L02 - Verilog 26 L02 - Verilog 25 6.884 - Spring 2005

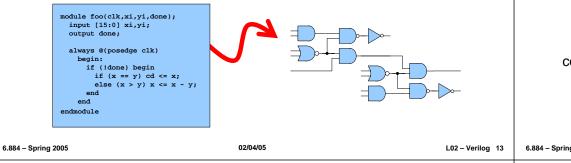

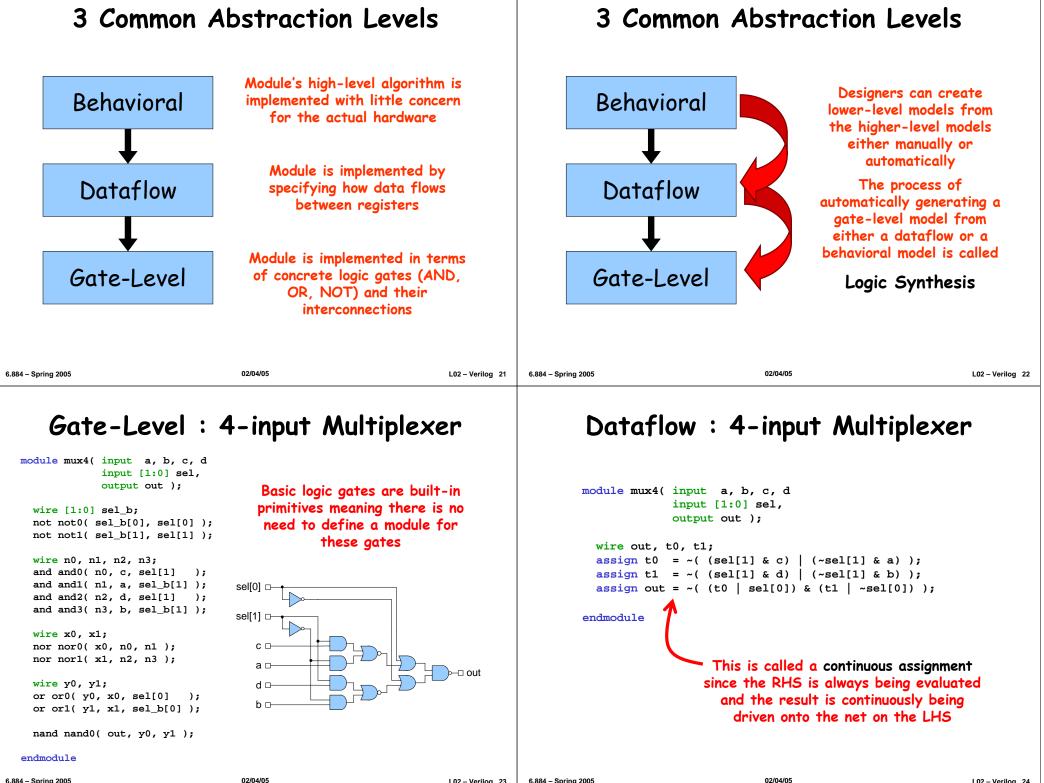

## Dataflow : Key Points

Dataflow modeling enables the designer to focus on where the state is in the design and how the data flows between these state elements without becoming bogged down in gate-level details

- Continuous assignments are used to connect combinational logic to nets and ports

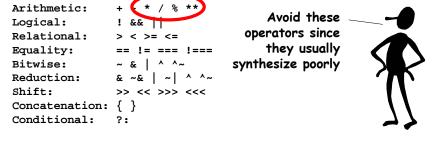

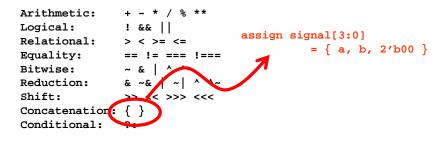

- A wide variety of operators are available including:

### Dataflow : Key Points

Dataflow modeling enables the designer to focus on where the state is in the design and how the data flows between these state elements without becoming bogged down in gate-level details

- Continuous assignments are used to connect combinational logic to nets and ports

- A wide variety of operators are available including:

L02 - Verilog 27 6.884 - Spring 2005

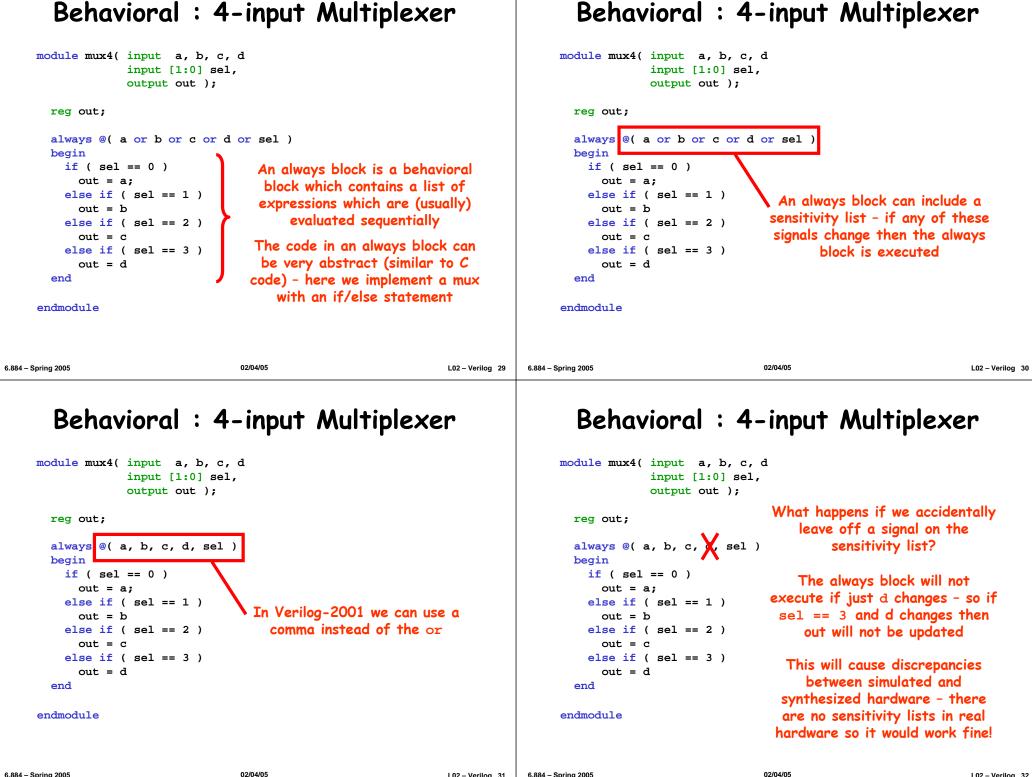

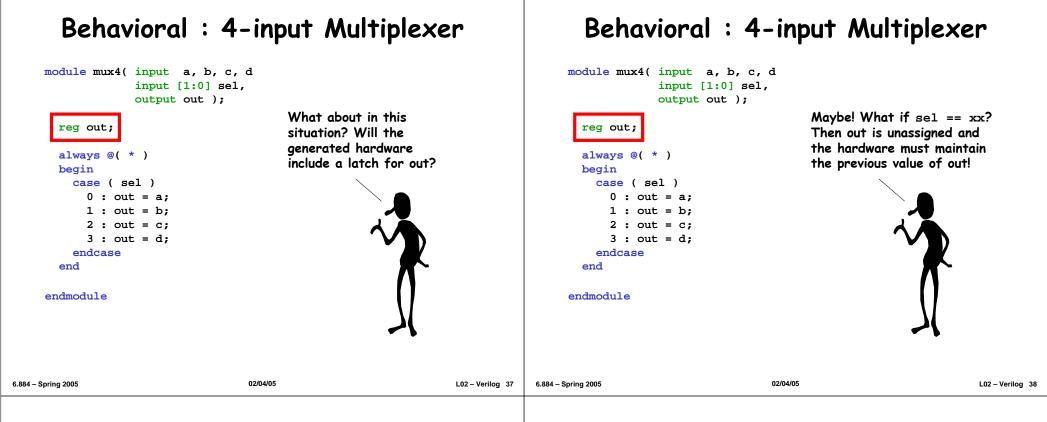

### **Behavioral : 4-input Multiplexer**

### **Behavioral : 4-input Multiplexer**

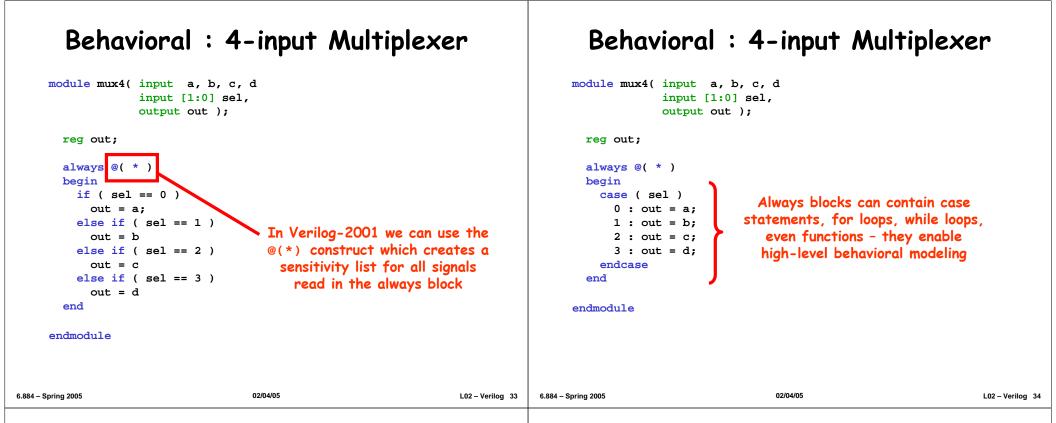

### Behavioral : 4-input Multiplexer

#### reg out;

always @( \* )

begin

case ( sel )

0 : out = a;

1 : out = b;

2 : out = c;

3 : out = d;

endcase

end

#### endmodule

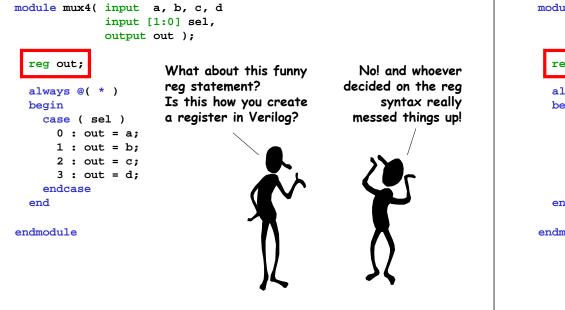

In Verilog a reg is just a variable – when you see reg think variable not hardware register!

Any assignments in an always block must assign to a reg variable – the reg variable may or may not actually represent a hardware register

If the always block assigns a value to the reg variable for all possible executions then the reg variable is not actually a hardware register

### Behavioral : 4-input Multiplexer

L02 – Verilog 39

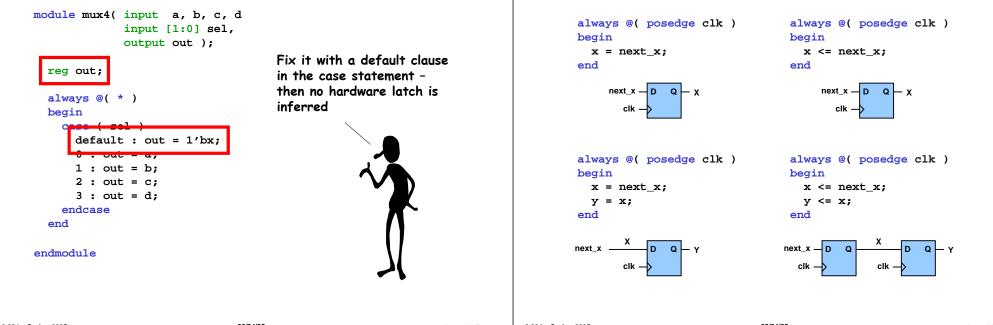

**Behavioral Non-Blocking Assignments**

L02 – Verilog 40

### **Behavioral Non-Blocking Assignments**

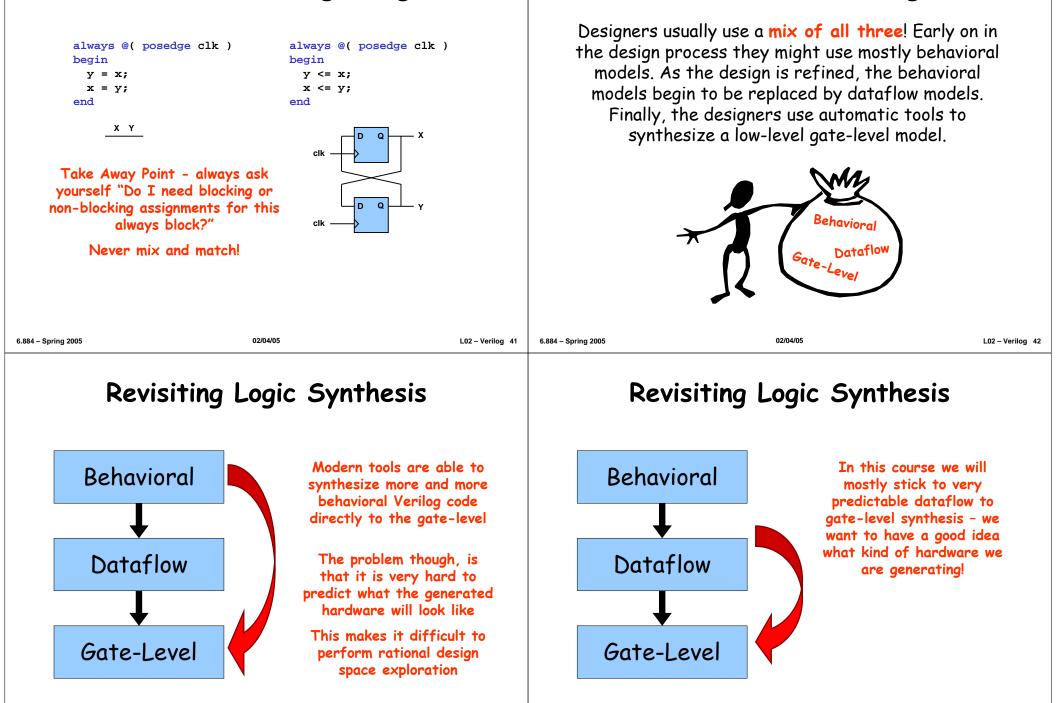

Which abstraction is the right one?

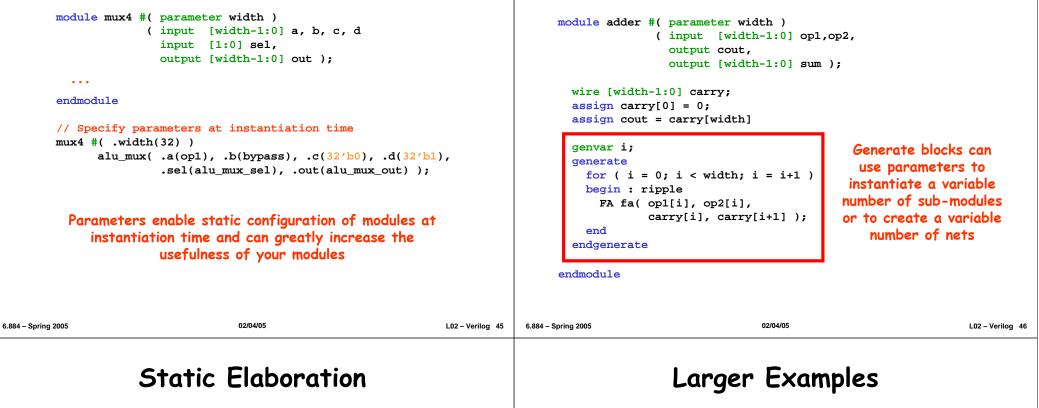

### Writing Parameterized Models

Writing Parameterized Models

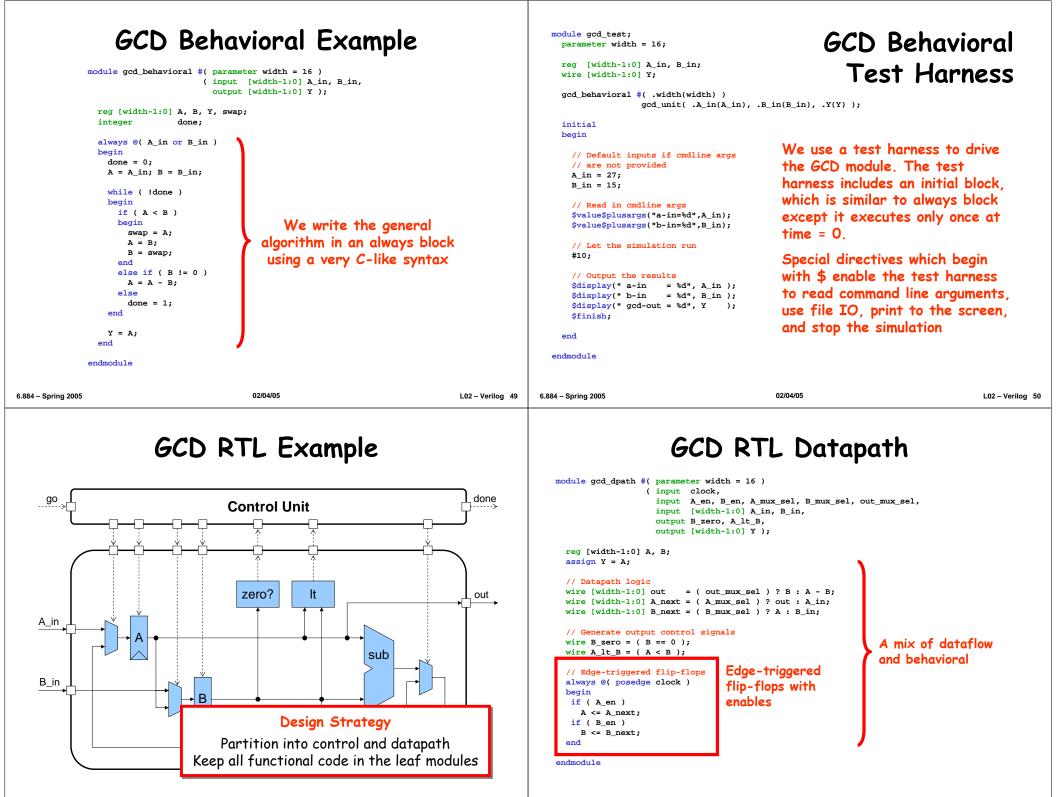

Let's briefly examine two larger digital designs and consider the best way to model these designs in Verilog

02/04/05

02/04/05

02/04/05

L02 – Verilog 52

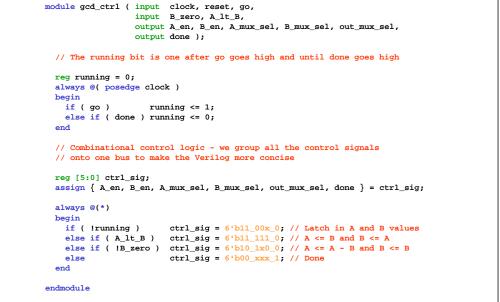

### GCD RTL Control Unit

02/04/05

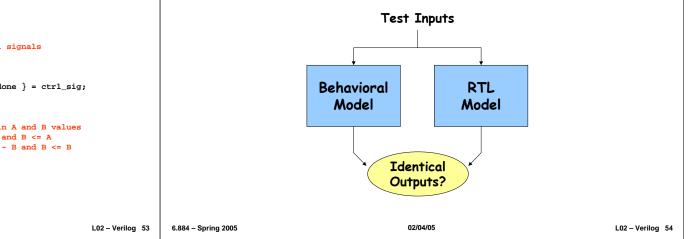

### GCD Testing

We use the same test inputs to test both the behavioral and the RTL models. If both models have the exact same observable behavior then the RTL model has met the functional specification.

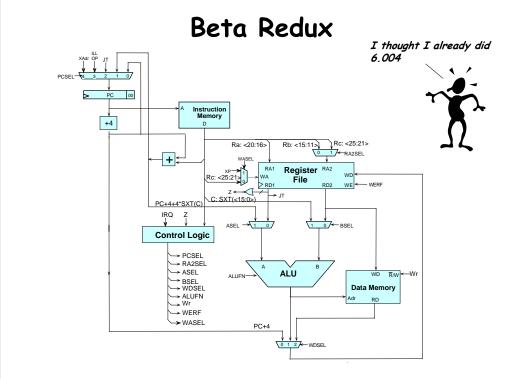

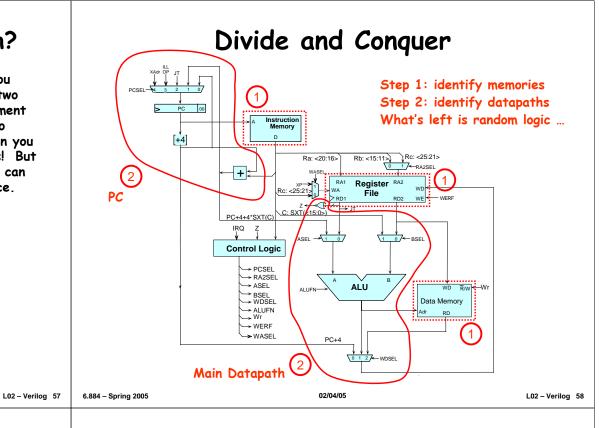

### Goals for the Beta Verilog Description

#### Readable, correct code that clearly captures the architecture diagram – "correct by inspection"

Partition the design into regions appropriate for different implementation strategies. Big issue: wires are "bad" since they take up area and have capacitance (impacting speed and power).

- Memories: very dense layouts, structured wires pretty much route themselves, just a few base cells to design & verify.

- Datapaths: each cell contains necessary wiring, so replicating cells (for N bits of datapath) also replicates wiring. Data flows between columnar functional units on horizontal busses and control flows vertically.

- Random Logic: interconnect is "random" but library of cells can be designed ahead of time and characterized.

- Think about physical partition since wires that cross boundaries can take lots of area and blocks have to fit into the floorplan without wasteful gaps.

6.884 - Spring 2005

02/04/05

### Hey! What happened to abstraction?

Wasn't the plan to abstract-away the physical details so we could concentrate on getting the functionality right? Why are we worrying about wires and floorplans at this stage? Because life is short! If you have the luxury of writing two models (the first to experiment with function, the second to describe the actual partition you want to have), by all means! But with a little experience you can tackle both problems at once.

6.884 - Spring 2005

02/04/05

### Take Away Points

# Hardware description languages are an essential part of modern digital design

- HDLs can provide an executable functional specification

- HDLs enable design space exploration early in design process

- HDLs encourage the development of automated tools

- HDLs help manage complexity inherent in modern designs

#### Verilog is not a software programming language so always be aware of how your Verilog code will map into real hardware

**Carefully plan your module hierarchy** since this will influence many other parts of your design

### Laboratory 1

You will be building an RTL model of a two-stage MIPS processor

- 1. Read through the lab and the SMIPS processor spec which is posted on the website

- 2. Look over the Beta Verilog posted on the website

- 3. Try out the GCD Verilog example in 38-301 (or on any Athena/Linux machine)

```

% setup 6.884

% cp -r /mit/6.884/examples/gcd .

% cat gcd/README

```

4. Next week's tutorial will review the Beta implementation and describe how to use Lab 1 toolchain (vcs, virsim, smips-gcc)

og 59 6.884 – Spring 2005