# Hardware Implementation of an 802.11a Transmitter

Elizabeth Basha, Steve Gerding, Rose Liu May 9, 2005

Complex Digital Systems (6.884) Final Project

Complex Digital Systems (6.884) Final Project

noise

## Design Specifications

802.11a

• Modulation: Orthogonal Frequency Division Multiplexing

• One symbol consists of 48 data-encoded complex

pairs and 4 pilot complex pairs which protect against

• OFDM symbol - unit of data transmission

• IEEE Standard for wireless communication

• Frequency of Operation: 5Ghz band

- Transmit at 3 datarates:

- 6Mb/s 1 24-bit input data frame per OFDM symbol

- 12Mb/s 2 24-bit input data frames per OFDM symbol

- 24Mb/s 4 24-bit input data frames per OFDM symbol

- Design Goals:

- Minimize Area

- $\bullet$  Minimize Power by reducing frequency and lowering  $\boldsymbol{V}_{DD}$

- Just-in-time performance to meet the required datarates

\_\_\_

3

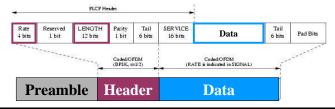

**Transmitter Overview**

- Tasks:

- Encodes data for forward error correction

- Maps data into complex pairs & distributes them among the different frequency indices

- Transform frequency data into time domain

- Packet Format:

Complex Digital Systems (6.884) Final Project

Complex Digital Systems (6.884) Final Project

4

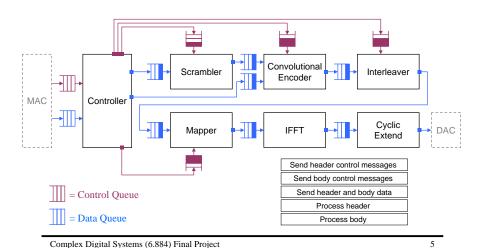

#### Top Level Model

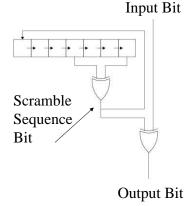

#### Basic Serial Scrambler Design

- Processes 1 input bit per cycle

- Simultaneously generates 1 scramble sequence bit and computes 1 output bit

- Repeatedly generates a 127-bit scramble sequence

Complex Digital Systems (6.884) Final Project

#### .

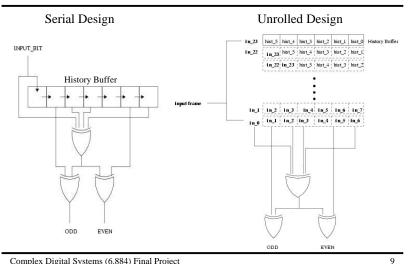

### **Initial Scrambler Design**

#### For Each Message:

- Generates the entire 127-bit scramble sequence 127 cycles

- Stores the scrambler sequence to be used throughout the message

#### Advantage:

• Processes 1 24-bit input frame per cycle

#### Disadvantage:

• Large initialization overhead is especially apparent for a series of very short messages

### Unrolled Scrambler Design

- Simultaneously generates 1 frame of the scrambler sequence and processes 1 frame of input data per cycle

- Updates the state of the seed register at end of each cycle

- •Advantages:

- 1 cycle initialization

- Processes 1 24-bit frame per cycle

### Convolutional Encoder Design

Complex Digital Systems (6.884) Final Project

11

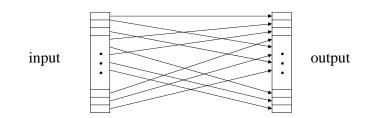

### Interleaver Algorithm

- Reorders input data bits

- Datarate dependent:

- Interleaving Pattern

- # of bits interleaved together

Complex Digital Systems (6.884) Final Project

10

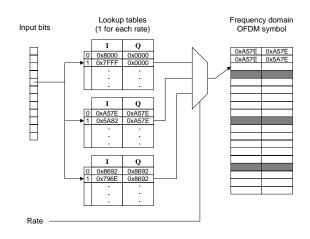

### Mapper Algorithm

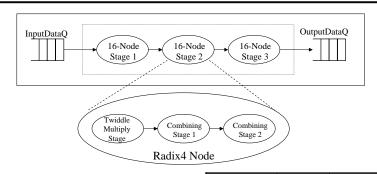

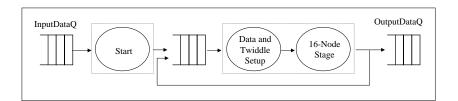

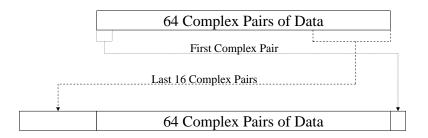

### IFFT Initial Design

- Area = 29.12mm<sup>2</sup>

- Cycle Time = 63.18ns

| Radix4 Nodes | *   | +    |

|--------------|-----|------|

| 1            | 16  | 24   |

| 48           | 768 | 1152 |

### IFFT Design Exploration 1

- Area = 5.19mm<sup>2</sup>

- Cycle Time = 30.50ns

Complex Digital Systems (6.884) Final Project

13

15

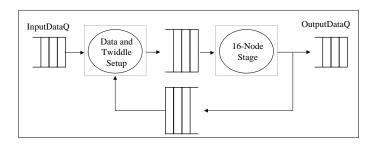

### IFFT Design Exploration 2

- Area =  $4.57 \text{mm}^2$

- Cycle Time = 32.89ns

Complex Digital Systems (6.884) Final Project

14

### Cyclic Extender

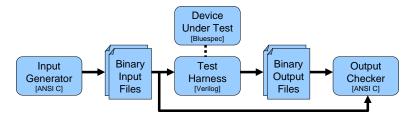

### Test Strategy

- Our test structure must enable us to:

- Debug each module separately

- Quickly verify new version of modules

- Verify correctness of entire system

- Measure throughput of individual modules and system as a whole

- To do this, we leveraged the framework of the Extreme Benchmark Suite (XBS)

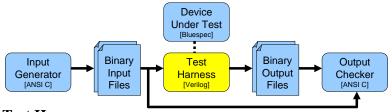

#### **XBS** Overview

XBS is a benchmark suite designed to measure the performance of highly parallel processors and custom hardware implementations.

All XBS benchmarks have the following structure:

Complex Digital Systems (6.884) Final Project

17

19

#### **XBS** Overview

Complex Digital Systems (6.884) Final Project

18

#### **XBS** Overview

#### **Test Harness**

- Encapsulates device under test

- Reads in input files and generates output files

- Measures performance [throughput in bits per cycle] of device under test

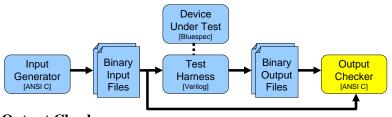

#### **XBS** Overview

#### **Output Checker**

- Reads in input and output files and determines if output files are correct

- Usually contains an ANSI C reference version of DUT

- If output is incorrect, displays location of discrepancy and correct value for debugging purposes

#### Results

#### Place and route results:

| Total Area          | 5.27 mm <sup>2</sup> |  |  |

|---------------------|----------------------|--|--|

| Critical Path Delay | 32.89 ns             |  |  |

#### XBS testing results:

| Module                | Throughput |              |       |      |           |          |  |

|-----------------------|------------|--------------|-------|------|-----------|----------|--|

|                       | Inpu       | t bits per o | cycle | OFDM | symbols p | er cycle |  |

| Scrambler             | 24         | 24           | 24    | 1    | 0.5       | 0.25     |  |

| Convolutional Encoder | 24         | 24           | 24    | 1    | 0.5       | 0.25     |  |

| Interleaver           | 12         | 12           | 12    | 0.5  | 0.25      | 0.125    |  |

| Mapper                | 12         | 16           | 19.2  | 0.5  | 0.333     | 0.2      |  |

| IFFT                  | 6          | 12           | 24    | 0.25 | 0.25      | 0.25     |  |

| Cyclic Extend         | 24         | 48           | 96    | 1    | 1         | 1        |  |

| Transmitter System    | 6          | 12           | 12    | 0.25 | 0.25      | 0.125    |  |

21

Complex Digital Systems (6.884) Final Project

### Evaluation

- Our design fully conforms to the IEEE 802.11a standard

- Our design meets timing for the 6, 12, and 24 Mbps transmission rates

- Total system throughput (24 Mbps) = 12 bits / cycle

- Clock Frequency = 30.4 MHz

- Maximum data rate of system = 364.8 Mbps

- We can turn our timing slack into power savings by reducing V<sub>DD</sub> and clock frequency

- Clock frequency can be reduced to 2.0 MHz