## **Side Channel Mitigations**

Mengjia Yan Spring 2022

#### Outline

- Non-interference: a general security property

- Verify Non-interference for Side Channels and Transient Execution

- Hardware and Software Contract

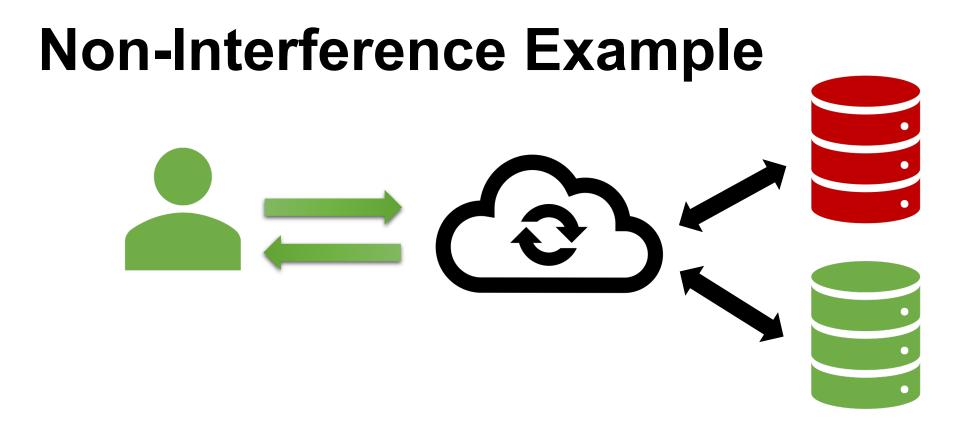

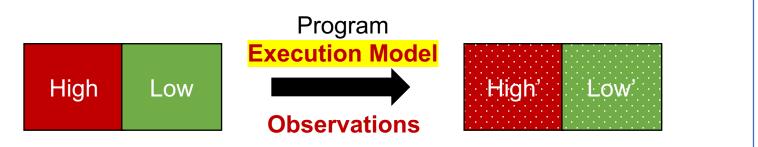

#### **Non-Interference Example**

Low (low sensitivity, not highly classified) High (high sensitivity, not seen by uncleared users)

- Intuitively: not affecting

- Any sequence of low inputs will produce the same low outputs, regardless of what the high level inputs are.

#### **Use Cases of Non-interference**

- Confidentiality: e.g., process isolation

- My memory -> Confidentiality of High state

- Other programs' memory -> Low

- Integrity: e.g., control-flow hijacking

- My memory -> Integrity of Low State

- Attacker controlled input -> High

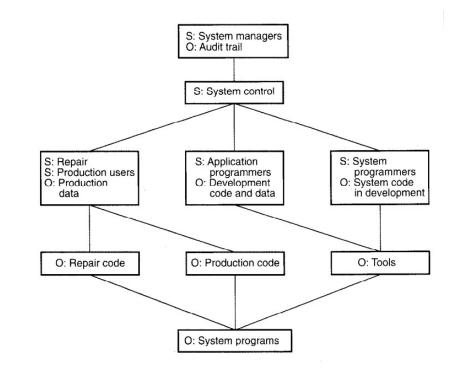

- Swirl example

- Expand High-Low to Lattice

Lattice-Based Access Control Models; Ravi S. Sandhu; 1993

#### **Non-Interference Formulation**

- Formulate the property as state-machine transition.

- Looking at a single-trace is ineffective

#### **Generality of Non-interference**

Conventionally: ISA emulation for software analysis/testing

- Can also be used for hardware security design

- Micro-architecture: state includes caches, buffers, buses, etc.

- Circuit level: flip-flop

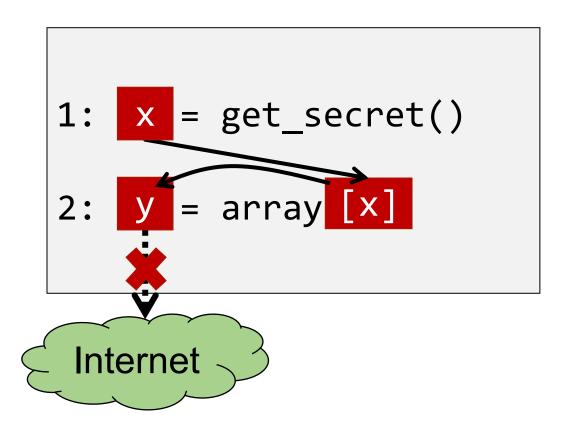

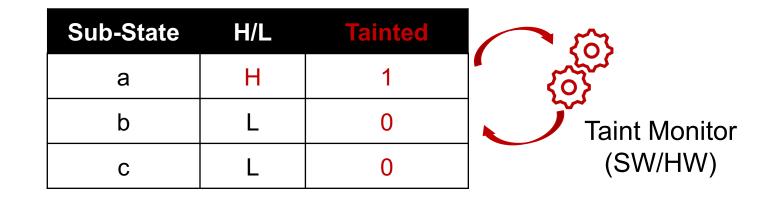

## Taint Analysis (also Taint Tracking)

- Goal: verify non-interference property

- Analogy

- Components:

- Source of taint (high state)

- Taint propagation

- Taint check (no taint on low state)

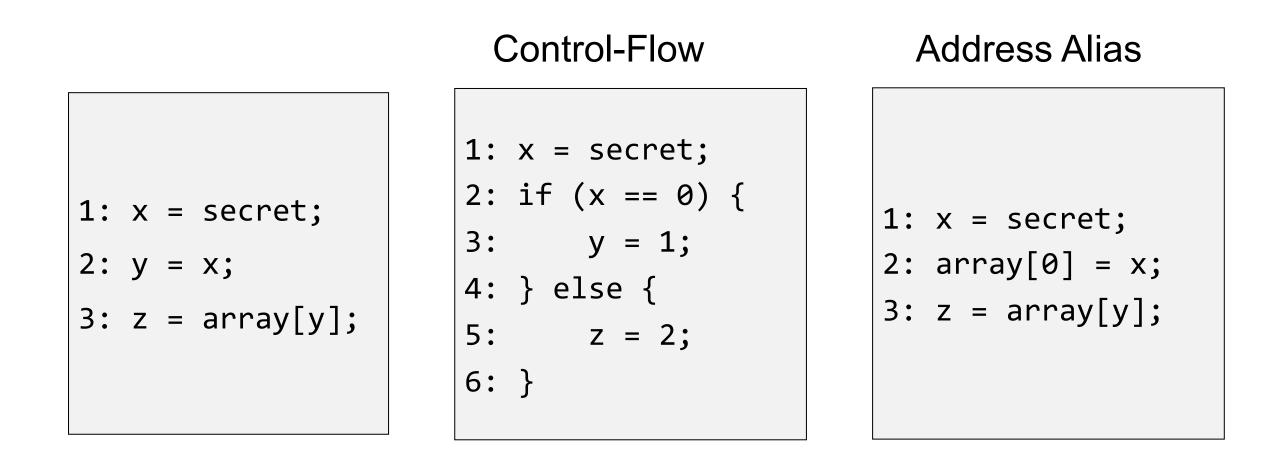

#### **Explicit and Implicit Information Flow**

#### **Taint Analysis Methods**

- Dynamic: run-time check

- Detect non-interference violation on-the-fly for a given input

- Static: compiler-time check

- Verify whether a given program is secure/bug-free for arbitrary input

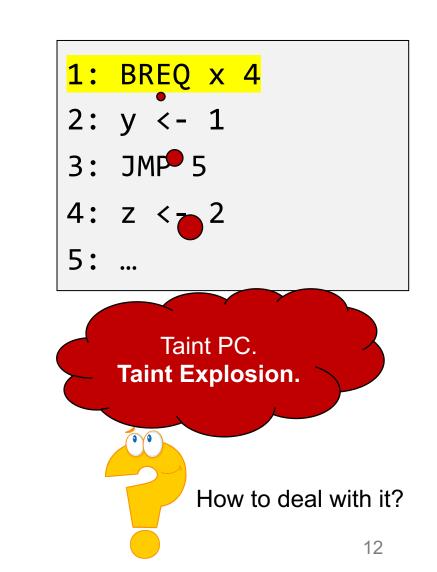

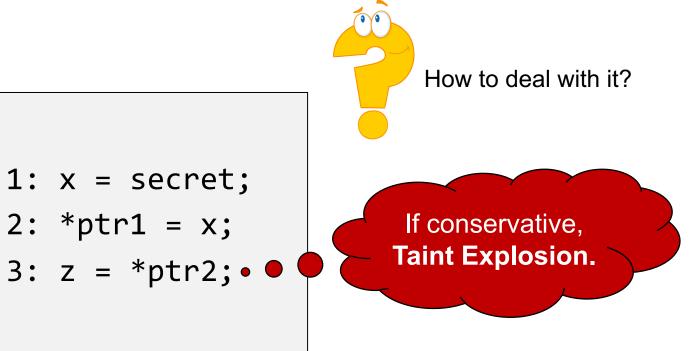

#### **Dynamic Taint Analysis**

- Problems:

- Granularity

- Run-time overhead

- How to handle implicit flow?

#### **Dynamic Taint Analysis**

- Problems:

- Granularity

- Run-time overhead

- How to handle implicit flow?

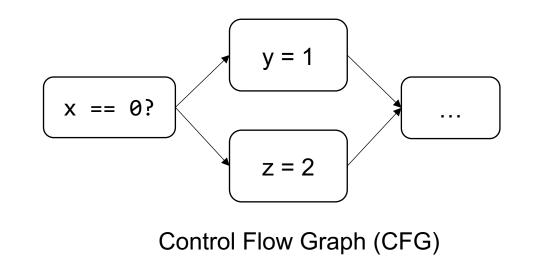

#### **Static Taint Analysis**

- Key differences

- Verify whether a given program is secure for arbitrary inputs

- Can leverage high-level program information

### **Static Taint Analysis**

#### Problems

- Scalability (check all possible inputs)

- How to handle implicit flow?

#### Takeaways

- Non-interference property: general security property for both confidentiality and integrity

- Taint Analysis

- Useful techniques for checking non-interference

- Static: verification tool

- Dynamic: online monitoring

- Both have taint explosion problems

#### Non-interference for Timing Side Channels

- How to define non-interference for timing side channels?

- How to check whether a given mitigation achieves noninterference or not?

- How to coordinate software and hardware mitigations? How to reason security about software-hardware co-design?

- Given SW x, running on HW y can protect all data containing secret z? {SW x, HW y, sec z}

#### **Non-interference at Micro-arch Level**

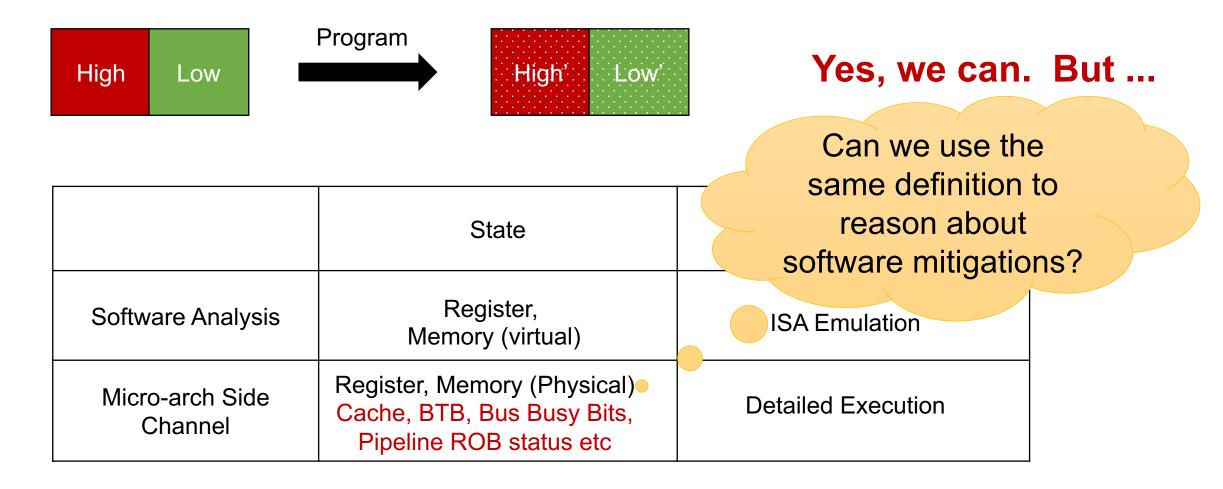

|                            | State | State Transition<br>(Program Execution) |

|----------------------------|-------|-----------------------------------------|

| Software Analysis          |       |                                         |

| Micro-arch Side<br>Channel |       |                                         |

#### **Non-interference at Micro-arch Level**

|                            | State                                                                                | State Transition<br>(Program Execution) |

|----------------------------|--------------------------------------------------------------------------------------|-----------------------------------------|

| Software Analysis          | Register,<br>Memory (virtual)                                                        | ISA Emulation                           |

| Micro-arch Side<br>Channel | Register, Memory (Physical)<br>Cache, BTB, Bus Busy Bits,<br>Pipeline ROB status etc | Detailed Instruction<br>Execution       |

## Verify HW Design Using Static IFT

Annotate variables (registers and wires) with security labels.

- 1 reg {L} v, {L} l, {H} h; 2 // LH (0) = L, LH (1) = H 3 wire {LH(v)} shared;

- 4 // l=h is forbidden

5 if (v == 0) l = shared;

6 else h = shared;

- 7 // implicit flow, not allowed 8 if (h == 0) l = 0; 9 else l = 1;

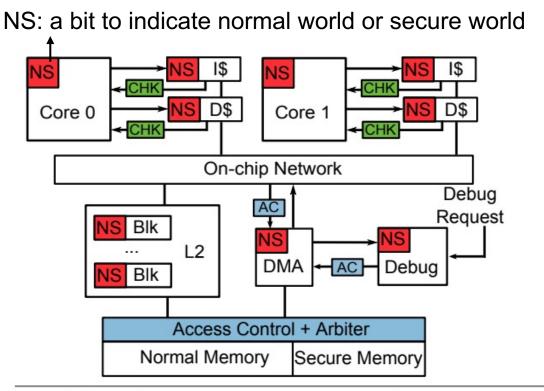

#### Figure 1. TrustZone prototype implementation.

Verification of a Practical Hardware Security Architecture Through Static Information Flow Analysis; Ferraiuolo et al; ASPLOS'17 HyperFlow: A Processor Architecture for Nonmalleable, Timing-Safe Information Flow Security; Ferraiuolo et al; CCS'18

6.888 L6 - Side Channel Mitigations

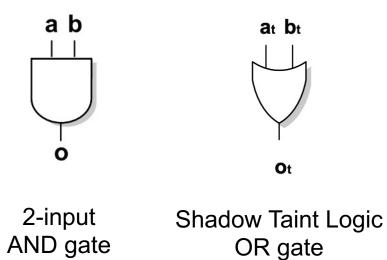

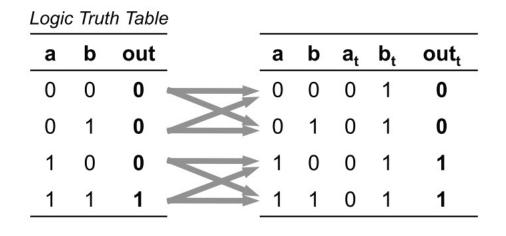

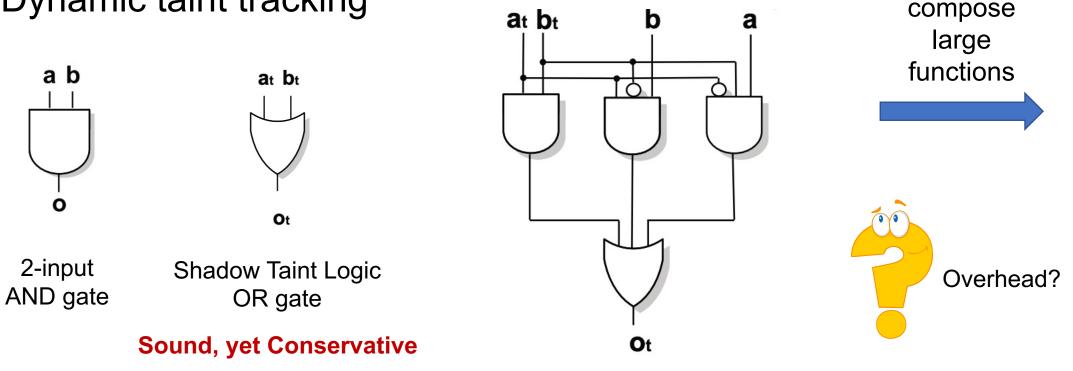

#### **Non-Interference at Gate Level**

• Dynamic taint tracking

Sound, yet Conservative

Complete Information Flow Tracking from the Gates Up; Tiwari et al; ASPLOS'09

#### **Non-Interference at Gate Level**

• Dynamic taint tracking

#### **Precise Taint Logic**

Complete Information Flow Tracking from the Gates Up; Tiwari et al; ASPLOS'09

#### **Non-interference at Micro-arch Level**

|                            | State                                                                                | State Transition<br>(Program Execution) |

|----------------------------|--------------------------------------------------------------------------------------|-----------------------------------------|

| Software Analysis          | Register,<br>Memory (virtual)                                                        | ISA Emulation                           |

| Micro-arch Side<br>Channel | Register, Memory (Physical)<br>Cache, BTB, Bus Busy Bits,<br>Pipeline ROB status etc | Detailed Execution                      |

#### **Non-interference at Micro-arch Level**

### "Constant-time" Programming

- Write program w/o data-dependent behavior

- Verify non-interference of timing side channels by simulating micro-arch state machine.

- Problems?

Original: Data Oblivious:

bool secret;

x <- pub[secret\*64];</pre>

bool secret; a <- pub[0]; b <- pub[64]; cmov x <- (secret) ? b : a;</pre>

#### **Observation Model**

- Motivation:

- Avoid verifying SW against specific implementations

- Observations:

- Program counters, Memory access addresses, Memory access data, Register data

- Dependent on hardware implementation

$$\forall S1, S2, (S, P) \rightarrow S', \mathbf{0}$$

if  $S1_L = S2_L$

then  $S1'_L = S2'_L$  and  $\mathbf{01} = \mathbf{02}$

### Verify "Constant-time" Programming

Using Observations

**Original:**

bool secret; x <- pub[secret\*64];</pre> **Data Oblivious:**

bool secret; a <- pub[0]; b <- pub[64]; cmov x <- (secret) ? b : a;</pre>

Memory access sequence: H Memory access sequence: 0 (L), 64 (L)

#### Takeaways

00

- How to verify non-interference of timing side channels?

- To check HW: state transition at micro-arch and gate level

- To check SW: define observation model

- Observation model can be served as a contract between HW and SW

Shall we always assume memory access sequence as the observation?

#### No. It is hardware dependent. Think about Silent Store and Cache compression.

# "Constant-time Programming" Fails in the Spectre Era

Memory access sequence: x (L), y (L)

#### **Execution Model**

- Motivation:

- Incorporate speculative execution in an execution model

- Add Execution Model:

- Sequential, Branch mis-speculation, etc.

$$\forall S1, S2, (S, P) \rightarrow S', O$$

if  $S1_L = S2_L$

then  $S1'_L = S2'_L$  and  $O1 = O2$

Hardware-Software Contracts for Secure Speculation; Guarnieri et al; S&P'20

6.888 L6 - Side Channel Mitigations

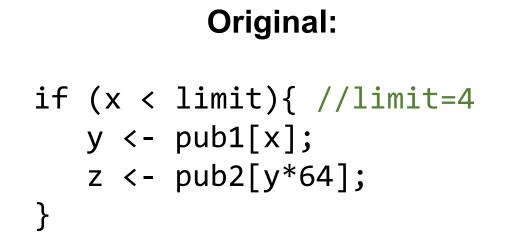

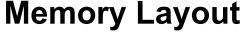

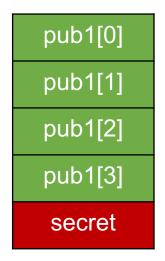

# "Constant-time Programming" Fails in the Spectre Era

if (x < limit){ //limit=4

y <- pub1[x];

z <- pub2[y\*64];

}</pre>

**Original:**

Memory access sequence (no mispredict): x (L), y (L) Memory access sequence (with mispredict):

x (L), y (H)

**Memory Layout**

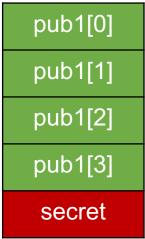

#### **SW Mitigations Against Spectre**

#### fence: SLH:

if (x < limit){

lfence();

y <- pub1[x];

z <- pub2[y\*64];

}

if (x < limit){

cmov mask <- (i < limit) 0xFFFF:0

y <- pub1[x] & mask;

z <- pub2[x\*64];

}</pre>

Memory access sequence (with mispredict): Ø

Memory access sequence (with mispredict): 0 (L), y (L)

Chandler Carruth. Speculative Load Hardening. <u>https://llvm.org/docs/SpeculativeLoadHardening.html</u>

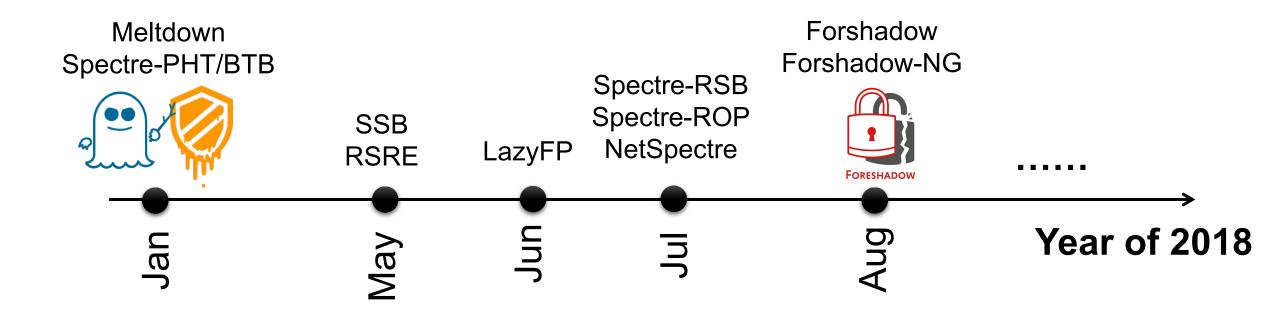

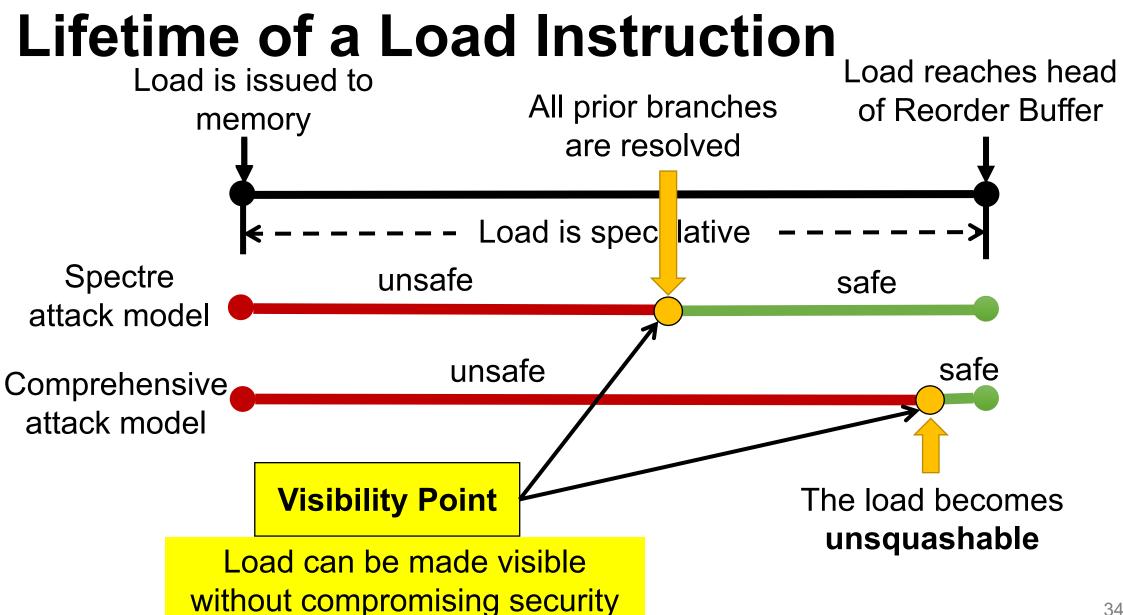

#### HW Solutions Targeting Many Transient Execution Attacks

#### **Generalization of Transient Execution**

- Different transient execution attacks create transient instructions in different ways

- Speculative attack model: an attacker can exploit any speculative insts

Speculative Attack Model Various events, such as:

- Control-flow mispredictions  $\rightarrow$  Spectre

- Virtual memory exceptions → Meltdown

- Attack Model ) Address alias between a load and an earlier store

- Interrupts

- -• etc.

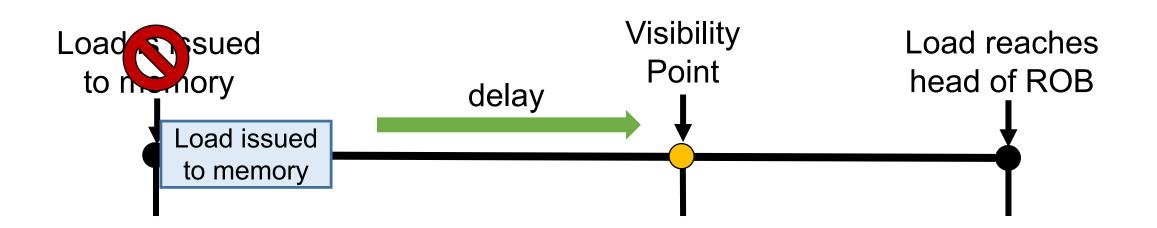

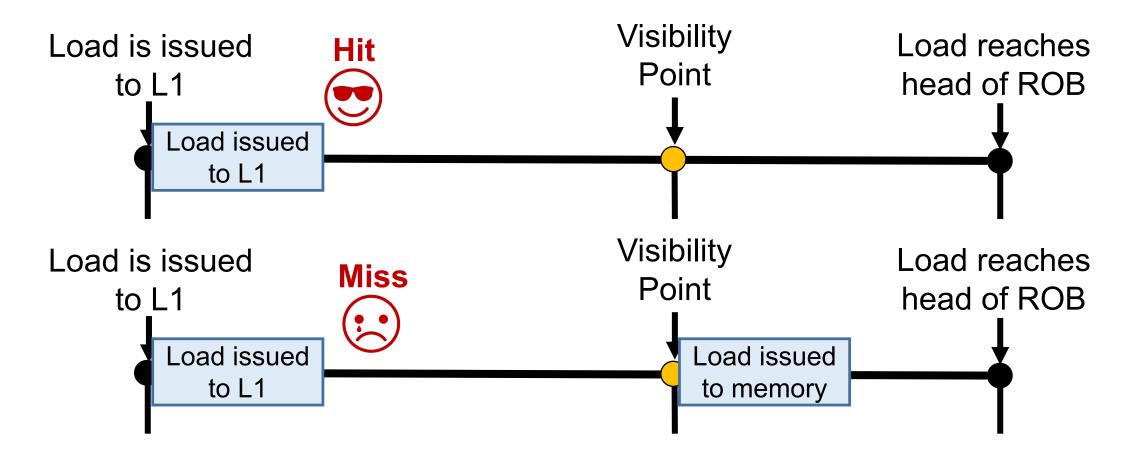

#### Naïve Solution: Delay all spec Loads

#### Delay-on-Miss (DoM)

Christos Sakalis, et al. Efficient invisible speculative execution through selective delay and value prediction. ISCA'19

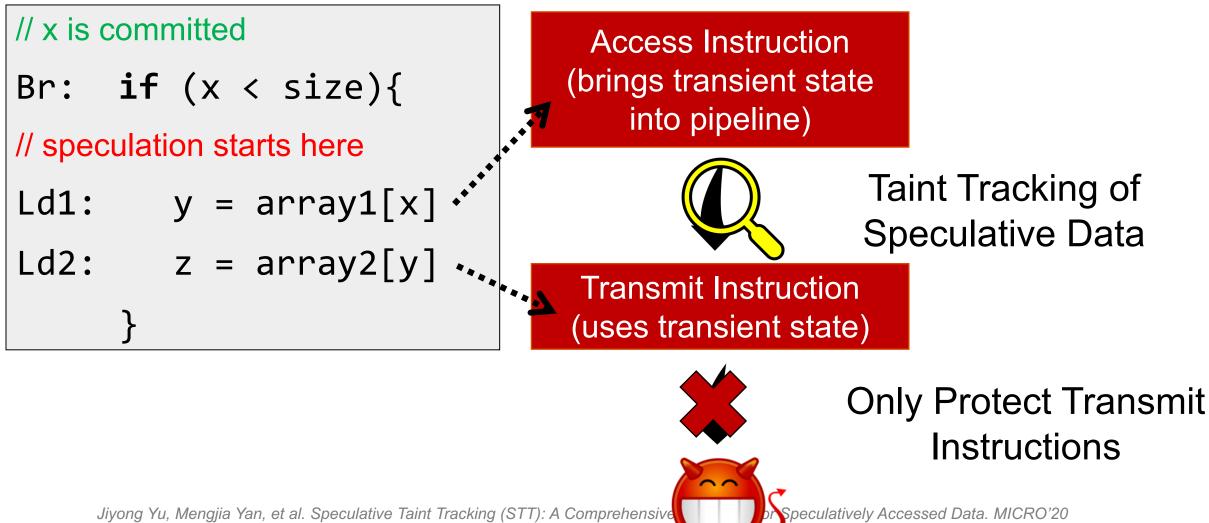

#### **Performance Optimizations**

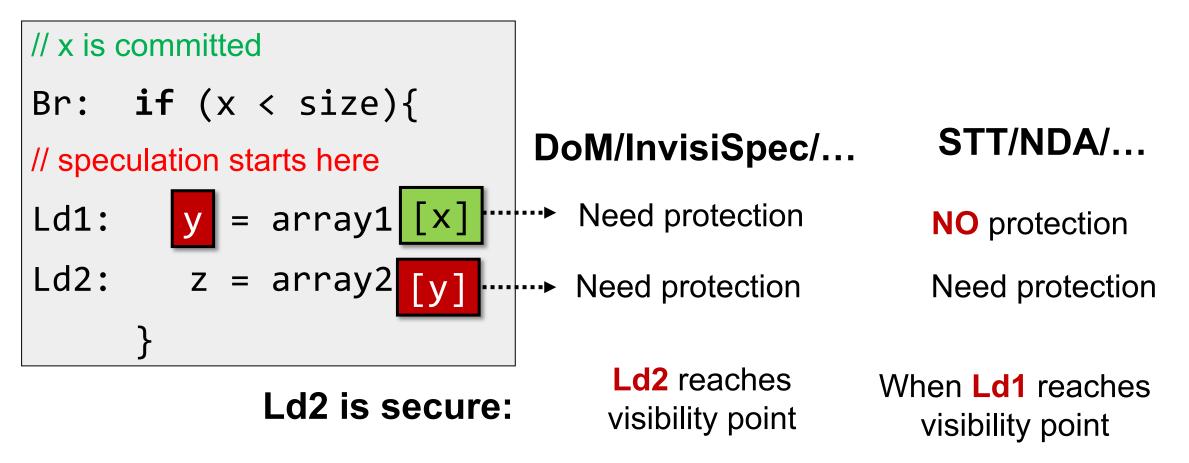

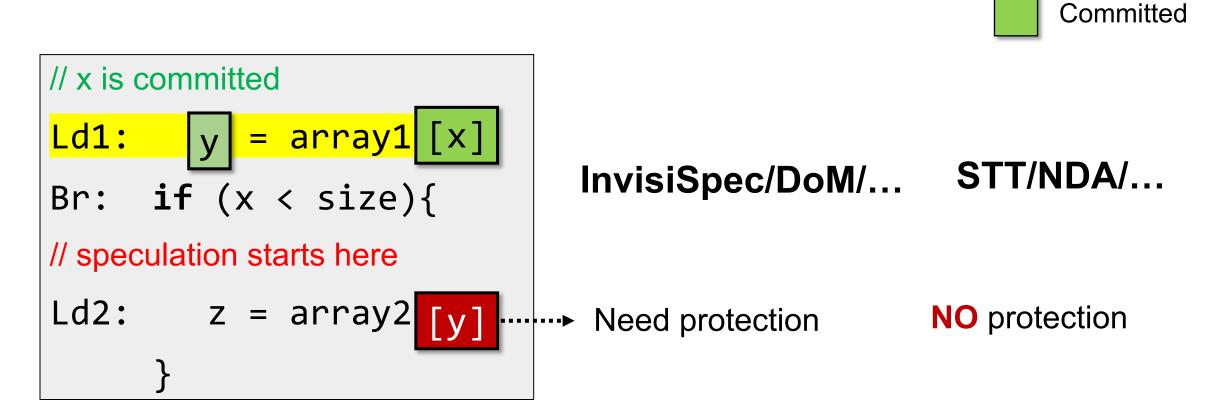

// x is committed

Br: if (x < size){</pre>

// speculation starts here

Ld1: y = array1[x]

Ld2: z = array2[y]

**X:** Committed register state (exists in legal execution)

Insight: Only need to protect the instructions that <u>use</u> transient states

**y:** Transient register state (does not exist in legal execution)

# STT, NDA, etc

# **Comparing Two Approaches**

#### **Comparing Two Approaches**

Speculative

#### Problems

- Different HW mitigations achieve different security properties

- How to communicate this information to SW?

- ISA?

- List code patterns?

- Specify execution model + observation model?

Current state-of-the-art. May not be the final solution. An unsolved research problem.

| Disable<br>Speculatio | on Protection                                             | Execution Model |                              |

|-----------------------|-----------------------------------------------------------|-----------------|------------------------------|

|                       |                                                           | Sequential      | Speculative (can mispredict) |

|                       | Program Counter                                           |                 |                              |

| Observation<br>Model  | Program Counter<br>+ Memory Address                       |                 |                              |

|                       | Program Counter<br>+ Memory Address<br>+ Register Content |                 |                              |

|                      |                                                           | Execution Model        |                              |

|----------------------|-----------------------------------------------------------|------------------------|------------------------------|

|                      |                                                           | Sequential             | Speculative (can mispredict) |

| Observation<br>Model | Program Counter                                           |                        |                              |

|                      | Program Counter<br>+ Memory Address                       | Disable<br>Speculation |                              |

|                      | Program Counter<br>+ Memory Address<br>+ Register Content | No<br>Protection       | No<br>Protection             |

| DoM                  |                                                           | Execution Model        |                              |

|----------------------|-----------------------------------------------------------|------------------------|------------------------------|

|                      |                                                           | Sequential             | Speculative (can mispredict) |

| Observation<br>Model | Program Counter                                           |                        |                              |

|                      | Program Counter<br>+ Memory Address                       | Disable<br>Speculation |                              |

|                      | Program Counter<br>+ Memory Address<br>+ Register Content |                        |                              |

|                      |                                                           | Execution Model        |                              |

|----------------------|-----------------------------------------------------------|------------------------|------------------------------|

|                      |                                                           | Sequential             | Speculative (can mispredict) |

| Observation<br>Model | Program Counter                                           |                        | DoM                          |

|                      | Program Counter<br>+ Memory Address                       | Disable<br>Speculation |                              |

|                      | Program Counter<br>+ Memory Address<br>+ Register Content | DoM                    |                              |

| STT                  |                                                           | Execution Model        |                              |

|----------------------|-----------------------------------------------------------|------------------------|------------------------------|

|                      |                                                           | Sequential             | Speculative (can mispredict) |

|                      | Program Counter                                           |                        | DoM                          |

| Observation<br>Model | Program Counter<br>+ Memory Address                       | Disable<br>Speculation |                              |

|                      | Program Counter<br>+ Memory Address<br>+ Register Content | DoM                    |                              |

|                      |                                                           | Execution Model        |                              |

|----------------------|-----------------------------------------------------------|------------------------|------------------------------|

|                      |                                                           | Sequential             | Speculative (can mispredict) |

| Observation<br>Model | Program Counter                                           |                        | DoM                          |

|                      | Program Counter<br>+ Memory Address                       | Disable<br>Speculation | STT                          |

|                      | Program Counter<br>+ Memory Address<br>+ Register Content | DoM STT                |                              |

#### Summary

- Non-interference

- A general security property that can be used to reason software security and micro-arch side channels

- Pros/Cons of static and dynamic taint analysis

- Reason about non-interference for side mitigations

- Both observation model and execution model are hardware dependent

- Fundamental problem, timing is not defined at the contract between HW and SW (currently ISA)