```

Pipelining Two-Cycle SMIPS -

single rule

rule doPipeline ;

let instF = iMem.req(pc);

fetch

let ppcF = nextAddr(pc); let nextPc = ppcF;

let newf2d = Valid (Fetch2Decode{pc:pc,ppc:ppcF,

inst:instF});

if(isValid(f2d)) begin

execute

let x = fromMaybe(?, f2d); let pcD = x.pc;

let ppcD = x.ppc; let instD = x.inst;

these values are

let dInst =\ decode(instD);

being redefined

... register fetch ...;

let eInst = exec(dInst, rVal1, rVal2, pcD, ppcD);

...memory operation ...

...rf update ...

if (eInst.mispredict) begin nextPc = eInst.addr;

newf2d = Invalid;

end

pc <= nextPc; f2d <= newf2d;

endrule

http://csg.csail.mit.edu/6.S195

```

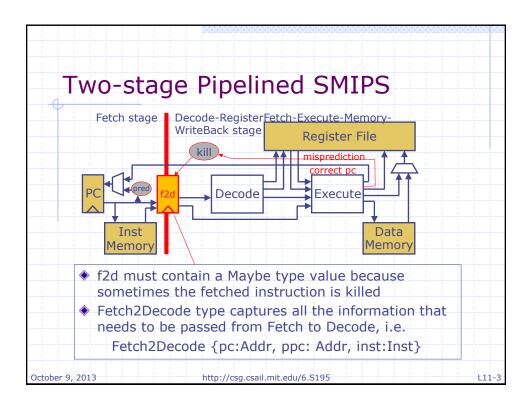

# Inelastic versus Elastic pipeline

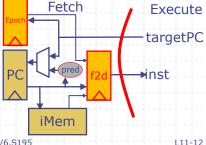

- The pipeline presented is inelastic, that is, it relies on executing Fetch and Execute together or atomically

- In a realistic machine, Fetch and Execute behave more asynchronously; for example memory latency or a functional unit may take variable number of cycles

- If we replace f2d register by a FIFO then it is possible to make the machine more elastic, that is, Fetch keeps putting instructions into f2d and Execute keeps removing and executing instructions from f2d

October 9, 2013 http://csg.csail.mit.edu/6.S195

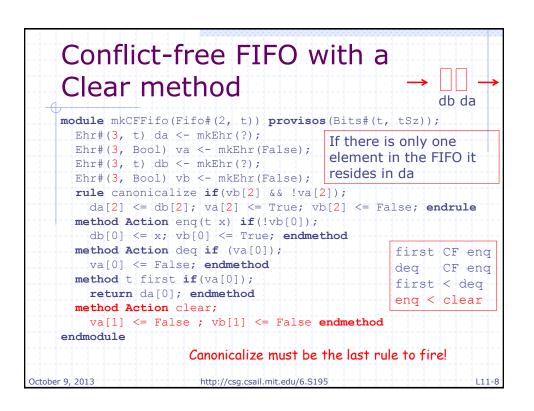

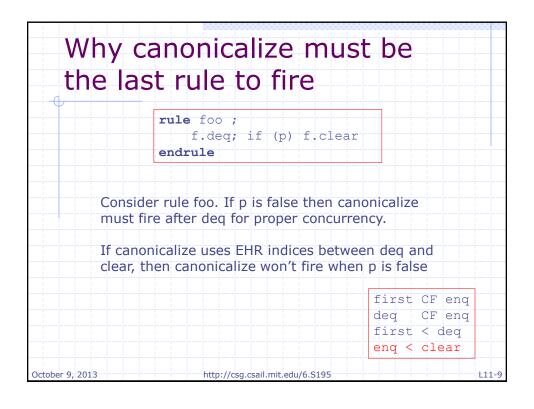

#### An elastic Two-Stage pipeline rule doFetch ; let instF = iMem.req(pc); let ppcF = nextAddr(pc); pc <= ppcF;</pre> f2d.enq(Fetch2Decode{pc:pc, ppc:ppcF, inst:instF}); endrule Can these rules execute concurrently rule doExecute; assuming the FIFO let x = f2d.first; let pcD = x.pc; allows concurrent eng, let ppcD = x.ppc; let instD = x.inst; deg and clear? let dInst = decode(instD); ... register fetch ...; let eInst = exec(dInst, rVal1, rVal2, pcD, ppcD); ...memory operation ... ...rf update ... No because of a if (eInst.mispredict) begin possible double pc <= eInst.addr; f2d.clear; end write in pc else f2d.deq; endrule October 9, 2013 http://csg.csail.mit.edu/6.S195 L11-6

```

An elastic Two-Stage pipeline:

for concurrency make pc into an EHR

rule doFetch ;

let instF = iMem.reg(pc[0]);

let ppcF = nextAddr(pc[0]); pc[0] <= ppcF;</pre>

f2d.eng(Fetch2Decode{pc:pc[0],ppc:ppcF,inst:inst});

endrule

These rules can

execute concurrently

rule doExecute;

assuming the FIFO has

let x = f2d.first; let pcD = x.pc;

(eng CF deg) and

let ppcD = x.ppc; let instD = x.inst;

(eng < clear)

let dInst = decode(instD);

... register fetch ...;

let eInst = exec(dInst, rVal1, rVal2, pcD, ppcD);

...memory operation ...

Double writes in pc

...rf update ...

have been replaced

if (eInst.mispredict)

by prioritized

pc[1] <= eInst.addr; f2d.clear; end</pre>

writes in pc

else f2d.deq;

endrule

http://csg.csail.mit.edu/6.S195

```

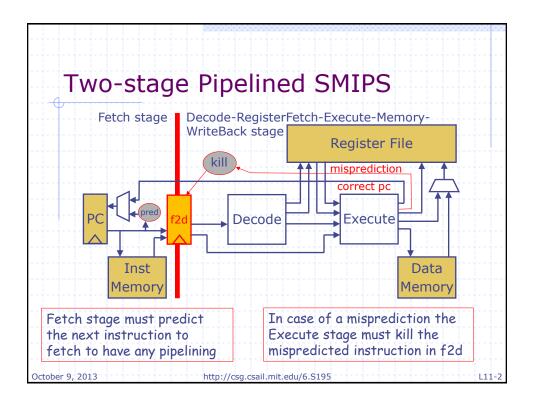

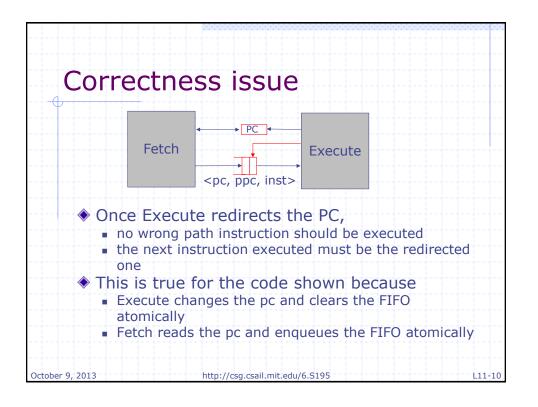

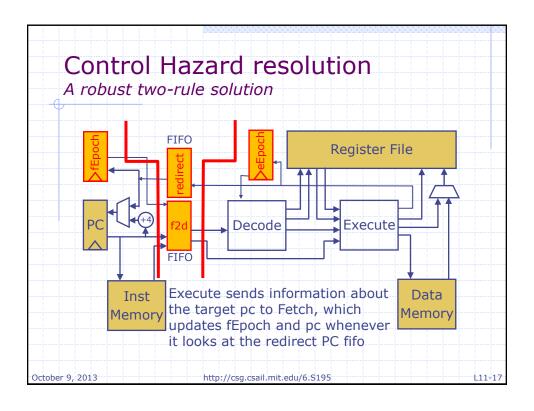

### Killing fetched instructions

- ◆ In the simple design with combinational memory we have discussed so far, the mispredicted instruction was present in the f2d. So the Execute stage can atomically

- Clear the f2d

- Set the pc to the correct target

- In highly pipelined machines there can be multiple mispredicted and partially executed instructions in the pipeline; it will generally take more than one cycle to kill all such instructions

Need a more general solution then clearing the f2d FIFO

October 9, 2013

http://csg.csail.mit.edu/6.S195

L11-1

# Epoch: a method for managing control hazards

- Add an epoch register in the processor state

- The Execute stage changes the epoch whenever the pc prediction is wrong and sets the pc to the correct value

- The Fetch stage associates the current epoch with every instruction when it is fetched

- The epoch of the instruction is examined when it is ready to execute. If the processor epoch has changed the instruction is thrown away

October 9, 2013

http://csg.csail.mit.edu/6.S195

```

An epoch based solution

Can these rules execute concurrently?

rule doFetch ;

let instF=iMem.reg(pc[0]);

let ppcF=nextAddr(pc[0]); pc[0]<=ppcF;</pre>

yes

f2d.eng(Fetch2Decode(pc:pc[0],ppc:ppcF,epoch:epoch,

inst:instF});

endrule

two values for epoch are sufficient

rule doExecute;

let x=f2d.first; let pcD=x.pc; let inEp=x.epoch;

let ppcD = x.ppc; let instD = x.inst;

if(inEp == epoch) begin

let dInst = decode(instD); ... register fetch ...;

let eInst = exec(dInst, rVal1, rVal2, pcD, ppcD);

...memory operation ...

...rf update ...

if (eInst.mispredict)

pc[1] <= eInst.addr; epoch <= epoch + 1; end</pre>

f2d.deq; endrule

October 9, 2013

http://csg.csail.mit.edu/6.S195

```

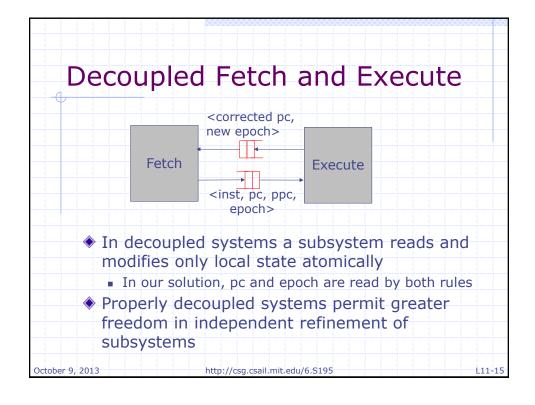

### Discussion

- Epoch based solution kills one wrong-path instruction at a time in the execute stage

- It may be slow, but it is more robust in more complex pipelines, if you have multiple stages between fetch and execute or if you have outstanding instruction requests to the iMem

- It requires the Execute stage to set the pc and epoch registers simultaneously which may result in a long combinational path from Execute to Fetch

October 9, 2013 http://csg.csail.mit.edu/6.S195 L11-

```

Two-stage pipeline

Decoupled code structure

module mkProc(Proc);

Fifo#(Fetch2Execute) f2d <- mkFifo;

Fifo#(Addr) execRedirect <- mkFifo;

Reg#(Bool) fEpoch <- mkReg(False);</pre>

Reg#(Bool) eEpoch <- mkReg(False);</pre>

rule doFetch;

let instF = iMem.req(pc);

f2d.enq(... instF ..., fEpoch);

endrule

rule doExecute;

if (inEp == eEpoch) begin

Decode and execute the instruction; update state;

In case of misprediction, execRedirect.eng(correct pc);

f2d.deg;

endrule

endmodule

October 9, 2013

http://csg.csail.mit.edu/6.S195

```

```

The Fetch rule

rule doFetch;

let instF = iMem.req(pc);

pass the pc and predicted pc

if(!execRedirect.notEmpty)

to the execute stage

begin

let ppcF = nextAddrPredictor(pc);

pc <= ppcF;

f2d.enq(Fetch2Execute{pe. pc, ppc: ppcF,

inst: instF, epoch: fEpoch});

end

else

fEpoch <= !fEpoch; pc <= execRedirect.first;</pre>

execRedirect.deq;

end

endrule

Notice: In case of PC redirection,

nothing is enqueued into f2d

October 9, 2013

http://csg.csail.mit.edu/6.S195

```

```

The Execute rule

exec returns a flag

if there was a fetch

misprediction

rule doExecute;

let instD = f2d.first.inst; let pcF

= f2d.first.pc;

let ppcD = f2d.first.ppc; let inEp

= f2d.first.epocl

if (inEp == eEpoch) begin

let dInst = decode(instD);

let rVal1 = rf.rd1(validRegValue(dInst.src1));

let rVal2 = rf.rd2(validRegValue(dInst.src2));

let eInst = exec(dInst, rVal1, rVal2, pcD, ppcD);

if (eInst.iType == Ld) eInst.data <-

dMem.req(MemReq{op: Ld, addr: eInst.addr, data: ?});

else if (eInst.iType == St) let d <-

dMem.req(MemReq{op: St, addr: eInst.addr, data: eInst.data});

if (isValid(eInst.dst))

rf.wr(validRegValue(eInst.dst), eInst.data);

if(eInst.mispredict) begin

execRedirect.enq(eInst.addr); eEpoch <= !inEp;</pre>

end

Can these rules execute concurrently?

end

f2d.deq;

yes, assuming CF FIFOs

endrule

October 9, 2013

http://csg.csail.mit.edu/6.S195

L11-20

```