# LABORATORY FOR COMPUTER SCIENCE

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

## **An I-Structure Memory Controller (ISMC)**

Computation Structures Group Memo 239 23 May 1984

Steven K. Heller

This report describes research done at the Laboratory for Computer Science of the Massachusetts Institute of Technology. Funding for the Laboratory is provided in part by the Advanced Research Projects Agency of the Department of Defense under Office of Naval Research contract N00014-75-C-0661. The author was supported by the International Business Machines Corporation as a part of MIT's VI-A program. This report appeared as the author's Masters Thesis at the Massachusetts Institute of Technology in May, 1983.

### An I-Structure Memory Controller (ISMC)

by

#### Steven K. Heller

Submitted to the Department of

Electrical Engineering and Computer Science

on May 13, 1983 in partial fulfillment of the requirements

for the Degrees of Bachelor of Science and Master of Science

in Computer Science and Engineering

#### **ABSTRACT**

I-structure storage is a new type of random access storage for multi-processor systems. By employing extra "status bits," data slots can be tagged as "data-present" or "data-absent," allowing reads which precede writes to be remembered until the data arrives. In order to implement an I-structure Memory (ISM) in hardware, a sophisticated controller is required. An I-structure Memory Controller (ISMC) for the Tagged Token Data Flow Machine is developed using the IDL (Interactive Design Language) design system. The design of the controller and a discussion of the IDL System, as well as suggestions for future controllers, will be presented in this paper.

Keywords: I-structure, memory controller, dataflow, multi-processor, architecture, token, design language.

MIT Thesis Supervisor:

Arvind, Associate Professor of Computer Science

IBM Thesis Supervisor:

Dr. Harold Fleisher, IBM Fellow

## ACKNOWLEDGMENTS

I would like to thank several individuals for their assistance: Professor Arvind, for his encouragement, advice, and patience; Dr. Fleisher, Ray Phoenix, and Leon Maissel, for their all around support of my project; Professor Mort Tavel (of the Institute), for his advice; and Eva Wu, for her expert profreading.

I would also like to thank IBM Poughkeepsie, and IBM Cambridge Scientific Center for their support.

## TABLE OF CONTENTS

|                                                         | _    |

|---------------------------------------------------------|------|

| 1.0 Introduction                                        | 7    |

| 1.1 Background Information on I-Structures and IDL      | 8    |

| 1.1.1 Introduction to I-Structures                      | 8    |

| 1.1.1.1 Software Motivation for I-Structures            |      |

| 1.1.1.2 Kinds of I-Structures                           |      |

| 1.1.1.3 A Peek at the Implementation of I-Structures    | . 12 |

| 1.1.2 Introduction the IDL Design System                | . 13 |

| 1.1.2.1 High Level Overview of the IDL Design System    | . 13 |

| 1.1.2.2 The IDL Language                                | . 15 |

| 2.0 I-Structure Memory Operations                       | . 17 |

| Status Transition Diagram                               | . 18 |

| 2.1 Organization of the I-Structure Memory Controller   | . 19 |

| 2.1.1 Physical Memory                                   | . 19 |

| 2.1.1.1 The I-Store Section                             | . 19 |

| 2.1.1.2 The Free-List Section                           | . 20 |

| 2.2 Normal Operations                                   | . 21 |

| 2.2.1 Store and Fetch Operations                        | . 21 |

| 2.2.2 Allocate and Clear Operations                     | . 30 |

| 2.2.3 Reset Operation                                   | . 31 |

| 2.2.4 Allocate-Free-Space Operation                     | . 31 |

| 2.3 Service Operations                                  | . 33 |

| 2.3.1 Read and Write Absolute Operations                | . 33 |

| 2.3.2 Initialize Operation                              | . 33 |

| 2.3.3 Load Error Destination Operation                  | . 35 |

| 2.3.4 Get Free Size Operation                           |      |

| 2.4 Error Handling in the I-Structure Memory Controller | . 35 |

| 2.4.1 Types of ISMC errors                              | . 36 |

| 2.4.1.1 Status Errors                                   | . 36 |

| 2.4.1.2 Data Type Errors                                | . 37 |

| 2.4.1.3 Free List Errors                                |      |

| 2.4.2 Error Recovery                                    |      |

| 3.0 Implementation                                      | . 40 |

| 3.1 Approach to Implementation                          | . 40 |

| 3.2 Run time flexibility                                | . 41 |

| 3.2.1 Size of the Free-List                             | . 41 |

| 3.2.2 Speed of the Memory                               | . 42 |

| 3.3 Handshaking Protocols                               | . 43 |

| 3.4 Registers                                           |      |

| 3.5 Hardware Required                                   | . 44 |

| 3.6 Suggestions For Future ISMCs                        | . 45 |

| 3.6.1 Realizable Model                                  |      |

| 3.6.2 Size of the I-Structure Virtual Address Space     |      |

| 3.6.3 Dynamic Refresh                                   |      |

| 3.6.4 End-of-Block Status                               | . 47 |

| 3.6.5 Internally Delayed Tokens                         | . 47 |

| 3.6.6 Free-List-Low Warning                             | . 47 |

| 3.6.7 Status Overloading                                |      |

| 4.0 Critique of IDL                                     |      |

| 4.1 Problems With Using a High Level Language           |      |

| 4.1.1 IDL at Too High a Level                           |      |

| 4.1.1.1 The Semantics of IDL Assignment                 |      |

| 4.1.1.1 The bemantics of ibn Assignment                 |      |

| 4.1.1.3 The Counting Constructs                     | • |   |   |   |   | 54  |

|-----------------------------------------------------|---|---|---|---|---|-----|

| 4.1.2 IDL at Too Low a Level                        |   |   |   |   |   | 58  |

| 4.1.2.1 Dot Notation Imitates Nested Conditionals   |   |   |   |   |   | 58  |

| 4.1.2.2 Dot Notation Represents Decision Graphs     |   |   |   |   |   | 59  |

| 4.1.2.3 Extending Dot Notation                      |   |   |   |   |   | 60  |

| 4.1.2.4 Cleaning up Dot Notation                    |   |   |   |   |   | 61  |

| 4.2 The Enumeration Assignment Problem              | ٠ | • | • | • |   | 63  |

| 4.3 The Don't Care Input Assignment Problem         | • | • | • |   |   | 64  |

| 4.4 A PASCAL-like Language Models a Hardware Design |   |   | • |   |   | 67  |

| References                                          |   |   |   |   |   | 69  |

| Appendicies                                         |   |   |   |   |   | 71  |

| A.O High Level Code                                 |   |   |   |   |   | 71  |

| A.1 *store-t-fix Operation                          | • | • | ٠ | • | • | 79  |

| A.2 *store-t-var Operation                          | • |   |   |   |   | 83  |

| A.3 *store-u-fix Operation                          | • |   | ٠ |   | • | 91  |

| A.4 *fetch-type-stored Operation                    |   |   |   |   |   | 95  |

| A.5 *fetch-notype-stored                            | ٠ | • | • |   |   | 99  |

| A.6 *allocate Operation                             |   |   |   |   |   | 102 |

| A.7 *clear Operation                                |   |   |   |   |   | 103 |

| A.8 *reset Operation                                | • | • |   | • | • | 106 |

| A.9 *read-absolute Operation                        |   |   |   |   |   | 107 |

| A.10 *write-absolute Operation                      |   | • |   |   |   | 108 |

| A.11 *initialize Operation                          | • | • |   | • |   | 109 |

| A.12 *load-error-destination Operation              |   |   |   |   |   | 110 |

| A.13 *allocate-free-space Operation                 |   |   |   |   |   | 111 |

| A.14 *get-free-size Operation                       |   |   |   |   |   | 113 |

| B.O IDL Code                                        |   |   |   |   |   | 114 |

| B.1 *store Operations                               |   |   |   |   |   | 123 |

| B.2 *fetch Operations                               |   |   |   |   |   | 129 |

| B.3 *initialize Operation                           | • |   | • |   | ٠ | 133 |

| B.4 *allocate Operation                             | • | • | • | • | • | 134 |

| B.5 *clear Operation                                |   | • |   |   | • | 134 |

| B.6 *reset Operation                                |   |   |   |   |   | 136 |

| B.7 *allocate-free-space Operation                  |   |   | • | • | ٠ | 138 |

| B.8 *read-absolute Operation                        |   |   |   |   |   | 138 |

| B.9 *write-absolute Operation                       |   |   |   |   |   | 139 |

| R 10 *load-error-destination Operation              |   |   |   |   |   | 139 |

## 1.0 INTRODUCTION

The Data Flow Machine, [Arvind 82] and [Arvind and Iannucci 81], employs several novel ideas in support of its unconventional architecture. One of these ideas, the Incremental Structure (I-structure) [Arvind and Thomas 81], is a high level memory abstraction that requires a sophisticated control mechanism for direct hardware implementation.

A micro-code implementation of an I-structure memory controller was developed by Brian Williams [Williams 81]. Because the number of memory related instructions for a Processing Element (PE) of the Data Flow Machine had been increased, and existing instructions had been modified, a need existed for a new design of the I-structure memory controller.

In addition to a hardware design language, the IDL System [Maissel and Ostapko 82] provides a simulation, verification and documentation system for VLSI design. IDL contains several high level constructs: IF-THEN-ELSE, for example, makes it particularly well suited for the development of control mechanisms. Furthermore, the output of the IDL system can be implemented directly in hardware.

This project comprises all stages of the design of an I-structure memory controller in the IDL design system. It includes detailed design specifications, IDL code, suggestions for an improved I-structure memory controller, and discussion of the IDL Design system.

### 1.1 BACKGROUND INFORMATION ON I-STRUCTURES AND IDL

To provide some background in the areas of I-structures and IDL, a representative picture is described here from which the reader can extrapolate details. Additional information about I-structures and the Dataflow Machine can be found in [Arvind 82], [Arvind and Iannucci 81], and [Arvind and Thomas 81]; and about IDL, in [Maissel and Ostapko 82]. Any reader already familiar with I-structure memory or IDL may wish to skip the rest of this chapter.

#### 1.1.1 INTRODUCTION TO I-STRUCTURES

A data structure known as I-structures have been proposed by Arvind and Thomas to efficiently manipulate arrays in functional languages. I-structure storage, or simply I-store, and associated operations, form an implementation model for I-structures. I-store is an integral part of the Tagged Token Dataflow Machine being developed by the MIT Laboratory for Computer Science by the Functional Languages and Architectures group. This machine will be an embodiment of the U-interpreter developed by Arvind and Gostelow at the University of California, Irvine. After we have described I-store, it will become clear that storage based on these ideas will be useful for any multiprocessor machine.

## 1.1.1.1 Software Motivation for I-Structures

Functional and applicative languages (in particular the dataflow language, Id, that will execute on our machine) are free from side effects. That is, the result of an operation depends solely on its inputs (as opposed to its input and the state of the machine).

In Id, variables are used to name partial results (as opposed to memory locations) and follow the single assignment restriction: a variable can only be assigned once. However, we can still have loops. Consider the following code fragment:

BEGIN-Loop

NEW x <- f(x, <o ther variables>)

END-Loop

The x on the left hand side of the assignment statement refers to a different "copy" of x than does the x on the right. In functional languages, all structures (e.g. arrays) are treated as if they were values. Thus, the APPEND array operation is used to modify one element of an array. APPEND (x,i,v) conceptually generates a completely new copy of array x, which differs from x only on selector i. Several methods to implement structures have been suggested that reduce copying without affecting the meaning of the program [Dennis 73] and [Ackerman 77]. However, none of these methods work well for one level structures such as arrays.

While copying may be tolerable for scalars, we can not afford to make unnecessary copies of large arrays in many applications. Consider the following code fragment:

FOR i = 1 TO 10 BY 1 DO

x[i] <- f(x[i-1", <other variables>)

END-FOR

In the above code, we assign each position (i.e. selector) of x only once. Hence, it is not necessary to make a new copy of x each time we execute the body of the loop. If the compiler can detect this condition for a structure, it can avoid a lot of unnecessary copying.

I-structures can be informally defined as follows: a piece of code is an I-structure producer if it assigns the array position associated with any given array selector at most once. When this condition is met, unnecessary copying which may otherwise be implied when assigning into an array can be avoided. Furthermore, the same condition is sufficient to allow the computation to proceed in parallel on the various elements of the structure.

Thus an I-structure can be viewed as an array of slots, where slots can be filled in any order, and each slot is filled at most once. The array name can be treated as the address of the first slot (i.e. a descriptor), not unlike the name of an array in FORTRAN. The Semantics of I-structures however, permit passing the name (description) of an array to other parts of the code even before all the slots have been filled. A read request (i.e. x[i]) to a slot is processed whenever the slot is filled. If the slot is never filled, then the read request never gets an answer.

The Id compiler tries to detect if an array is being generated as an I-structure, and if it can make such a determination, the code generated avoids unnecessary copying. The compiler also uses I-structures to pass parameters to procedures and to receive results from functions.

## 1.1.1.2 Kinds of I-Structures

When compiling a high level language, two types of structures arise: structures whose elements are all of the same type, and structures whose elements are all of different types. If all of the elements are of the same type, it would be wasteful to store the type along with each element, but if all of the elements are of different types, type information must be associated with each element.

There are two kinds of I-structures: uniform and mixed. Associated with each I-structure is an I-structure descriptor (ISD). The ISD provides information about the length (number of elements), width (size of an element), and other characteristics (uniform or mixed, starting address, etc.) of the structure.

Each element of a uniform structure has the same type and hence length. Since the type can be easily stored in the ISD, type information does not need to be stored with each entry. Uniform I-structures are stored in a format called u-fix (untyped fixed-length); they are written into using a \*store-u-fix operation and read from using a \*fetch-notype-stored operation. Since no type information is stored with each entry, a type must be provided when reading a u-fix.

In a mixed I-structure, each element can be a different type and length. We have developed two formats for storing mixed I-structures. The t-fix (typed fixed-length) format allocates to each element as much storage as the largest element requires. The t-var (typed variable-length) format allocates a minimum amount of space to each element, and if a value doesn't fit, an internal pointer points to a larger slot where the value has actually been stored. This use of invisible pointers was inspired by LISP machines. The type is stored along with each element in the t-fix and t-var formats. The \*store-t-fix and \*store-t-var operations are used to write into t-fix and t-var formats respectively, and both formats can be read from using the \*fetch-type-stored operation.

## 1.1.1.3 A Peek at the Implementation of I-Structures

The implementation of an I-structure Memory (ISM) is fundamentally different from that of a conventional memory in two ways. Locations are tagged as data-present or data-not-present; and if data is not present and a read occurs, the read is "deferred" until the data arrives. The information required in order to monitor the "status" of a location is stored in a hidden status field.

Deferred reads must be allowed in the Dataflow machine because the timing of read and write requests may not have any inherent order. A reader and writer are synchronized at the I-structure memory through their data dependency.

The ISMC will assist memory managers by providing additional status information and accommodating variable length data. While the presence bit and the deferred bit are the only status bits required for a minimal implementation of I-structures, additional status information is used to assure consistency against possible compiler bugs and physical hardware boundaries. The variable length data facility abates the problem of storing amorphous arrays (using the t-var format). We can think of the t-fix and t-var formats as hardware assisted constructs.

All status information other than the presence bit and the deferred bit could be migrated to runtime software support. If we wish to carry the current analysis to an extreme, presence and deferred information could be maintained through the use of semaphores, but the runtime support would start to get out of hand.

Thus a datum stored in I-structure storage can be thought of as a node in a dataflow graph with one arc leading in, and several arcs leading out. The write request is the incoming token, and the read requests combine with the written value to form the outgoing tokens.

## 1.1.2 INTRODUCTION THE IDL DESIGN SYSTEM

IDL, developed by Maissel and Ostapko, is the hardware design environment in which the ISMC is implemented. This section provides a high level overview of the IDL system, and a brief description of the base language.

## 1.1.2.1 High Level Overview of the IDL Design System

The IDL design system allows a designer to explore, design, simulate,

verify, document, and modify a VLSI design. The system includes an interactive user interface, a file manager, a language (IDL, a register transfer level language), a compiler, an assembler, several simulators, minimization programs, and several other logic manipulation tools. The system outputs both a canonical form of the logic designed and a self documenting specification of the design. The IDL system is particularly well suited for designing Finite State Machines (FSMs).

The specification in IDL (the language) identifies two subsections of a design: the logic box, and the external world. The executable portion of the code describes the logic box and its effect on the external world. The non-executable portion of the code describes the structure of the external world. Executable statements indicate state transitions, as well as the register, bus, memory, black box (functional description), and other actions that should occur in a given state. These actions are emulated by the simulators in order to provide a complete simulation environment. The declarative statements indicate the sizes of registers, busses, memories, and other external objects; organize inputs, outputs, and feedbacks into more easily usable groups; indicate connections between the controller and external objects; and allow the user to specify strings for textual substitution.

The compiler makes certain syntax and consistency checks as it translates code into an intermediate form. This intermediate form, called regularized IDL, can be interpreted by the "High Level Simulator." Regularized IDL can be further assembled into two-level logic. This canonical sum of products form can be manipulated in a number of ways (including minimization a la MINI [Hong, Cain, and Ostapko 74]), and can

be simulated by the "Fast Simulator."

The sum of products result comes in the form of PLA (Programmable Logic Array) personality and can be translated to other forms for conversion into random logic or for various manipulations. Synthesis of a PLA from IDL output is trivial, and paths to other embodiments of the logic can take advantage of the minimized two level form.

## 1.1.2.2 The IDL Language

An IDL designer specifies both the details of the logic being designed and its interaction with other objects (registers, busses, etc.).

The first part of an IDL program consists of declarations which indicate the structure of various objects. The following IDL fragment demonstrates two declarative IDL statements.

- (1) declares registers MAR and MDR to be 16 and 32 bits respectively.

- (2) indicates that input CHAIN is obtained from the value last latched into the fourth bit of register CNTL.

IDL GROUPs, which are similar to RECORDs in programming languages, allow the designer to refer to several objects at once. IDL STRINGs allow the designer to create mnemonics for less easily understood constructs. The mnemonic may represent a hairy condition of the inputs, a value to compare against inputs, or any other textual entity the designer wishes to abstract. STRINGs are resolved by textual substitution before the rest of the program is processed.

The main part of an IDL program is the executable code. An executable statement has the following syntax:

label: IF <condition> THEN <actions> [ELSE <actions>]

A label can be thought of as a precondition. <condition> may be any boolean function of the inputs. <actions> involve changing state and controlling the external world, and thus include setting outputs, feedbacks, and control lines. The following fragment transfers the contents of REG1 to REG2 (sets a control line to make a transfer) if IN1 is true and if IN2=IN3.

IF (IN1 AND (IN2=IN3)) THEN REG1<- REG2

IDL also provides a mechanism (called dot notation) for building decision graphs. A regular label is the root of a decision graph, and dotted labels are the descendants. To activate any label, the ->label construct can be used.

The novice IDL user should be careful in dealing with the left arrow or assignment symbol. In IDL, left arrow is used for many purposes:

Declarations:

GROUP declarations: GRP foobar <- foo, bar

external connections to the PLA: FIX input <- one-bit-register

string declarations: STRING boom <- x=1 AND y=0

Executable Code:

register transfers: reg1 <- reg2 setting outputs: control <- 1

IDL syntax clearly distinguishes between the above cases, but none the less the left arrow is heavily overloaded.

## 2.0 I-STRUCTURE MEMORY OPERATIONS

After I-structure memory is initialized (using the \*initialize instruction), normal operation proceeds. Regions of memory are allocated using the \*allocate operation, read from and written into using the \*fetch and \*store operations, and deallocated using the \*clear operation.

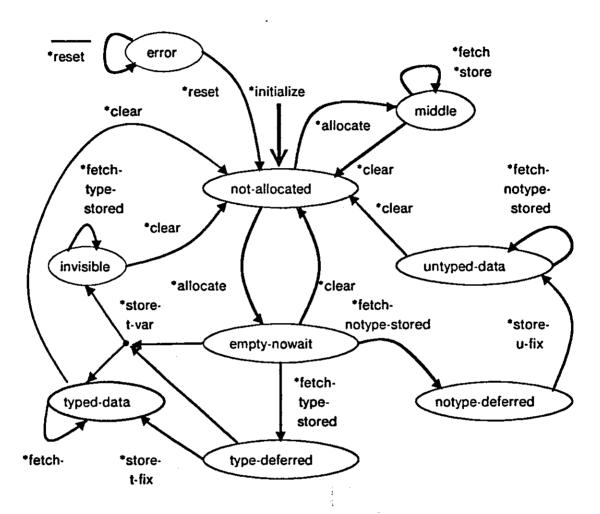

As various operations touch a word, the ISM keeps track of the status of the word by setting status bits which are invisible to the user. A Status Transition Diagram can be found in Figure 1 (next page).

ISM operations fall into two categories: normal operations and service operations. This chapter describes hardware organization of the ISMC, the error-free cases of the operations, and the error recovery technique.

## Status Transitions in the I-Store Section

All omitted arrows are branches to error

Figure 1

## 2.1 ORGANIZATION OF THE I-STRUCTURE MEMORY CONTROLLER

The ISMC is built using 288K bytes of Random Access Memory (RAM), registers, a Finite State Machine (FSM), and some random logic. This section describes the organization of these components.

#### 2.1.1 PHYSICAL MEMORY

The ISM is divided between two physical memories: a 256K byte data memory, and a 32K byte status memory. The data memory has 16 address bits and has a 32 bit wide word. The status memory also has 16 address bits, but has a 4 bit wide word. Together they store 64K words of 32 bits each, with 4 bits of hidden status associated with each word.

The 64K words are divided into two sections: the i-store and the free list. The location at which the i-store ends and the free list begins is system programmable and can be changed whenever the system is initialized.

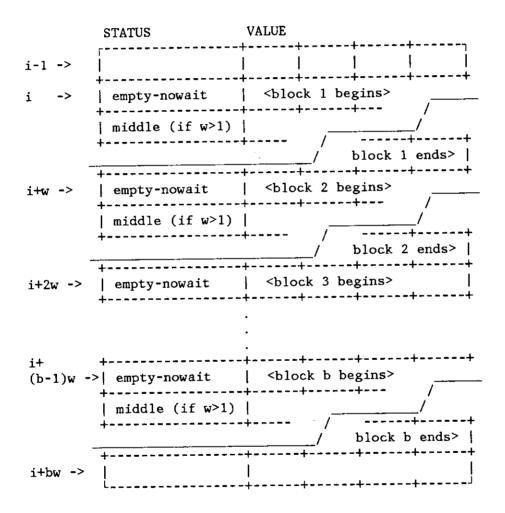

#### 2.1.1.1 The I-Store Section

Each word (32 bits of data and 4 bits of status) in the i-store section is initialized with a status of not-allocated. When a block is allocated, the first word is tagged, i.e. the status field is changed to, empty-nowait, and the other words are tagged middle. When data arrives, the first word of the block is marked. If the data is stored in place, the data is tagged typed-data or untyped-data. The invisible (pointer) status is used if the data is stored indirectly on the free list. If

fetches arrive before the data, the first cell in a block is tagged type-deferred or notype-deferred corresponding to the \*fetch-type-stored and \*fetch-notype-stored instructions.

If an error occurs at any location in the i-store, the high order bit of a status field is set to one. Information is thereby preserved about the structure of a data element that must be untangled when an error occurs. The three lower order bits of the status field are used to enumerate the values of the status field.

The details of the i-element structures can be found in the high level code declarations. A status transition diagram is given in Figure 1.

## 2.1.1.2 The Free-List Section

When the free list section is initialized, a linked list of double words (free-links) is created. The status field of the second word is used to indicate a cell at the end of the list, and the second half of the second word is used to point to the next free-link.

When a fetch is deferred, a free-link is taken from the free list and stores a destination as a deferred-link. The last two bytes are used to point to other destinations.

If a large datum is stored in an amorphous array (using \*store-t-var), a free-link is converted into a data-cell. If the datum is large enough to require two free-cells, one is converted into a data-link, and the other is converted into a data-cell.

The details of the free list structures can be found in the high level code declarations (Appendix A).

## 2.2 NORMAL OPERATIONS

All of these operations require the ISMC to check the status of a word before proceeding; \*stores, \*fetches, \*allocates, \*clear, and \*reset are included in this category.

## 2.2.1 STORE AND FETCH OPERATIONS

The \*store-t-fix, \*store-t-var, and \*store-u-fix operations are used to store data of types t-fix, t-var, and u-fix respectively; the \*fetch-type-stored operation retrieves data of type t-fix or t-var (data stored along with its type); and the \*fetch-notype-stored operation retrieves data of type u-fix (data stored without its type).

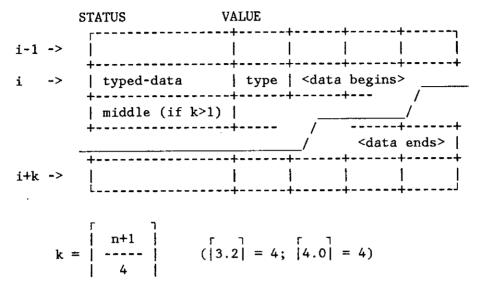

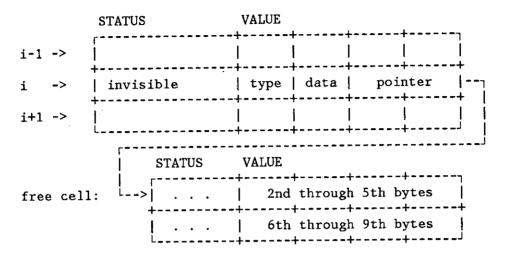

A \*store-t-fix operation creates the following data structure when storing a n-byte datum and its type at location i:

n refers to the size of the data which follows the type field. If n=5, 6 bytes are required to store the information. The 0th byte is the type, and the 1st - 15th bytes are data.

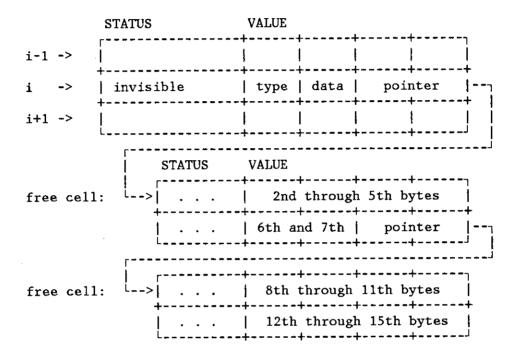

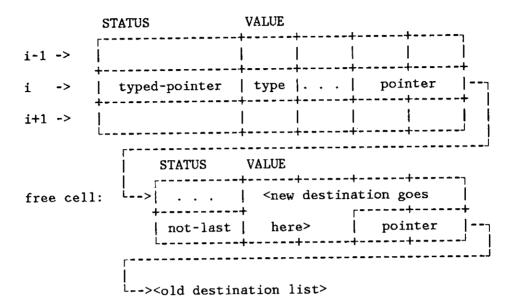

When storing a n-byte datum and type at location i, the \*store-t-var operation uses only one word at location i. If more space is required, a pointer is stored, and the overflow is placed in cells from the free list.

The following data structure is created if data of length 3 or less is stored (along with its type) using the \*store-t-var operation.

The following data structure is created if data of length greater or equal to 4 and less than or equal to 9 is stored (along with its type) using the \*store-t-var operation.

. . . = this space not used in this operation

The following data structure is created if data of length greater than or equal to 10 and less than or equal to 15 is stored (along with its type) using the \*store-t-var operation. The data-length part of the type field distinguishes the following data structure (with two linked cells) from the previous one (with one linked cell). A more elegant implementation would have used the status bits too.

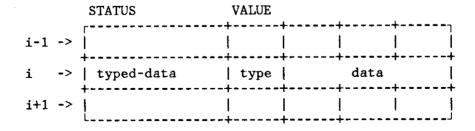

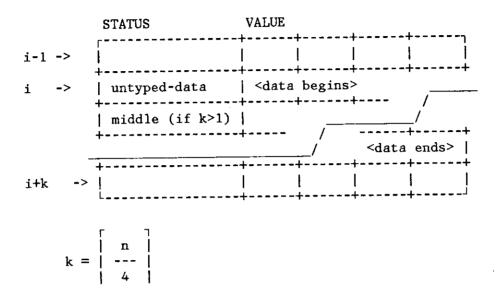

The \*store-u-fix operation operates in a similar manner as the \*store-t-fix operation. When storing a n-byte datum at location i, a \*store-u-fix operation creates the following data structure:

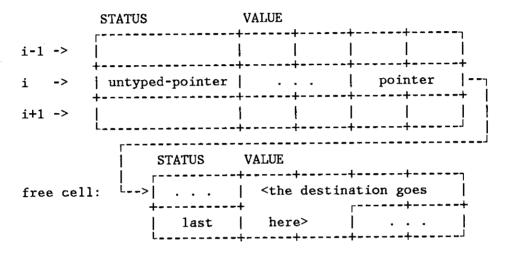

Before the \*fetch operations can be explained, the concept of a destination must be understood. In our model, a destination (48 bits) is associated with each \*fetch instruction, and indicates to which computation the fetch is to be sent. The destination is used by the token switching network to route tokens to their "destinations." Other multiprocessor systems that wish to use an I-store might simply combine a processor number with a locally unique computation identifier to form a destination. A computation identifier is needed since processors should expect to send many requests for data before the first response is recieved.

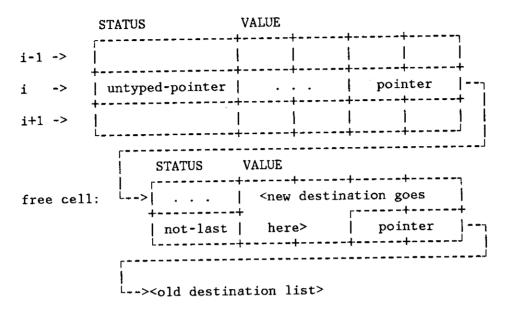

When fetching data which has already been stored, the data structure is not modified. However, when fetching data which has not yet been stored, the destination must be remembered. The destination can be CONSed into (added to the head of) an existing destination list, or the current destination will form a new list. Each destination is stored in a cell taken from the free list.

If a \*fetch-type-stored is encountered for location i, no data has been stored, and no fetches have been previously deferred at this location, a new destination list is created:

The untyped-pointer status implies deferred destinations.

If a \*fetch-type-stored is encountered for location i, no data has been stored, and fetches have been previously deferred at this location, the destination is CONSed into the existing destination list:

Note that destinations are stored LIFO style, in this operation as well as in \*fetch-notype-stored.

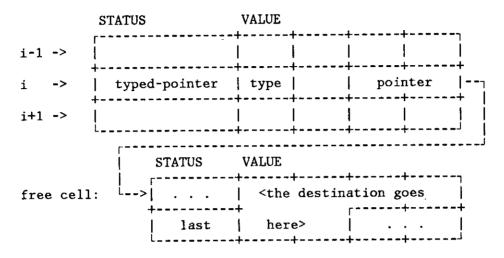

If a \*fetch-notype-stored is encountered for location i, no data has been stored, and no fetches have been previously deferred at this location, a new destination list is created (similar to the \*fetch-type-stored):

The typed-pointer status also implies deferred destinations.

If a \*fetch-type-stored is encountered for location i, no data has been stored, and fetches have been previously deferred at this location, the destination is CONSed into the existing destination list:

Again note that destinations are stored LIFO style.

## 2.2.2 ALLOCATE AND CLEAR OPERATIONS

The \*allocate operation is used to prepare an array of locations for stores and fetches. The \*clear operation is used to recover a sequence of locations, and return them to the unallocated state.

The \*allocate operation creates the following data structure when allocating b blocks each of size w words starting with location i.

The \*clear operation creates the following data structure when clearing b words starting with location i.

|          | STATUS        | VALUE      | L       |           | t    |

|----------|---------------|------------|---------|-----------|------|

| i-1 ->   |               |            |         | <br>      |      |

| i ->     | not-allocated |            |         | '<br><br> | <br> |

|          | not-allocated | <br> <br>  |         | ,<br><br> | <br> |

|          | <del>*</del>  | •          | ,       |           | •    |

|          | 1             | L          | <b></b> | <b></b>   | ++   |

| i+b-1 -> | not-allocated | ,<br> <br> |         | <br>+     | ++   |

| i+b ->   |               | ,<br> <br> | <br>+   | <br>      |      |

#### 2.2.3 RESET OPERATION

The \*reset operation is used to recover a word from an error state. The word in error is returned to its previous status. If no error is indicated in the status field, the error bit is set, and an error message is sent.

## 2.2.4 ALLOCATE-FREE-SPACE OPERATION

This operation increases the size of the free list by allocating a space in the i-store section for free cells. This space can be returned only by reinitializing the entire ISM.

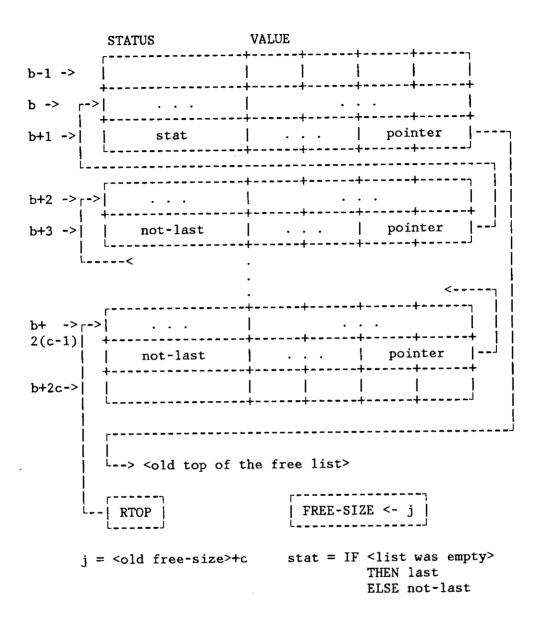

The \*allocate-free-space operation creates the following data structure given base b and number of cells c.

### 2.3 SERVICE OPERATIONS

With the exception of the \*initialize operation, service operations are not normally used by the Data Flow machine during error free operation.

## 2.3.1 READ AND WRITE ABSOLUTE OPERATIONS

These operations fetch and store a word directly. Both the status and the value fields are manipulated. No type checking is performed. These absolute operations are not intended for use during normal, error free operation; they are to be used for debugging the base system and for error recovery (by managers).

#### 2.3.2 INITIALIZE OPERATION

The \*initialize operation reinitializes the ISM. Two parameters are provided: the boundary between the data section and the free list section (stored in register BOUND); and the size at which the free list should spawn a warning message. The data section is initialized as unallocated, and the free list is linked. The contents of the status and value fields of all words are ignored. The \*initialize operation clears the entire memory.

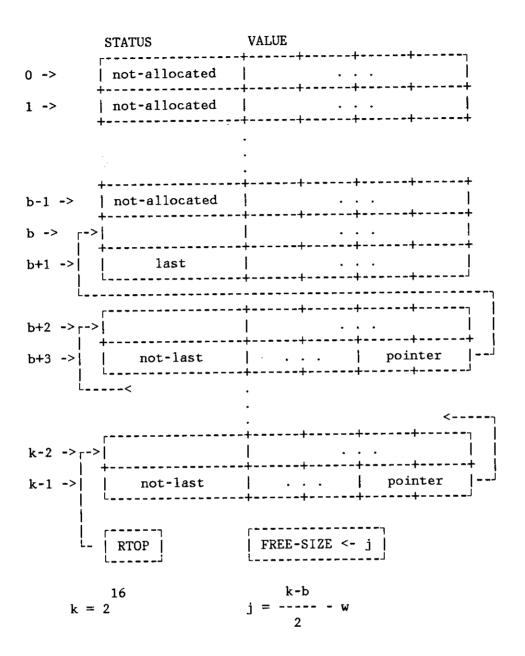

The \*initialize operation creates the following data structure given boundary b and warning size w.

# 2.3.3 LOAD ERROR DESTINATION OPERATION

A six byte register, called the error destination register contains the address of the manager to which all errors are sent. The \*load-error-destination operation loads the contents of the error destination register.

## 2.3.4 GET FREE SIZE OPERATION

This operation sends the contents of the FREE-SIZE register to the specified destination. The true size of the free list can be determined given the value stored in FREE-SIZE and a constant (provided the last time the ISM was initialized).

# 2.4 ERROR HANDLING IN THE I-STRUCTURE MEMORY CONTROLLER

Since the ISMC operates at a fairly high level, it is possible to detect certain errors. For example, any attempt to write into a location that is already occupied will be caught. Several error handling mechanisms were considered for the ISMC.

In our analysis, we assumed the existence of an error manager which can be thought of as a piece of runtime software that deals with errors and inconsistencies as they occur.

When an error is detected in the ISMC, several pieces of information

must be preserved. All of this information will be found in the token being processed, or in the location being addressed.

### 2.4.1 TYPES OF ISMC ERRORS

There are three types of errors that can occur in the ISMC: status errors, data type errors, and free-list errors.

## 2.4.1.1 Status Errors

A status error indicates that the operation being performed is inconsistent with the status of the addressed word. Classified within this category are BOUNDS errors, and status inconsistency errors.

A BOUNDS error indicates that the address provided is an illegal one. The ISM has 16 bit addresses, but not all addresses are legal arguments to operations. In particular, an address pointing to a location which is part of a free cell (or was part of a free cell and is now part of a deferred destination list or the tail of a long piece of data) is an illegal parameter; these locations must be accessed only through internal indirect references. Also, locations tagged as the middle of an element are illegal parameters to operations.

All other status errors are status inconsistency errors. Overwrite errors, inconsistent deferred fetch requests, and many others fall into this category. Most of the possible ISMC errors are of this type; see the status transition diagram for details (Figure 1).

# 2.4.1.2 Data Type Errors

A LENGTH error indicates that data is being forced into a slot which is too small to contain it. A DATA-TOO-LARGE error indicates that someone is trying to read more data from a location than it contains. Another kind of data type error is called DEFERRED-TYPE-COLLISION. When a fetch arrives with a type (\*fetch-notype-stored) and discovers that there is already a deferred destination list, and the imbedded type is different from the one arriving on the fetch, there is a type inconsistency.

## 2.4.1.3 Free List Errors

A FREE-LIST-EMPTY error indicates that the free list is out of space. Also included in this category is the FREE-LIST-LOW warning message. While this is not actually an error condition, it indicates to a manager that a potential problem situation is arising.

The free list errors will be useful tools in the emulation of the first dataflow machine. However, it is not clear how much space should be allocated to the free list or what should be done upon reaching free list space problems. When a free list error occurs, the ISM can be left in a consistent state, and operations can continue.

### 2.4.2 ERROR RECOVERY

When an error is detected in the ISMC, several pieces of information are

sent to a manager: all important information from the incoming token, and additional information depending on the brand of error. In addition, an error flag is set at the head of the implicated element (if there is one), except for the \*allocate, \*clear, and \*allocate-free-space operations which set the error bit at the location where the error was actually encountered.

Three bits are reserved for status information under normal (error free) operation. An additional status bit is reserved to indicate that an error has occurred at a given location. When an error occurs, the error bit is set and the other three bits are left untouched. Hence the ISMC can detect the previous status of a word directly during error recovery.

When a free list error occurs, the partially completed operation is undone, and the active token is returned to the communication network. The process of undoing an operation may give rise to the returning of a free cell to the free list. Hence we will be sending a free-list-overflow error when the free list is not actually empty. If we don't complain to someone and delay the token a bit, a livelock situation (discussed below) may arise.

A better solution is to send all important information both about the error and the token involved. Then, a manager can take any action that it sees fit.

The following livelock should be considered. Certain errors may cause a token to be ejected (presumably untouched) back into the communication network. If the free list is empty and we need to defer a destination,

for example, we might not want to mark the location being addressed. If the ejected token returns before the error is handled, (a possibility if the communication is "intelligent") another error token is generated, and the process repeats. To deal with this situation, several possibilities arise. We could mark the tokens so that the communication network sends them on a slower path. We could store tokens locally. If the free list is not full, we could put them on the free list. We could redirect the tokens to a manager. Embedding all important information in the error message being sent to a manager is the most promising compromise.

Block commands (allocate and clear) involve several groups of words in memory. If an error occurs while executing a block command, follow the scheme as outlined above, tell a manager how much of the block command has been completed, and cease processing the block command.

# 3.0 IMPLEMENTATION

## 3.1 APPROACH TO IMPLEMENTATION

In designing the ISMC, several stages of the design were developed in succession. An informal paper design describing the function and structure of the ISMC was the first step. Then a formal high level design in the form of non-executable ALGOL-like code was drawn up (Appendix A). Detailed descriptions of the algorithms were specified, and all of the data structures were then presented. The final stage of the design was the IDL code. The IDL description can be implemented in hardware, and both algorithmic and bookkeeping details are present. Since this code is executable, it can be simulated and verified.

The evolution of the ISM is a continuous process. By the time this paper had been completed, the design had become outdated. The goal of this project was to present a consistent model of the ISMC as it existed around Fall 1982.

For several reasons, the IDL code for the ISMC was not simulated. The functionality of the design was being verified by PASCAL programs derived from the High Level Code in Appendix A. Also, the ISMC design severly stressed the IDL system. Simulation using the current implmentation of IDL would have been quite difficult. Since the goal of this project was to develop an ISMC design and to study the IDL design system, and since the ISMC design had already become obsolete, IDL simulation became a less important part of the project.

### 3.2 RUN TIME FLEXIBILITY

Because some of the details of the design are not known at design time, the prototype may be the vehicle most appropriate for determining the values of these parameters. Thus, in order to allow some flexibility in the design of the I-structure memory controller, several design constraints were left as parameters.

### 3.2.1 SIZE OF THE FREE-LIST

It is unclear how memory should be divided between the i-store and free list sections. If the free list becomes empty, deferred fetches cannot be accommodated, and large elements of amorphous arrays cannot be stored. It is not even clear whether a given split will be adequate across differing applications, or across the lifetime of a single program. Hence in order to allow flexibility in the prototype engine, several techniques have been employed which allow dynamic monitoring, error checking, and recovery.

When the memory is initialized, the size of the free list section is provided as a parameter. Since a manager does not have time to wait for the adjoining section to clear in order to enlarge the free list, the boundary between the i-store and free list sections cannot be easily changed on the fly. If free space becomes scarce, the \*allocate-free-space operation can convert i-store space into space for the free list. Only after a manager flushes all structures from this ISM can the space be returned by re-initialization.

The size of the free list is tracked by an up-down counter in the ISMC. The value maintained in this counter is offset from the size of the free list by an amount specified at the last initialization. This technique allows a free-list-low warning to be sent to a memory manager at a predetermined list size. In addition, the value of the counter can be monitored dynamically by any manager. The actual end of the free list is marked in the status bits of the last free-link of the list.

### 3.2.2 SPEED OF THE MEMORY

In an attempt to provide flexibility for the implementation and a possibility for upgrading the design by plugging in a faster FSM or RAM, the relative speeds of the FSM (presumably a PLA) and the slave RAM have been made a programmable option. By setting dip switches, the memory may operate in less then one, two, three, or four PLA cycles without impacting the design.

## 3.3 HANDSHAKING PROTOCOLS

Three handshaking ports have been set up to allow the ISMC to communicate with the outside world: one at the source of tokens, one at the receiver of newly formed tokens, and one for the hard interrupt line. Handshaking is accomplished through the use Set Reset (SR) latches; the sender sets the SR latch, and the receiver resets it. In order to avoid clumsiness in the IDL design, these SR latches have been modeled as simple one bit registers, each with two sources of information. By convention, the sender only sets a register when it contains a zero, and the receiver only resets a register when it contains a one.

### 3.4 REGISTERS

The registers can be separated into four categories: input registers, transaction registers, output registers, and system registers.

The input registers are used to receive tokens, two bytes at a time. Once a token has been accepted, it can be transferred all at once to transaction registers. A one-bit register is used to synchronize the supplier of data with the input section, and a feedback is used to synchronize the input section with the transaction section.

The transaction registers are used to interact with physical memory.

This category includes registers to hold the active token, a Memory Address Register (MAR, 16 bits), and a Memory Data Register (MDR, 36 bits,

The output registers are used to output tokens one at a time. Once a token is ready to be exported, it can be transferred all at once from the transaction registers to the output registers. A feedback is used to synchronize the output section with the transaction section. I have assumed that a token buffer exists between the ISMC and the communication network.

The system registers hold the value of certain ISM variables. BOUND (16 bits), which points to the first word in the free list section, is loaded each time the ISM is initialized. RTOP (16 bits) points to the top of the free list. ERRDEST (48 bits) contains the destination to which error messages are sent. This register is loaded explicitly with a \*load-error-destination operation. FREE-SIZE (16 bits) is related to the size of the free list. When the ISM is initialized, FREE-SIZE is set to the size of the free list minus a constant (a parameter of initialization). When FREE-SIZE reaches zero, a warning is sent to the error destination. The end of the free list is marked in the status field of the last free cell. FREE-LIST-STATUS (1 bit) indicates whether or not the free list is empty. PE-NUMBER (10 bits) contains the enveloping PE's number. IEXTRA (16 bits) is an extra register for pointer manipulation.

### 3.5 HARDWARE REQUIRED

The ISMC design required about 1500 lines of IDL code. This design stressed the IDL system to the limit, even when IDL operated in a four

megabyte virtual region (under APL). We were able to compile and assem-

ble the ISMC to PLA personality (two level logic). The following sta-

tistics were gathered:

Controller:

- Product terms: 887

- Inputs (no feedbacks): 151

- Outputs (no feedbacks): 316

- Feedbacks: 91

Registers: 718 bits

Comparators: 40 bits

3.6 SUGGESTIONS FOR FUTURE ISMCS

The ISMC presented is a consistent model. Since this project included

implementing the ISMC, at some point the design had to be frozen and

completed. The following considerations were not included at freezing.

3.6.1 REALIZABLE MODEL

The controller presented in this thesis, while realizable, is not a re-

alistic design. A realistic design, for example, would have one or more

busses. Without bussing, the number of control lines and data wires is

too large. Some binary counters were included in the controller that

(as it turns out) are better placed as external objects. Enough has

been learned from this design, however, that the next generation can

45

claim feasibility.

# 3.6.2 SIZE OF THE I-STRUCTURE VIRTUAL ADDRESS SPACE

At a late point in this design, we decided that each ISM could have up to 24 bits of address space. Anywhere between 16 and 24 bits could be implemented. The number of free cells, however, was not to exceed 32K so that the present data structures would not need to be modified.

The ISMC presented here assumes a 16 bit address space. Several conceptually simple modifications would accommodate this change. The only delicate matter is dealing with two different length pointers, a full length pointer (16-24 bits, depending on the implementation) for externally generated references, and a short pointer (16 bits) for internally indirected references.

### 3.6.3 DYNAMIC REFRESH

This ISMC does not support the refresh cycle required for a dynamic memory. With the current design, only static memories are supported. Support for dynamic memories may become important at some time in the future.

# 3.6.4 END-OF-BLOCK STATUS

A new status code indicating the end of an allocated block can be assigned, allowing us to avoid reading an additional word in the case of a size mismatch. Overhead that did not impact error free operation was considered secondary in this design.

### 3.6.5 INTERNALLY DELAYED TOKENS

An additional register could be added to the system registers that pointed to a list of internally delayed tokens. It may be desirable to temporarily swallow some tokens that are causing errors. If this is done, a more complicated structure than a list might be desirable (for example, a tree).

### 3.6.6 FREE-LIST-LOW WARNING

A warning is sent to a memory manager every time the free list size reaches zero (the free list may or may not be empty). If the size oscillates around zero, many warning messages might be sent; perhaps only one is needed.

# 3.6.7 STATUS OVERLOADING

The status bits identify the structure of the associated word. If the i-store and free list sections were physically disjoint, the address would provide additional status information implicitly. This allows us to overload the assignments of the status bits.

The two sections are not physically disjoint. Once an \*allocate-free-space operation has occurred, there is no way to use address information to imply structure. The current design fully utilizes the encodings for the i-store section. We can minimize the effects of overloading by assigning all list status codes in such a way that they overlap with error codes of the i-store section.

In the next generation, all possible status possibilities should be enumerated differently, either by adding a status bit, or by modifying the error handling mechanism. In the current model, one bit indicates if an error has occurred, allowing us to preserve information about the previous structure. If we relax this model and assign a single code to "ER-ROR," we will have plenty of room for the other assignments.

# 4.0 CRITIQUE OF IDL

# 4.1 PROBLEMS WITH USING A HIGH LEVEL LANGUAGE

When using IDL, two types of problems related to language arose: IDL is at too high a level to notice certain details, and IDL is at too low a level to conveniently express certain constructs.

### 4.1.1 IDL AT TOO HIGH A LEVEL

# 4.1.1.1 The Semantics of IDL Assignment

The following code fragment involving two inputs and a latched feedback is translated into PLA personality:

| Code Fragment 1 | PLA 1                          |      |

|-----------------|--------------------------------|------|

| IF f            | <sub>Г</sub> -<<- <sub>7</sub> |      |

| THEN $f <- x$   | xyf f                          |      |

| ELSE f <- y     |                                |      |

|                 | 0 - 1    R                     | (PO) |

|                 | 1 - 1    S                     | (P1) |

|                 | - 0 0    R                     | (P2) |

|                 | - 1 0    S                     | (P3) |

And the following similar code fragment is translated into PLA personality:

In any programming language, if f, x, and y were booleans, code fragments 1 and 2 would have identical semantics. In IDL, these fragments are only equivalent when the fedback term is latched with certain latches, ones that hold their values between cycles unless otherwise instructed. In addition, the fragments are taken out of context. If the context contains statements with overlapping conditions, they may interfere in such a way as to make the fragments distinguishable.

In code fragment 1, product terms (P1) and (P2) assert that f is set (or reset) to its current value. If f is fedback through a SET DOMINANT latch, a common and typical latch for feedbacks, and if there is no interference from other terms, as discussed below, (P1) and (P2) are not needed. When (P1) and (P2) are removed from PLA 1, PLA 2 results.

Interference caused by overlapping product terms is demonstrated below:

| Code Fragment 3           | PLA 3                                                                                    |

|---------------------------|------------------------------------------------------------------------------------------|

| IF f AND g<br>THEN f <- x | x y f g h f                                                                              |

| IF f AND h THEN f <- y    | 0 - 1 1 -    R (P6)<br>1 - 1 1 -    S (P7)<br>- 0 1 - 1    R (P8)<br>- 1 1 - 1    S (P9) |

Assume that f is fedback through a a SET DOMINANT latch. A SET DOMINANT latch holds its value unless otherwise instructed, and the SET command dominates over the RESET command. If f, g, and h are all true, there is a parallel assignment to f. This type of parallel assignment is resolved in a PLA by the "natural" pairwise ORing of x and y; f receives the value (x OR y). While product terms (P7) and (P9) both have the property that they set f to one based on the precondition that it is already set to one, we cannot eliminate (P7) and (P9). If the condition (f AND g AND h AND (x  $\neq$  y)) arises and we only test terms (P6) and (P8), f will be set to zero. The terms which were previously redundant are now needed to explicitly override the RESET terms.

The confusion arises primarily because we are looking at IDL as if it were a conventional programming language such as ALGOL. In ALGOL, variables (analogous to feedbacks) maintain their value unless explicitly assigned. Hence, the ALGOL analogies of code fragments 1 and 2 are equivalent. In addition, ALGOL has no notion of parallel action. The confusion demonstrated by code fragment 3 would simply not arise in ALGOL.

IDL uses assignment to directly describe PLA personality (setting bits in the OR plane in the column corresponding to the output recieving a value) rather than the abstract notion of value transferal. While IDL assignment is frequently equivalent to value transferal, this is not always the case, as demonstrated above. The direct analogy in programming involves expressing single ideas partly in machine language. Consider the following line of PASCAL code:

x := <contents of machine register number 8>

Although this would be a severe violation of modern programming ideology, it might not be such anathema in a hardware design language such as IDL. In fact, this mixed level notation may be necessary in order to generate an efficient implementation.

In order to avoid the confusion caused by IDL assignment, we could abandon the mixed level notation in favor of a purely abstract language. We still would be able to specify the hardware and types of latches, but the algorithms for automatically generating an efficient implementation are not obvious. It is easy to generate an implementation in hardware that uses whichever latch we desire, but cleverly using a given latch is not an easy process to automate.

As long as the IDL user realizes the difference between IDL assignment and ALGOL-like assignment, he can avoid much difficulty. Detecting possible problems due to overlapping assignments is not difficult, and the automatic reporting of such potential errors may be a useful addition to the IDL system.

## 4.1.1.2 Hidden Control Signals

The IDL system allows the designer to indicate register transfers in "assignment-like" statements, generates control signals for these transfers, and simulates the transfers automatically. This high level abstraction does not permit the user to talk about the control signal directly.

At a particular place in the IDL code (let's sat point x), the MDR already contained the data present in a particular register; call it R1. In other parts of the code, similar conditions caused MDR to be assigned R1. At point x, it does not matter if the control signal "MDR<-R1" rises; in fact, we would like to indicate this don't care situation in the IDL code. All we can do is indicate that the transfer occurs, or it doesn't. All system generated control signals have this weakness.

If we say "MDR<-R1", a one will be placed in the OR plane in the column corresponding to the "MAR<-R1" control signal. If we don't say "MDR<-R1", a zero is implicitly placed in the OR plane.

The problem occurs because we cannot talk about control signals directly. We would like to be able to express the idea that the control signal "R1<-R2" (transfer the contents of R2 to R1) is a valid output and can be manipulated. The following action should be expressible:

"R1<-R2" <- <don't care>

## 4.1.1.3 The Counting Constructs

IDL will automatically generate PLA personality to perform some arithmetic functions such as incrementing and decrementing a set of feedbacks which are collectively treated as an integer.

Part of the ISMC design includes "switch programmable" inputs which specify the relative cycle times of the PLA and the physical memory. The architect is thus allowed to specify the number of PLA cycles the controller should wait between memory accesses.

There are basically two approaches in accommodating this flexibility: load a constant initial value (such as zero) and count (up or down) until the count matches the value of a set of inputs, or load a value from inputs and count (up or down) while testing for a match with a predetermined constant value. These two approaches will be referred to as the set-and-compare paradigm and the load-and-test paradigm respectively. The following code fragments demonstrate the approaches.

Code Fragment 4

Load-and-Test Paradigm:

L1: IF <memory access>

THEN count <- memtime

-> L2

L2: IF count = 0

THEN <continue>

ELSE count <- count-1

% remain in this state

Code Fragment 5

Set-and-Compare Paradigm:

L1: IF <memory access>

THEN count <- 0

-> L2

In my first design of the variable memory speed feature, I first transferred the incoming switch settings to feedbacks, and then counted down to zero (load-and-test). While the load-and-test paradigm would be the obvious choice in micro-programming (due to the jump-on-zero instruction), the set-and-compare paradigm turned out to be superior in a this design. The considerations which effect the choice of paradigms are discussed below. Unfortunately the code segments for the two prototypes are similar, and it is not at all obvious at the high level which one is desirable.

The cost of incrementing is the same as the cost of decrementing, and either one could be applied to both paradigms. Although testing for zero is unit cost, the cost for comparing two inputs for equality and the cost for transferring a value from inputs to feedbacks depend on the details of the PLA implementation.

The cost of testing two n-bit quantities for equality is different from the cost of testing for inequality. If we have a PLA with one bit decoded inputs, testing for equality takes two raised to the power n product terms (n is the number of bits in the counter), and testing for inequality takes two times n product terms. We have a PLA with two bit decoded inputs: testing for equality takes one product term, and testing for inequality takes n product terms. We may or may not be able to trade off the true and complement tests.

The cost of transferring a n-bit value from inputs to feedbacks also depends on the PLA. If we use sophisticated latches, it takes two times n product terms. (A trick allows us to load SR latches from inputs using

only n+1 terms.) If we use simple polarity-hold latches (D type), the cost of the transferal drops to n product terms. Simple latches, however, make the counting process more expensive. If the condition <memory access> is complex, counting becomes even more expensive.

Since, the discussion has only addressed the microscopic picture, the most serious issue has not yet been addressed. We shall assume for the remainder of this discussion that we have two bit decoded inputs, and that the cost of a test for equality is therefore one product term. Every time we count up or down in some given state we require several lines of PLA personality (three lines for unlatched (D type) feedbacks, and two for many complex latches). If the condition associated with the state is complex, we must multiply by the number of conjuncts. We need approximately 5 product term for EACH memory access. There are more than 150 reads and writes in the ISMC code. We cannot afford to devote so many product terms to counting.

Fortunately, there is another technique similar to the set-and-compare, force-and-compare, which allows us to solve the counting problem much more efficiently. We can set up an independent process in the PLA, a counter which runs continuously, with the provision that its value may be overridden at any point. The new model involves forcing the count to 3 (binary 11) at memory access, and counting until the count matches a set of inputs. Setting the counter to all "ones" is possible because of the way a PLA operates. By performing a parallel assignment of all "ones" to the count variable, we can override any other value.

The following code fragments demonstrate this approach:

Code Fragment 6

Force-and-Compare Paradigm:

Universally: count <- count+1

L1: IF <memory access>

THEN count <- '111...1'

-> L2

L2: IF count = memtime

THEN <continue>

ELSE % remain in this state

This solution demonstrates the set-and-compare paradigm. One product term is required to force the count, and another to compare the count with inputs, giving a total of two product terms for each memory access.

We have been able to decouple the details of counting from the business of memory access. Unfortunately, we are relying on a PLA trick which allows us to override any assignment with the all ones value. Hence, a solution analogous to load-and-test is not possible.

Several interesting points stem from this analysis.

- There is no difference between incrementing and decrementing. In fact the details of counting become fairly unimportant if we can arrange for the code to occur only once.

- 2. The solution chosen was not drawn from microprogramming. We have employed a technique which has no analog in programming.

- 3. All three paradigms are applicable in different domains, and the designer must know about the details of the implementation in order to make an intelligent choice. Unfortunately, the difference between the techniques are not obvious in the IDL code. Also, automatic translation of one paradigm to another does not appear easy. If an efficient implementation is to be obtained, it must be designed that way.

- 4. In our analysis we assumed that the counting was done inside the PLA. All three techniques become similar if we count and compare/test external to the PLA. This new solution is as efficient as force-and-compare, and it does not depend on two bit decoding or parallel assignment. What it does is remove from the PLA a chunk of logic (arithmetic) which we can implement efficiently externally.

### 4.1.2 IDL AT TOO LOW A LEVEL

## 4.1.2.1 Dot Notation Imitates Nested Conditionals

The IDL language has made an important leap in the direction of structured language. The best example is IDL's use of the IF-THEN-ELSE construct. Unfortunately, IF-THEN-ELSE was not carried far enough to include nested decision trees. IDL does have a dot-notation construct however, which can be used to imitate nested IF-THEN-ELSE:

Code Fragment 8 Code Fragment 7 Nested IF-THEN-ELSE Dot-Notation L1: IF c1 L1.: IF c1 THEN -> L1.2 THEN IF c2 ELSE -> L1.3 THEN a1 L1.2: IF c2 ELSE a2 ELSE IF c3 THEN al ELSE a2 THEN a3 L1.3: IF c3 ELSE a4 THEN a3

ELSE a4

The above dot notation is only slightly more clumsy than the IF-THEN-ELSE version. A more complex decision structure, however, aggravates the situation. The reader may wish to compare the High Level code presented in Appendix A with the IDL code presented in Appendix B. For example, compare the first few statements associated with the \*store operations in the two versions of the code. Although the comparison is not quite fair, it is indicative of the difficulty. Dot notation has the full power of the IF-THE-ELSE construct, but it loses the advantage gained by positional association.

### 4.1.2.2 Dot Notation Represents Decision Graphs

Dot notation does have the interesting property that it is more general than nested IF-THEN-ELSE. While nested IF-THEN-ELSE is used to embody a decision process representable by a tree, dot notation can be used to embody any decision process representable by a Directed Acyclic Graph (DAG, the class of trees are a proper subset of the class of DAGs). Although DAGs can be "converted" into trees by replicating decision nodes, this conversion tends to clutter the code. Consider the following code fragments and corresponding graphs:

Code Fragment 9 Code Fragment 10 Dot-Notation Nested IF-THEN-ELSE L1.: IF c1 L1: IF c1 THEN -> L1.2 THEN IF c2 ELSE -> L1.3 THEN S4 L1.2: IF c2 ELSE al THEN -> L1.4 ELSE IF c3 ELSE a1 THEN S4 L1.3: IF c3 ELSE a2 THEN -> L1.4 ELSE a2 L1.4: S4

While the nested IF-THEN-ELSE may appear more elegant, it repeats a statement. The statement itself may be a graph of decisions with many conditions and actions. Unfortunately, a linear-textual language cannot represent DAGs while taking advantage of the positional adjacency of nesting.

# 4.1.2.3 Extending Dot Notation

The generality of dot notation can be carried a step farther. Under the current syntax, a dotted label consists of a root name and an intermediate node name. In the above example, L1 is the root name and 2, 3, and 4 are the intermediate node names. The tie of intermediate nodes to any particular root can be lifted by naming intermediate nodes independently. The following code is a relaxed version of Code Fragment 9.

Code Fragment 11

L1: IF c1

THEN -> .2

ELSE -> .3

.2: IF c2

THEN -> .4

ELSE a1

.3: IF c3

THEN -> .4

ELSE a2

.4: S4

While this change may not appear dramatic, one can imagine situations (frequent in the IDL code for the ISMC) in which several roots could lead to a common intermediate node. Unfortunately, the syntax duplicates the entire decision each time. This idea has no parallel in structured programming.

# 4.1.2.4 Cleaning up Dot Notation

There is an apparent inconsistency in IDL's view of dot notation. The research report on IDL [Maissel and Ostapko 82] describes the use of dot notation on pages 23 through 26. Code fragments 12 and 13 (below) are viewed as equivalent.

And code fragments 14 and 15 (below) are viewed as equivalent.

Code Fragment 14 Code Fragment 15

L1: IF c1 L1.: IF c1

THEN  $x \leftarrow 1$  THEN  $x \leftarrow 1$

L1: IF c1 / c2 L1.: IF c1

THEN  $y \leftarrow 1$  THEN -> L1.2

L1.2: IF c2

THEN y <- 1

But code fragments 12 and 14 are not viewed as equivalent.

In order to have some action take place at an intermediate node in a tree, the action must be isolated. Similarly, unisolated actions may or may not occur, even when the conditions up to this point in the decision structure have been met. Additional conditions may impact actions which seem to occur higher in the tree. The historical reasons for this apparent inconsistency are no longer applicable.

There is a strong analogy between dot notation and nested IF-THEN-ELSE, and GOTOs and conditionals. Since the IF-THEN-ELSE construct is not supported by the same complement of structured constructs as the programming version is, one can make a very strong case for dot notation. I am confident that a more usable system can be developed (without sacrificing power) by moving toward structure and away from dot notation.

### 4.2 THE ENUMERATION ASSIGNMENT PROBLEM

The problem of state assignment (discussed extensively in the literature, [Marcus 75], [Ward 68], [Miller 65], and many others) is well known and difficult.

A similar problem arose in my study of the ISMC. In the design of the i-store section, eight distinct structures arose for the data word: not-allocated, empty-nowait, typed-data, untyped-data, middle, invisible, type-deferred, and notype-deferred. The actual assignment of binary values to the various enumerations of the status bits have no intrinsic significance. The assignment will, however, have a significant impact on the logic required to operate on these bits.

This Enumeration Assignment Problem is common to the designer of digital systems. The designer must collect all decisions that will be asked of these bits and make an assignment that optimizes the decision. In practice, it is not particularly difficult to make some reasonably efficient assignment. In a design language such as IDL, however, we would like to defer the assignment as much as possible, and allow the assignment to change (automatically perhaps) as we modify the decisions made.

In the design, we wish to operate conceptually in a multiple valued logic. All decisions represent two valued predicates in the larger logic. When the time comes to implement our design in [boolean] hardware, we wish to use the list of predicates to make an assignment that yields the simplest realization of these predicates. The problem is slightly more complex than presented so far. Various variables may be related to each other in such a way that the best enumeration assignment cannot be found independently.

## 4.3 THE DON'T CARE INPUT ASSIGNMENT PROBLEM

When certain combinations of inputs arise, we may not care which branch of a decision to follow. There is no way of indicating in IDL that a don't care should be associated with a decision rather than an output. Even if we express this fact using some construct, the minimization problem generated by this kind of an input don't care is different from the problem of minimizing several functions of several variables.

Consider the following Karnaugh Map, which should be considered a boolean function on two variables, and the code fragment that uses it.

The don't care at the ab=10 position means that both the THEN and the ELSE branch provide an acceptable assignment of values to x and y. If we expand the statement into maps for x and y, propagating the don't care, the following Karnaugh maps result:

| Karnaugh Map 2 | Karnaugh Map 3 |

|----------------|----------------|

| x              | У              |

| a              | a              |

| ъ   0   1      | ь  0 1         |

|                |                |

| 0   0   ?      | 0   1   ?      |

|                |                |

| 1   1   1      | 1   0   0      |

|                |                |

The don't cares at the ab=10 positions have been decoupled. There are four ways of assigning the two don't cares, but only two of those assignments preserve the semantics of the decision structure. If the don't cares at ab=10 on Map 1 and Map 2 are both assigned the same value (either 1 or 0), we encounter a peculiar situation. When ab=10, the values of outputs x and y will be equal to each other. These values are inconsistent with both the THEN and ELSE branches of code fragment 16.

If we want to move the input don't cares to the output side, we must also carry along some constraints on their assignments. In the example above we must assert that the assignments of the don't cares for x and y must be opposite values.

This problem would never have arisen if we could not express don't cares of the input variety. In fact, code fragment 16 cannot be expressed using only output don't cares. Another syntax for expressing input don't cares is the IF-EITHER-OR statement:

IF <condition>

EITHER <actions>

OR <actions>

We can compress logic to two levels and preserve the semantics of our decision structures as follows. Uniquely label all input don't cares.

When we multiply out the multiple level logic, the don't cares are linked by their labels (some will be in inverted form). Whenever we assign a don't care, all instances of the don't care must be assigned the same value. This is by no means a minimization algorithm. This problem is clearly a superset of "classical minimization."

Even though we don't know how to solve the input don't care assignment problem precisely, we can try applying a few heuristics. Boolean maps can be minimized locally. We might also consider the sizes of the THEN and ELSE branches if we are working on a decision tree. Consider the following Karnaugh maps.

| Karnaugh Map 4<br>AB |       |      | DE            | Karnaugh Map 5 |        |           |    |    |       |

|----------------------|-------|------|---------------|----------------|--------|-----------|----|----|-------|

| C                    | 00    | 01   | 11            | 10             | FG     | 00        | 01 | 11 | 10    |

| 0                    | 0     | 0    | ?             | 1              | 00     | 0         | 0  | ?  | ?     |

| 1                    | ?     | 0    | 1             | 1              | 01     | 0         | ?  | 1  | ?     |

| we assign so that:   |       | 11   | <br>    ?<br> | 1              | 1      | <br>    ? |    |    |       |

|                      | ON SE | ET = | A not         |                | 10<br> | ?         | ?  | ?  | ?<br> |

In the case of Karnaugh map 4, the best assignment seems to be assigning the don't cares in such a way that the ON SET = A, and the OFF SET = not A.

The most promising assignment for Karnaugh Map 2 is assigning the 0101 spot to one boolean value, and assigning the rest of the spots to the other value. If 0101 is assigned 0, then the OFF SET requires the single term (NOT F)(NOT D) and the ON SET requires the terms F and D. If 0101 is assigned 1, then the ON SET requires the single term EG and the

ON SET Requires the terms (NOT E) and (NOT G). Depending on the complexity of the THEN and ELSE branches, one of the two choices can be made. If the THEN branch is "heavier," we assign the spot to 1. If the ELSE branch is "heavier," we assign the spot to 0. In any case, assigning all zeros or all ones is probably non-optimal.

## 4.4 A PASCAL-LIKE LANGUAGE MODELS A HARDWARE DESIGN

During the course of this project, I wrote a version of the ISMC in PAS-CAL-like pseudo code, and subsequently in IDL. Also, our group undertook an effort to translate my pseudo code into PASCAL for use in a simulator for our dataflow machine. In this section, I will discuss several points where the designs were dissimilar.

The IDL code tended to be non-reentrant. When copying code to a similar section of the design, extreme caution had to be used in changing all references to state (labels). The PASCAL did not suffer from this problem, and it is not inherent in the hardware.

PASCAL data structures could not be used to directly model the hardware, that is, without loosing the advantages of having the data structure in the first place. When a VARIANT-RECORD is used in PASCAL, there is implied storage (to discriminate the cases). The very bits which are beyond our control are the most critical ones. Those are the bits by which decisions are to be made. We must have close control over them or know that the compiler will do a particularly good job in dealing with them.

The PASCAL code does not have any sense of time (other than sequences). This issue is of particular concern in IDL as it must be in any hardware design system. As a direct result of this problem there was no way to express the idea of a hard reset in PASCAL.

Many important details (from the hardware point of view) were glossed over in PASCAL. One of these issues involve passing tokens to the system, and transferring values within it. When we say x:=y in software, no one asks how the value travels. The details of value transferal cannot be ignored in hardware.

### References

## [Ackerman 77]

Ackerman, W. B. A Structure Memory for Data Flow Computers. Technical Report TR-186, Laboratory For Computer Science, Massachusetts Institute of Technology, Cambridge, Massachusetts, August 1977.

### [Arvind 82]

Arvind and Members of the Functional Languages and Architecture Group. The Tagged Token Dataflow Architecture. Technical Report (unpublished), Massachusetts Institute of Technology, Cambridge, Massachusetts, August 1982.

### [Arvind and Iannucci 81]

Arvind and Iannucci R. A. Instruction Set Definition for a Tagged Token Data Flow Machine. Memo 212, Computation Structures Group, Laboratory for Computer Science, Massachusetts Institute of Technology, Cambridge, Massachusetts, December 1981 (updated May 1982.)

## [Arvind and Thomas 81]

Arvind and Thomas, R. E. I-Structures: An Efficient Data Structure for Functional Languages. Memo 178, Computation Structures Group, Laboratory for Computer Science, Massachusetts Institute of Technology, Cambridge, Massachusetts, October 1981.

### [Dennis 73]