© Bluespec, Inc., 2006

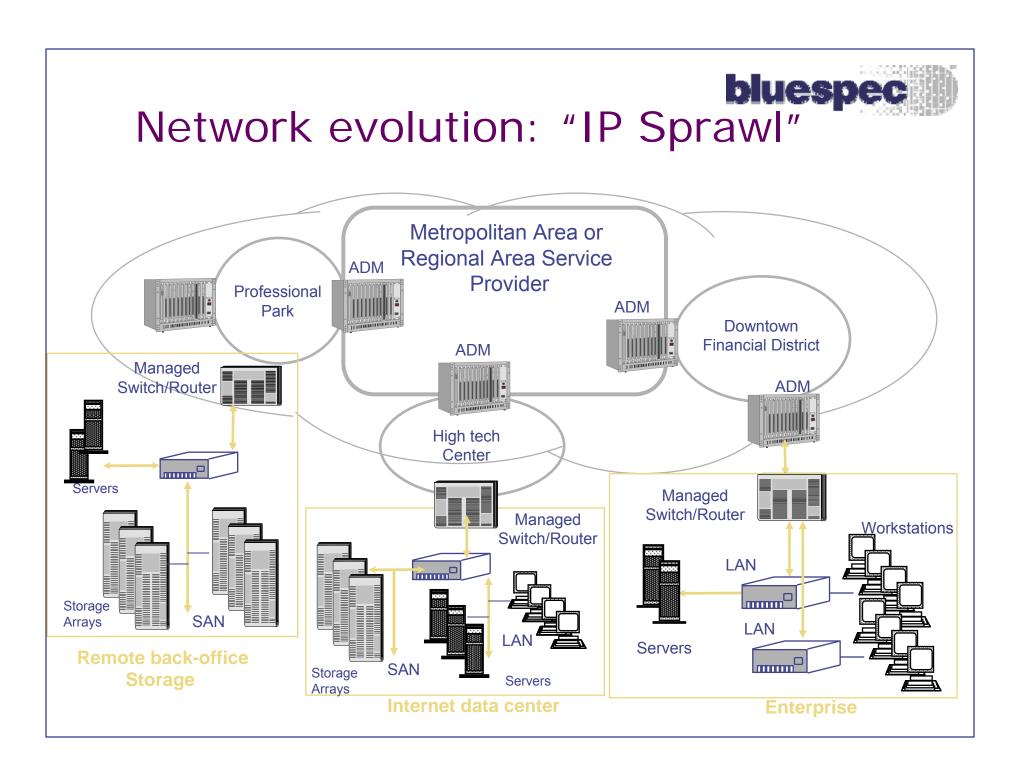

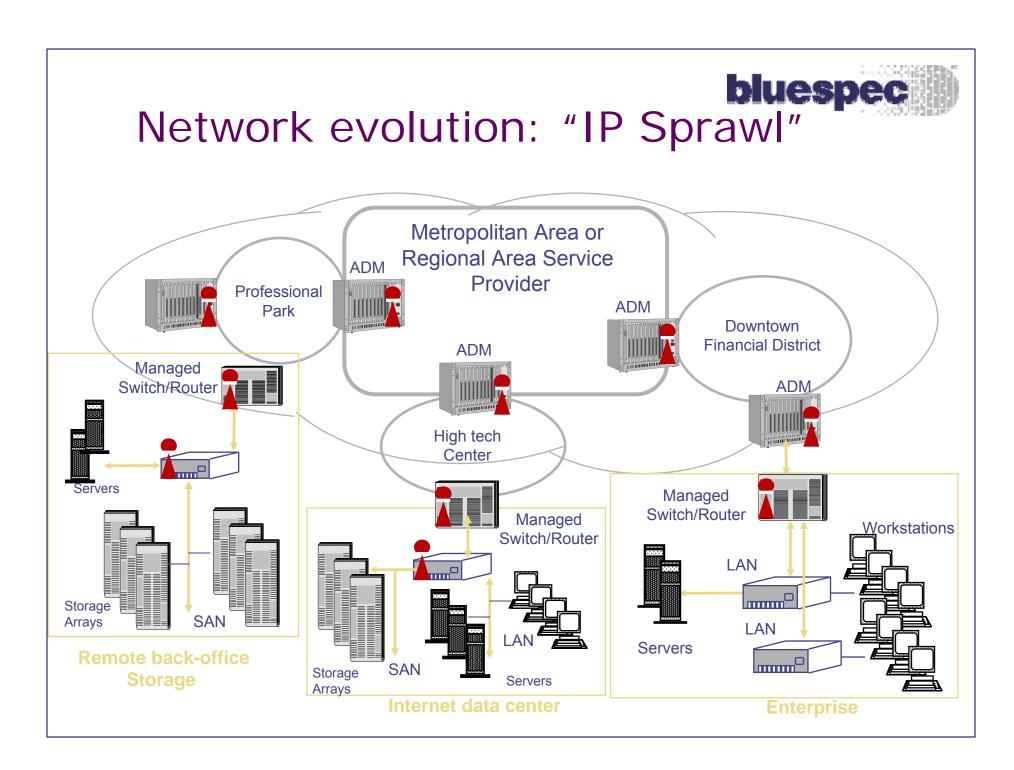

Delivering <u>Efficient</u> switch fabrics and building blocks for <u>10G IP</u> differentiated services...

... lower cost

... higher port density

...less power

# ...by rewriting the rules for semiconductor development

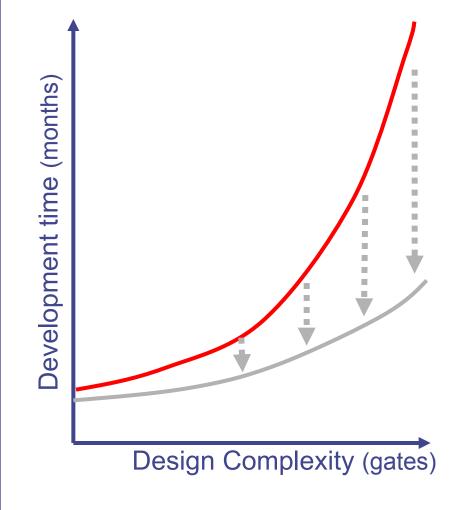

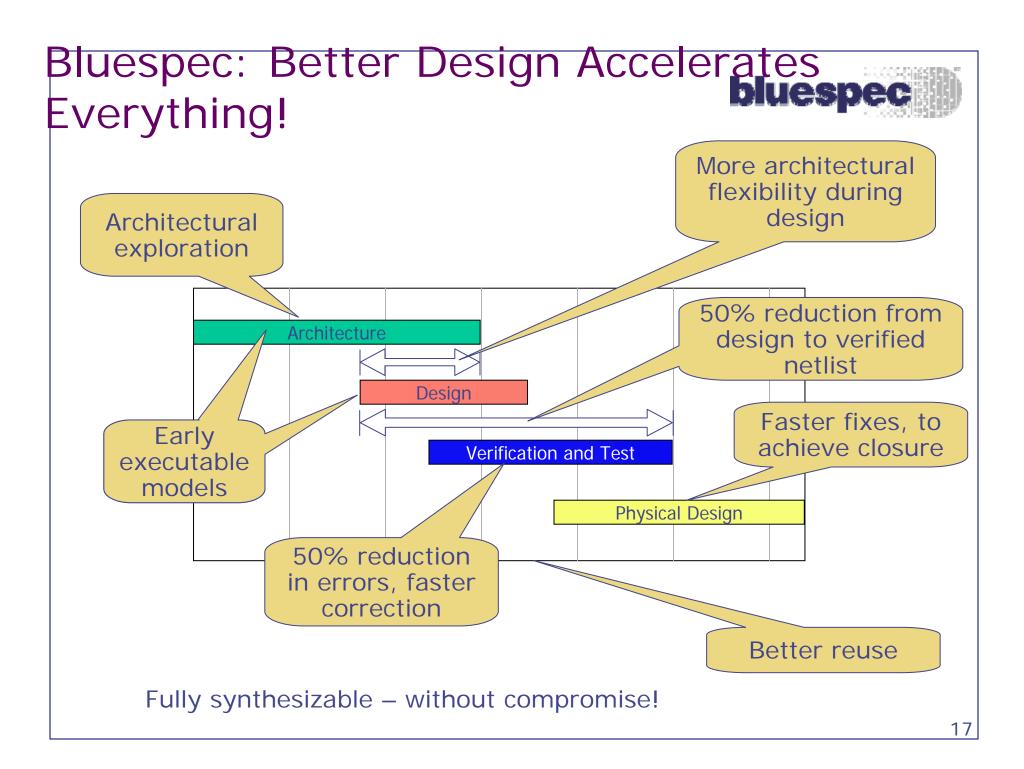

Sandburst's revolutionary BlueSpec<sup>TM</sup> technology reduces ASIC development time by up to 50%!

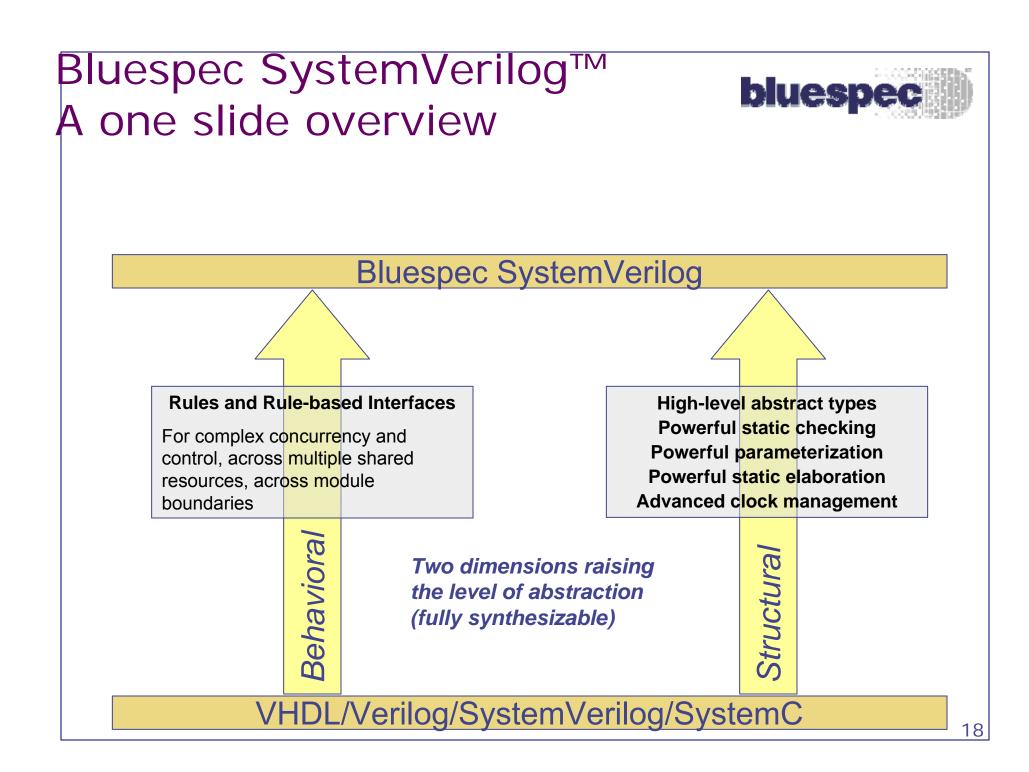

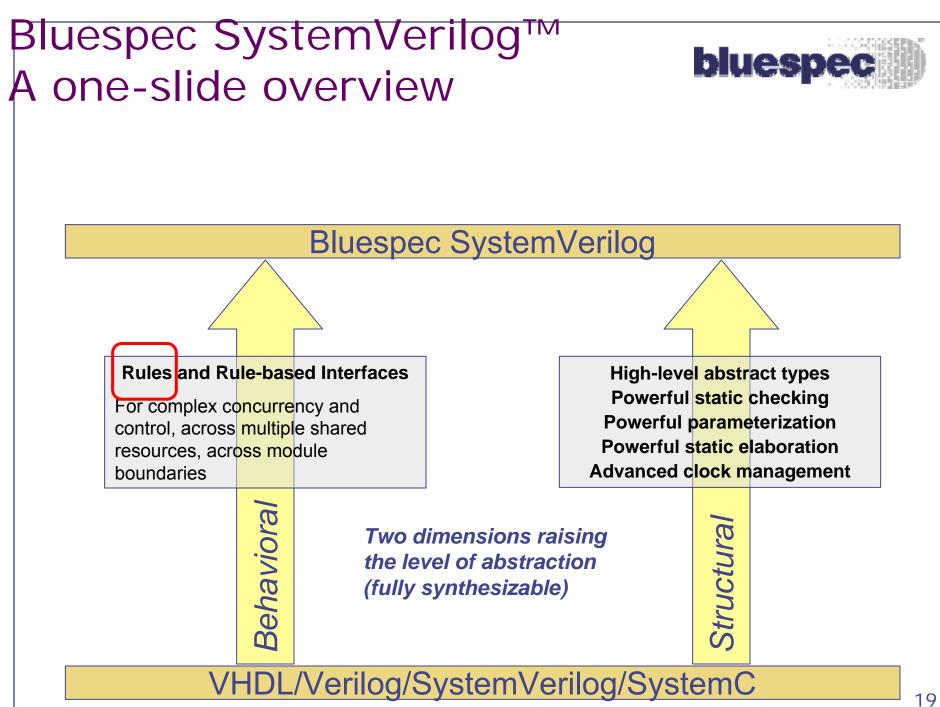

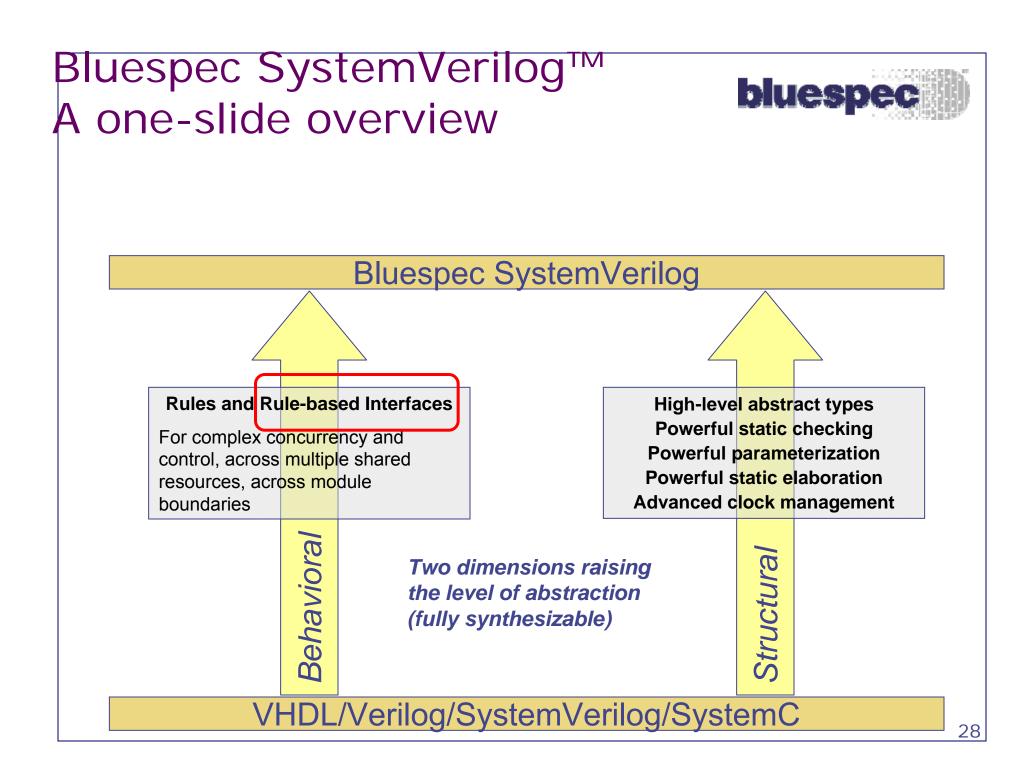

### What is BlueSpec

- A language for hardware description

- Based on TRS (term rewriting systems)

- Syntax and type system based on Haskell

- Run-time execution model quite unlike Haskell's

- Compiled to structural Verilog

- . . . or C

- . . . or FPGAs.

## Bluespec at Sandburst

- Lennart Augustsson designed the Bluespec language

- Notation, type system, and static abstraction mechanisms borrow heavily from Haskell

### Designed and implemented the compiler

- v1 circa 7/2000, v2 circa 9/2000, v3 11/2001

- Mieszko Lis implemented the scheduler

- Initially produced just Verilog

- Process/execute with std. Verilog tools

- Later (10/2000) also produced C

- C code is "cycle accurate" to the Verilog

- Can mix Bluespec-generated code with other code (hand-written Verilog, legacy Verilog, imported IP, ...)

### The Bluespec team

- Rishiyur Nikhil, Director (DEC/Compaq Research, MIT)

- Lennart Augustsson (CRT, Chalmers)

- Stephen Bailey (DEC, startups)

- Joe Stoy (Oxford)

- Mieszko Lis (MIT)

- Jacob Schwartz (MIT)

- Dan Rosenband (MIT)

### plus Arvind

- Consultants

- Professor James Hoe (CMU)

- Professor Krste Asanovic (MIT)

- Professor Srini Devadas (MIT)

- Niklas Rojemo (Sweden)

## BlueSpec<sup>TM</sup> Advantage:

### Bluespec use at Sandburst

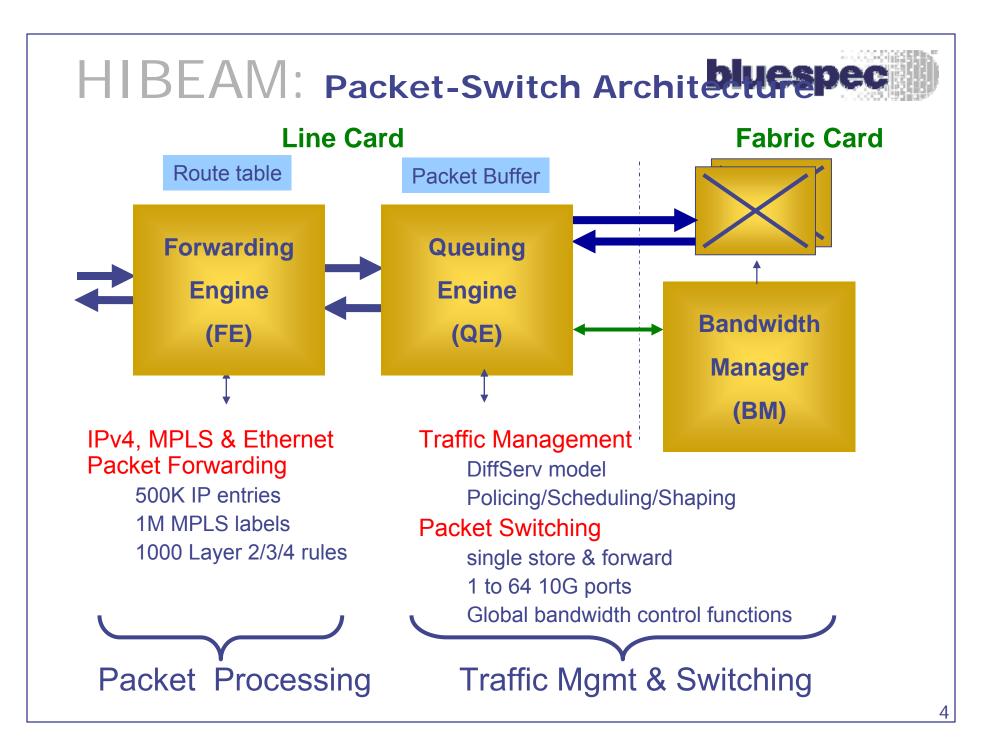

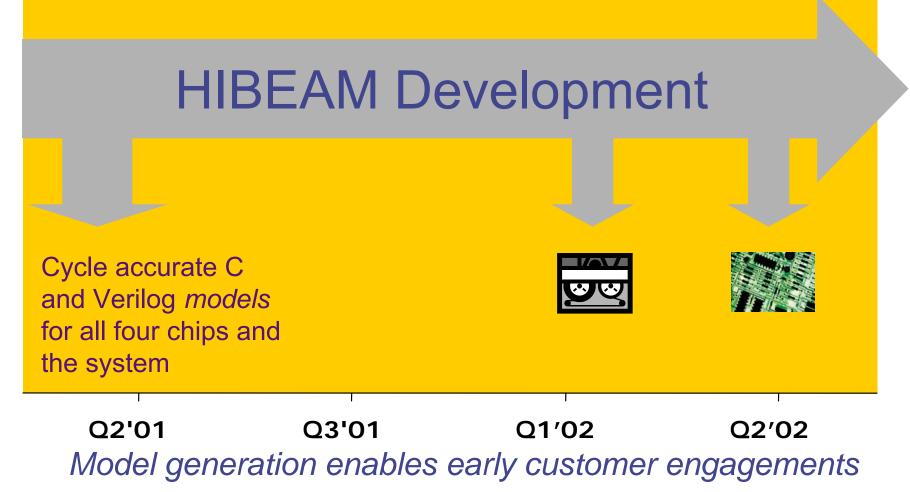

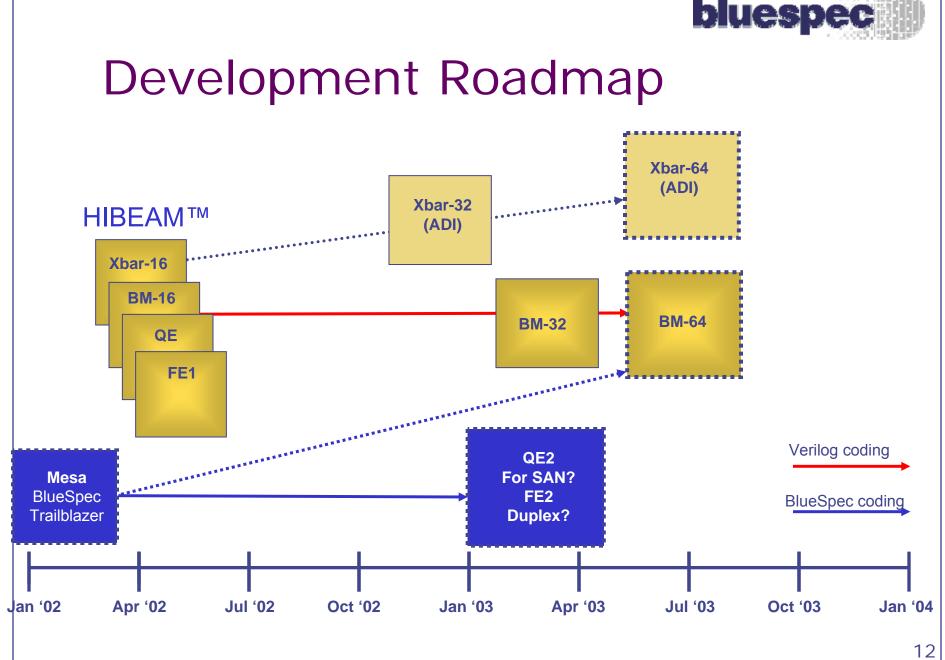

- HIBEAM chip set system model for performance analysis

- close to 15K lines of Bluespec

- April 2001 through the present

- Mesa "pathfinding" project

- Goal: flesh out the Bluespec "design flow"

- Understand how Bluespec design fits into the larger picture of the full ASIC design process

- 6/2001 through 11/2001

#### cing? New Home?

nik K. Shah 8184 656 x8184 43 (Cell) ortgage.com

ly among the Top Mortgage .We close loans faster because ing, underwriting, approval, and

#### rates!!

ible rates for your situation!!

· Portfolio Loans with as Little as 5% Down

- A Credit Programs

- Second Mortgage Programs

- Multi-Family Financing (Owner

- Occupied or Investor)

- · Land Loans

- · Bridge Loans

- No Income Verification Loans

Arvind

Tasker

MB0050 New Hampshire Broker # 72207MB epse # 20001147LL Florida License # 248255 a based upon FICO score and Loan to Value

#### JRANCE HE SAME THINK AGAIN.

#### THER BE WITH AN O PROVIDES EXPERTISE NCE COMPANIES?

ou can expect the following:

and excellent service panies with strong paralleled claim services ndividual needs at

ur schedule, there is only one

#### BUSINESS

### **Bluespec has designs** on saving billions for semiconductor industry

#### New company launches with \$4 million in funding

#### By MARK PICKERING INDIA New England Staff

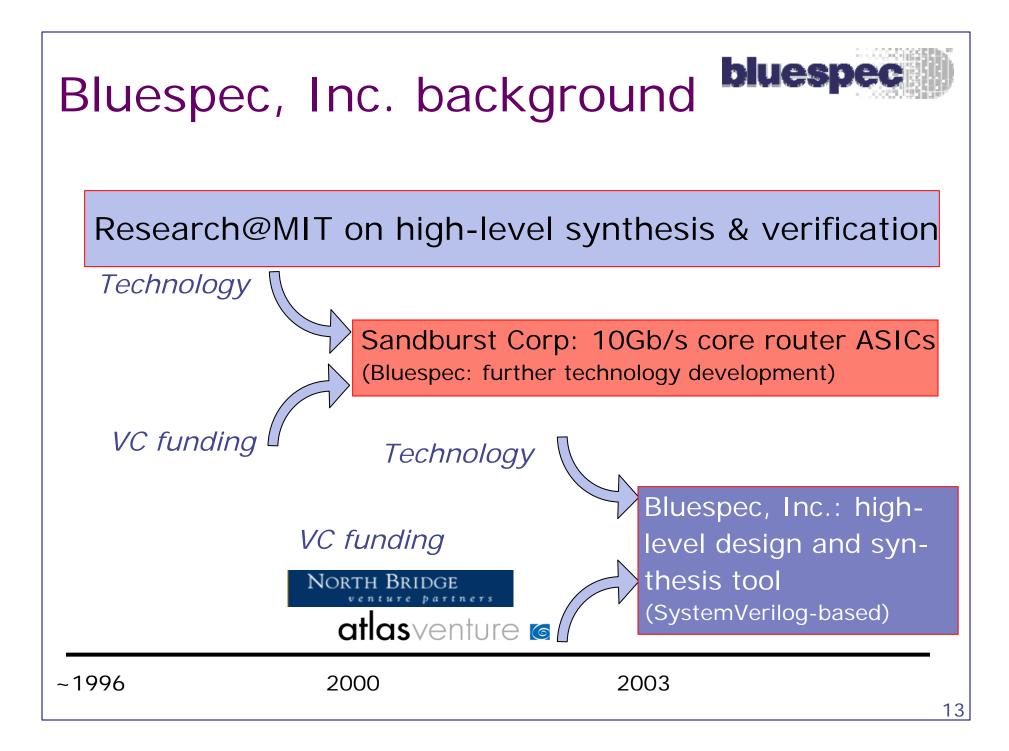

WALTHAM, Mass. - Two local entrepreneurial luminaries have co-founded a new startup, Bluespec, whose software is being used to speed up the microchip-

setts Institute of Technology professor, is best known for founding Andover-based Sandburst Corp., a semiconductor

company backed by \$36 million in venture capital.

"Arvind's research has come up with a key breakthrough" in how chips are designed, said Shiv Tasker, Bluespec co-founder and chief executive officer. Tasker has more than 15 years of experience

in the chip-design industry and, most recently, was CEO of Walthambased PhaseForward, a health-related software

company. Working together on Bluespec, the two have landed \$4 million in venture capital from Atlas Venture and Walthambased North Bridge Venture Partners

There is a major opportunity for companies such as Bluespec "to save the semiconductor

industry billions of dollars," said Rita Glover, principal analyst at EDA Today, which covers Arvind said. electronic-design automation.

Bluespec has 14 full-time employees, mostly in engineering, said Tasker. Now, efforts are moving beyond the research phase. "The technology is very robust," said Tasker.

not a good fit for Sandburst, a chip company.

"You don't want to confuse investors," he said

decision being made, he said. Sandburst, where Mutual friends then introduced Arvind and

Tasker.

what it would take to build something as a commercial product and to identify whether the capitalists."

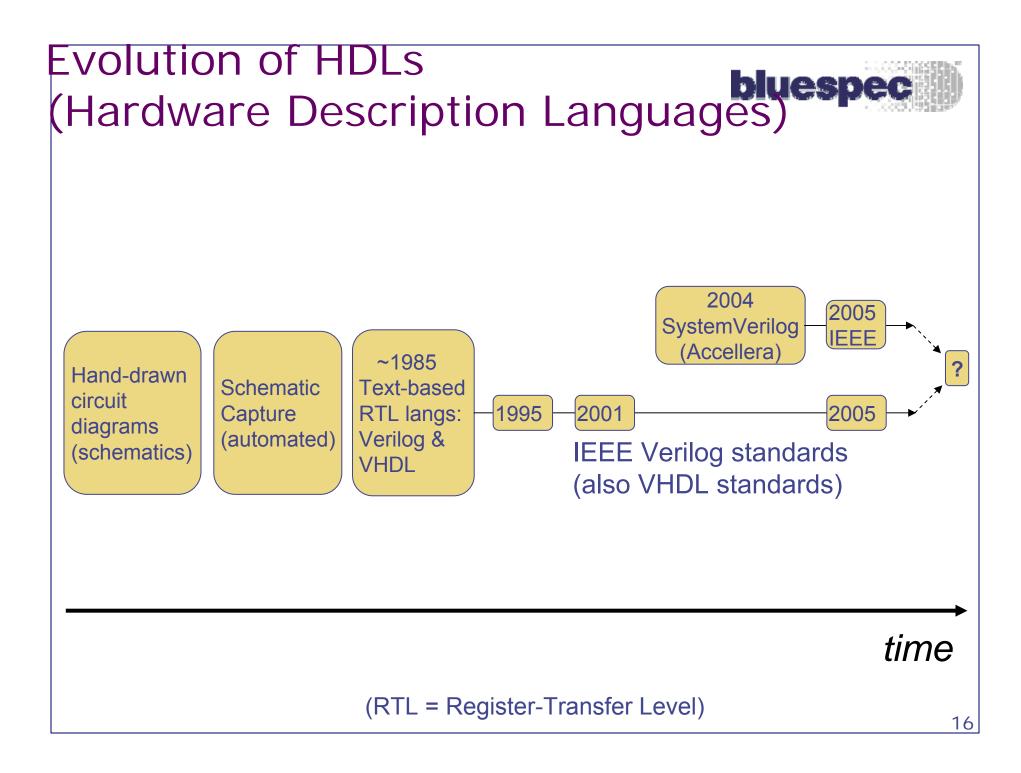

ingly difficult to design chips, because of the

Sandburst's CEO, Arvind said it suits him fine. "My leave was for two years from MIT,"

Asked if he thought of being a CEO lege professor."

The process of starting Bluespec actually began last January, said Arvind, who goes by just the one name. At that point, Arvind had stepped down from his CEO role at Sandburst and was back teaching computer science at MIT

Meanwhile, he had begun to see real potential in research he had been doing first at MIT and then at Sandburst, which owned all the related intellectual property, he said. Ultimately, the company's board decided the software being developed now by Bluespec was

Having separate businesses, Arvind said, also seemed a better strategy for appealing to venture capitalists.

Arvind stepped aside from voting on that matter, given that he could benefit from the Arvind remains a board member, now has a minority stake in Bluespec.

"The technology looked intriguing, so I wrote

a business plan," said Tasker. "We had to assess market size was large enough to interest venture

In fact, Tasker said, "the market is clamoring for solutions to design problems." It is increasdrive to put more and more complex electronics

manufacture chips has vastly outstripped the speed at which they are designed."

Working with the venture capitalists, Tasker and Arvind formed the company in June and gained funding in July. Asked about his return to teaching after being

As for Bluespec, Arvind said, "I'm there one day a week, but there in spirit even more." there, Arvind insists genially: "I'm a col-

### The Bluespec team

- Rishiyur Nikhil, Director (DEC/Compaq Research, MIT)

- Lennart Augustsson (CRT, Chalmers)

- Stephen Bailey (DEC, startups)

- Joe Stoy (Oxford)

- Mieszko Lis (MIT)

- Jacob Schwartz (MIT)

- Dan Rosenband (MIT)

### plus Arvind

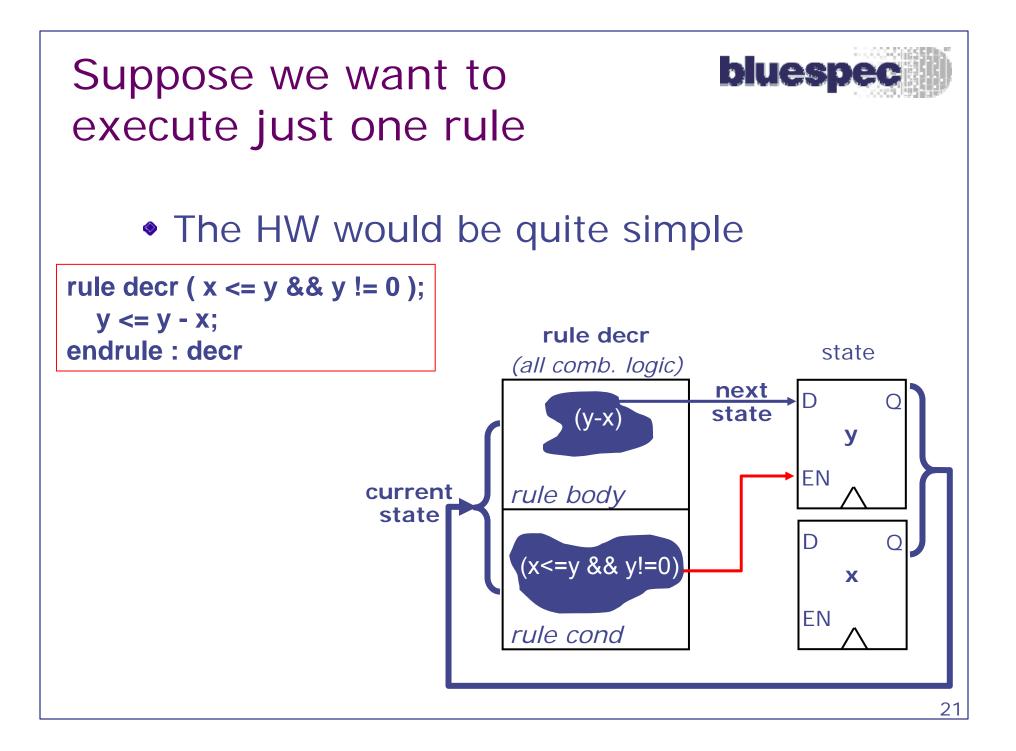

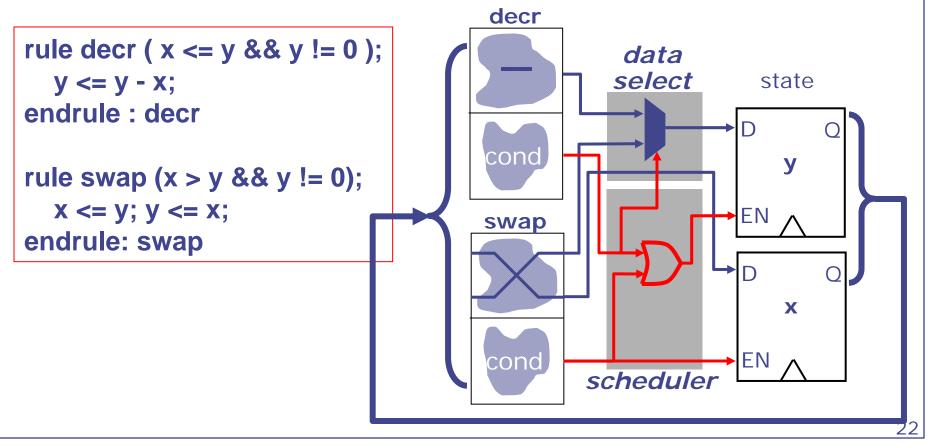

# One-at-a-time intuitions

- Untimed rule semantics are one-rule-at-a-time steps

- The Bluespec compiler schedules multiple rule steps into each clock, producing a timed semantics and resolving non-determinism

- But before we go there, let's build some HW intuitions based on one-rule-at-a-time

- We'll use the following example

- (Can you guess what it computes? Hint: "Euclid")

```

rule decr ( x <= y && y != 0 );

y <= y - x;

endrule : decr

rule swap (x > y && y != 0);

x <= y; y <= x;

endrule: swap

```

Answer: Euclid's algorithm for computing GCD (Greatest Common Divisor) of initial values in x and y registers; result is in x

### Two mutually exclusive rules

(Later: what to do if they're not mutually exclusive)

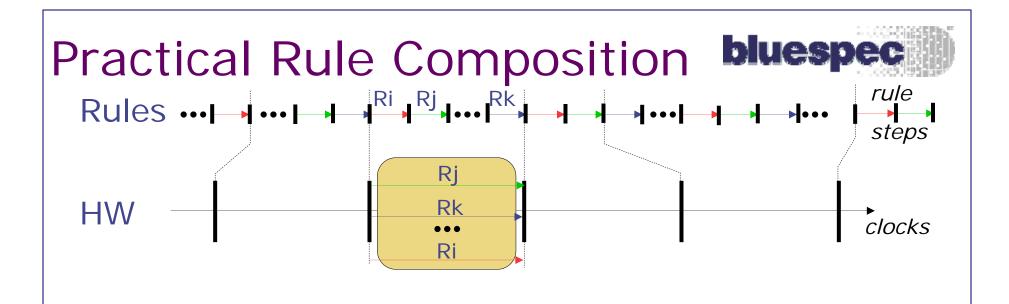

- Practical rule composition

In practice, we only do restricted rule compositions

- Every rule executes entirely within one cycle

- A rule fires at most once in a cycle (no Rule1<Rule1)

- Greedy: as many rules as possible per clock cycle

- Rule1 body does not feed into Rule2 cond

- Therefore, rule conds can be evaluated based on state at beginning of cycle

- Rule1 body does not feed into Rule2 body

- Therefore, Rule2 can use state from beginning of cycle

- No intra-cycle communication between rules, in the HW

- Correctness: HW scheduler only allows rules Ri, Rj, ..., Rk to execute concurrently when *net state change* is equivalent to Ri<Rj<...<Rk</li>

- Thus, never get into inconsistent state (no race conditions)

- Every state in the HW exists in the one-rule-at-a-time semantics

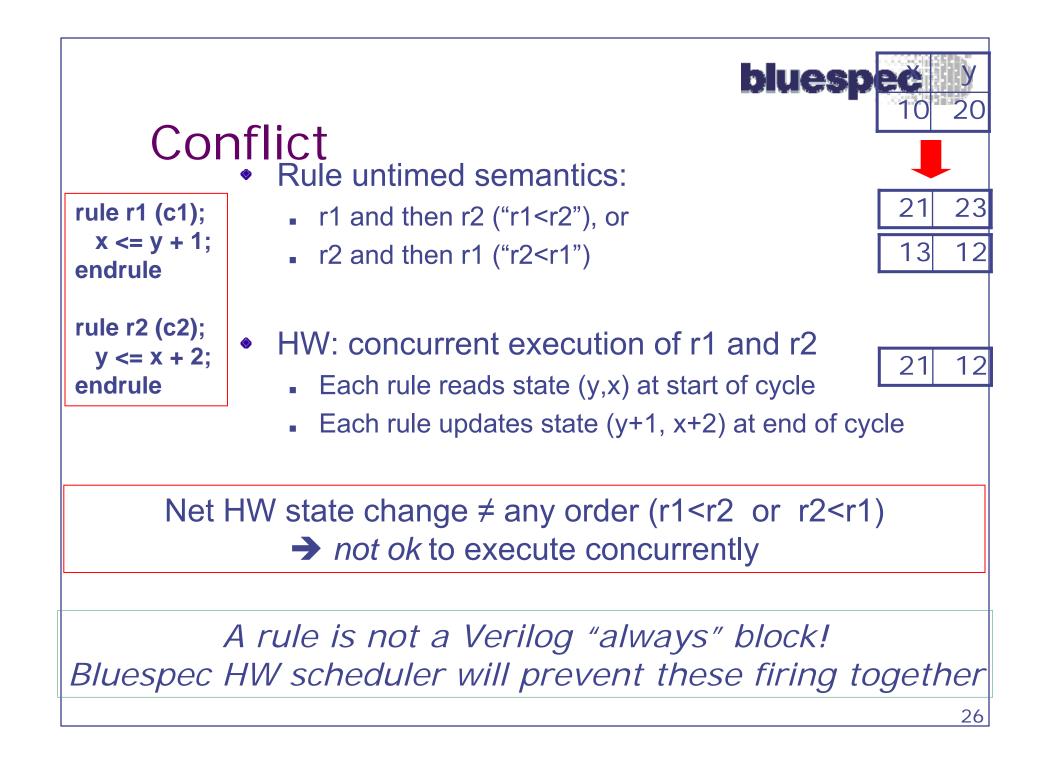

### Multiple Rules and Conflicts

- If two rules are enabled in a particular cycle, what prevents them from executing concurrently?

- Answer: conflicts

- Since state read/write ordering is different in rule-at-a-time semantics compared to concurrent execution, certain concurrent executions would result in inconsistent states

- Certain *resource sharings* prevent concurrency

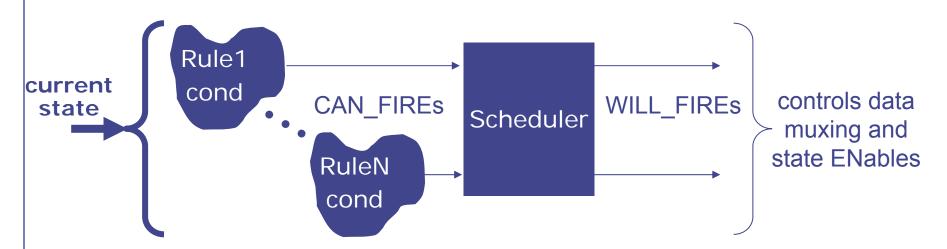

## CAN\_FIRE and WILL\_FIRE

Scheduler incorporates conflict analysis by compiler

- CAN\_FIRE is False → WILL\_FIRE is False

- CAN\_FIRE is True → WILL\_FIRE is

- True if not precluded by conflicts with other rules

- False otherwise (the rule is blocked for this cycle)

### Multiplier Example

module mkTest ();

```

Reg#(int) state <- mkReg(0);

Mult_ifc m <- mkMult1();

```

```

rule go (state == 0);

m.start (9, 5);

state <= 1;

endrule

```

```

rule finish (state == 1);

$display ("Product = %d",m.result());

state <= 2;

endrule

```

endmodule: mkTest

interface Mult\_ifc; method Action start (Tin x, Tin y); method Tout result (); endinterface: Mult\_ifc

module mkMult1 (Mult\_ifc); Reg#(Tout) product <- mkReg(0); Reg#(Tout) d <- mkReg(0); Reg#(Tin) r <- mkReg(0);</pre>

```

rule cycle (r != 0);

if (r[0] == 1) product <= product + d;

d <= d << 1;

r <= r >> 1;

endrule

```

```

method Action start (x,y) if (r == 0);

d <= x; r <= y; product <= 0;

endmethod

```

```

method result () if (r == 0);

return product;

endmethod

```

```

endmodule: mkMult1

```

### Multiplier Example

mkTest :: Module Empty mkTest = module state :: Reg int state <- mkReg 0

```

m :: Mult_ifc

m <- mkMult1

```

```

rules

```

```

"go" : when state == 0 ==>

m.start (9, 5)

state := 1

```

```

"finish" : when state == 1 ==>

$display ("Product = %d",m.result())

state := 2

```

interface Mult\_ifc =

start :: Tin ->Tin -> Action

result :: Tout

```

mkMult1 :: Module Mult_ifc

mkMult1 =

module

product :: Reg Tout

product <- mkReg 0

d :: Reg Tout

d <- mkReg 0

r :: Reg Tin

r <- mkReg 0

rules

"cycle": when r /= 0 ==>

if r[0] == 1

product := product + d

d := d << 1

r := r >> 1

interface

start x y = action { d:=x; r:=y; }

when r == 0

result = product

when r == 0

```

31

### Multiplier Example

```

ESL_MODULE (mkTest, ESL_EMPTY) {

esl_reg<int> state;

Mult_ifc * m;

ESL_RULE (go, state == 0) {

m->start (9, 5);

state = 1;

}

ESL_RULE (finish, state == 1) {

cout << "Product = " << m->result()

<< endl;

state = 2;

</pre>

```

ESL\_INTERFACE ( Mult\_ifc ) { ESL\_ACTION\_METHOD\_INTERFACE (start, Tin x,Tin y); ESL\_VALUE\_METHOD\_INTERFACE (result, Tout);

```

ESL_CTOR (mkTest) {

ESL_NEW_REG(state, int, 0);

m = new mkMult1();

ESL_END_CTOR;

}

```

### Concern: the "learning curve"

- Hardware designers:

- "Atomic" means (if anything) "in the same clock cycle"

- Bluespec:

- Many atomic actions in same cycle, as if they happened one at a time

### Concern: the "learning curve"

- Hardware designers:

- Begin by designing the overall finite state machine to control the design

- Bluespec:

- Design little rules locally: the compiler will generate the overall logic

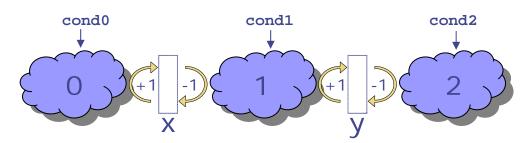

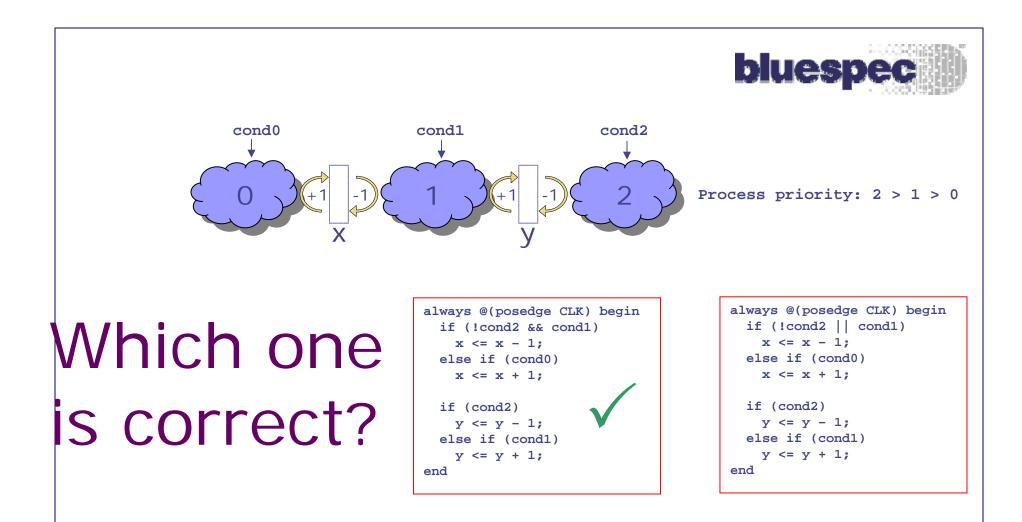

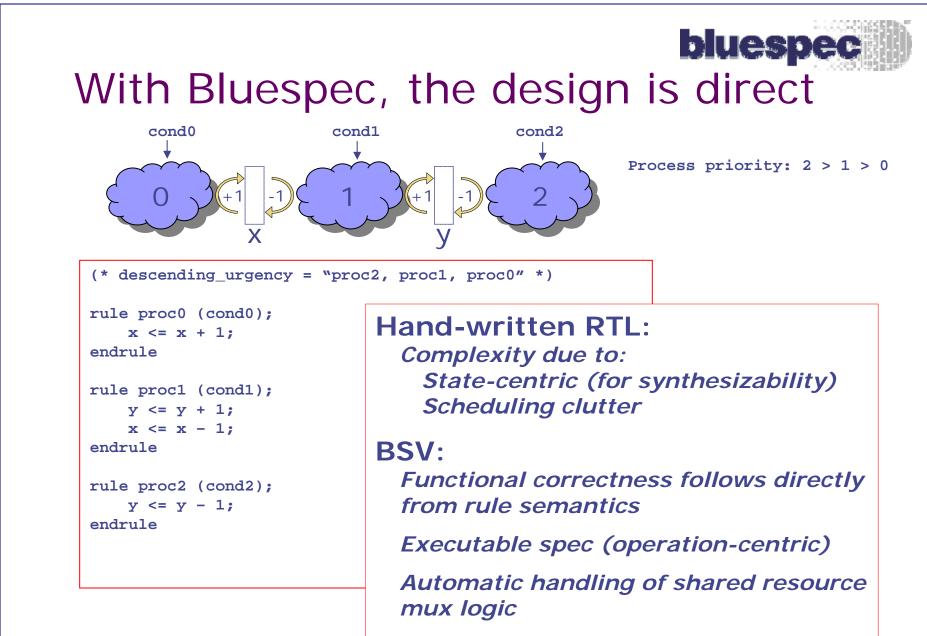

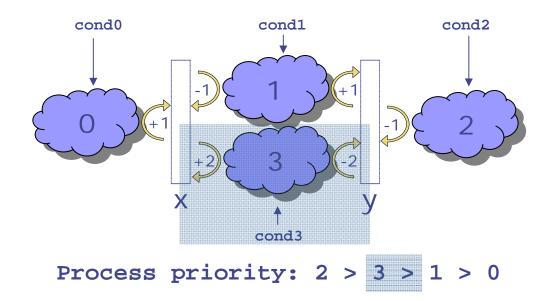

# Simple example with concurrency and shared resources

Process priority: 2 > 1 > 0

- Process 0: increments register x when cond0

- Process 1: transfers a unit from register *x* to register *y* when *cond1*

- Process 2: decrements register y when cond2

- Each register can only be updated by one process on each clock. Priority: 2 > 1 > 0

- Just like real applications, e.g.:

- Packet arrives, is processed, departs

What's required to verify that they're correct? What if the priorities changed: cond1 > cond2 > cond0? What if the processes are in different modules?

Same hardware as the RTL

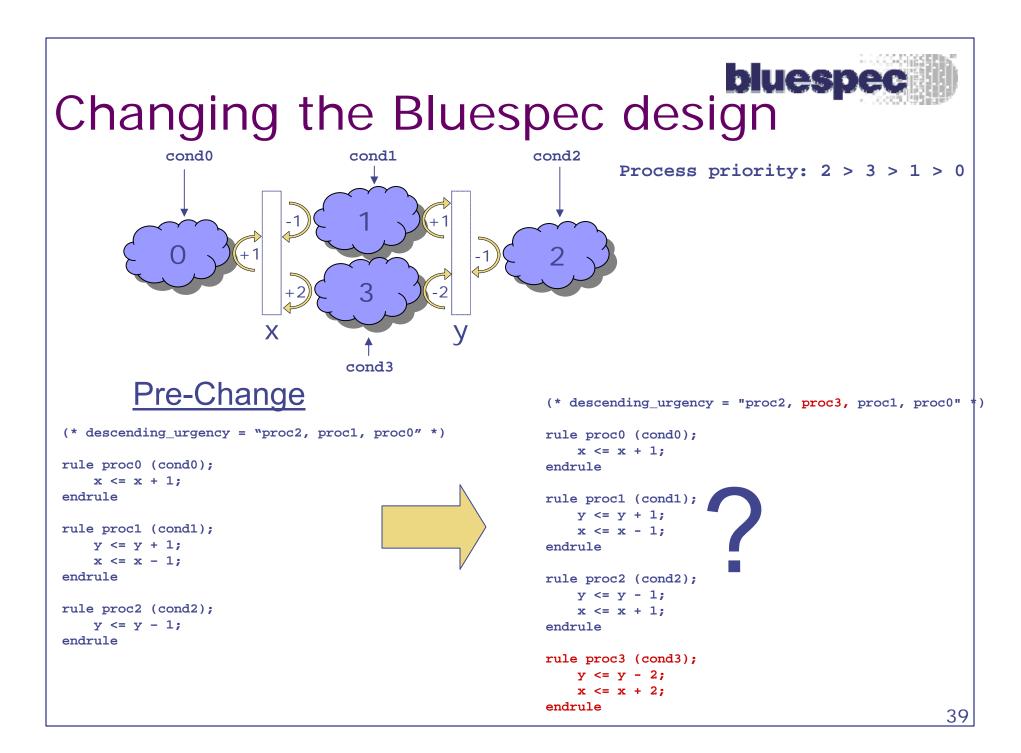

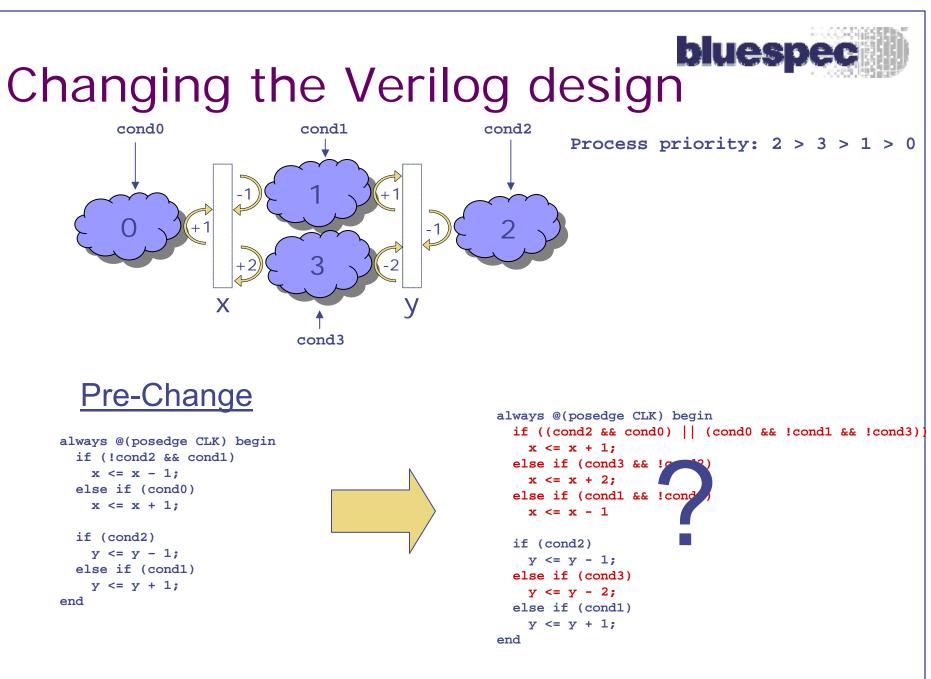

# Now, let's make a small change: add a new process and insert its priority

#### Concern: the "learning curve"

- Other ways to make customers immediately productive

- Offer generic IP they can use "off the shelf" with very little training

- They can customize

- But then they'll have to learn more, to do so

So how does Arvind fit into this?

- Board member

- Provides longer-term view of the technical development

bluespec

```

module mkFifo(Fifo#(t))

provisos(Bits#(t,ts));

Reg#(t) dta <- mkRegU;

Reg#(Bool) full <- mkReg(False);</pre>

```

```

method push(t x) if (!full);

full <= True; dta <= x;

endmethod</pre>

```

method t pop() if (full);

full <= False; return dta;

endmethod

endmodule</pre>

- Immediate solution (Bluespec)

- Invent "wires"

- Wires similar to registers, but:

- Registers:

- Read "early" in clock cycle, written at end

- Wires:

- · Written first, read later

- Value goes away at end of cycle

- Immediate solution (Bluespec)

- New primitive: no great upheaval to language

- Methods set wires; an internal rule makes the appropriate state change

- Allows the "problem" to be overcome by enhancing the FIFO's design

- Immediate solution (Bluespec)

- But:

- Separating method from state change breaks atomicity – needs care to get internal behavior right

- Leads users into bad practices, and spaghetti-like designs

- Longer-term solution (Arvind)

- Extend language: allow designers to specify scheduling requirements

- Performance Guarantees

- "Allow pop before push in same cycle"

- Compiler generates necessary hardware

- Cleaner; more robust

- Need more intuition about what the compiler will do

#### A Final Concern

#### • Has Arvind's fame spread far and wide?

c:\users\stoy>finger arvind@mit.edu [mit.edu]

Student data loaded as of May 17, Staff data loaded as of May 17. Notify Personnel or use WebSIS as appropriate to change your information.

Our on-line help system describes

How to change data, how the directory works, where to get more info. For a listing of help topics, enter finger help@mit.edu. Try finger help\_about@mit.edu to read about how the directory works. Directory bluepages may be found at http://mit.edu/communications/bp.

There were 3 matches to your request.

Complete information will be shown only when one individual matches your query. Resubmit your query with more information. For example, use both firstname and lastname or use the alias field.

name: Arvind, Amarnath department: System Design And Management year: G alias: A-arvind

name: Jairam, Arvind department: Lincoln Laboratory title: LL - Associate Staff alias: A-jairam

name: Arvind department: Dept of Electrical Engineering & Computer Science title: Charles W & Jennifer C Johnson Professor in CS Eng alias: arvind

c:\users\stoy>

c:\users\stoy>finger arvind@mit.edu [mit.edu]

2

Student data loaded as of May 17, Staff data loaded as of May 17. Notify Personnel or use WebSIS as appropriate to change your information.

Our on-line help system describes

How to change data, how the directory works, where to get more info. For a listing of help topics, enter finger help@mit.edu. Try finger help\_about@mit.edu to read about how the directory works. Directory bluepages may be found at http://mit.edu/communications/bp.

There were 3 matches to your request.

Complete information will be shown only when one individual matches your query. Resubmit your query with more information. For example, use both firstname and lastname or use the alias field.

name: Arvind, Amarnath department: System Design And Management year: G alias: A-arvind

name: Jairam, Arvind department: Lincoln Laboratory title: LL - Associate Staff alias: A-jairam

name: Arvind department: Dept of Electrical Engineering & Computer Science title: Charles W & Jennifer C Johnson Professor in CS Eng alias: arvind

c:\users\stoy>

#### Conclusion:

## Arvind is recursively impossible.