## Bluespec-8 Advanced Topics

Rishiyur S. Nikhil nikhil@sandburst.com Thursday, January 16, 2003

MIT IAP Course http://www.csg.lcs.mit.edu/IAPBlue

# **Topics**

- Connectables

- Structured connections between modules

- Control/status registers

- "Back door" entry into a chip

- Multiple clock domains

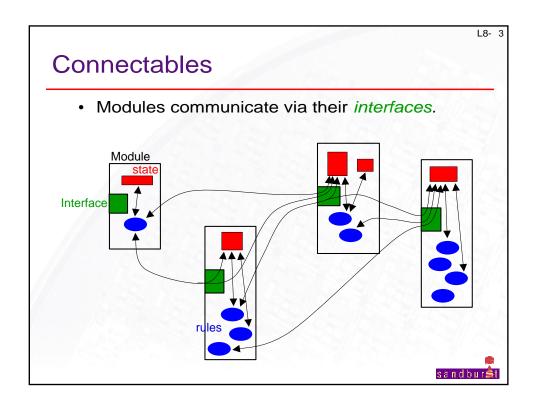

## Connectables

- In certain situations, there are practical considerations on what can go into an interface

- Verilog boundary: Bluespec interface must have a translation into a Verilog interface (wires)

- Timing analysis and timing closure:

- Interface input and output wires must be registered immediately at the module boundary

- Interface protocol should be "pipelinable", allowing free insertion of pipeline registers in long wires

- Readability and maintainability:

- · "standard" interfaces

- standard "adapters" between similar standard interfaces

- "Connectables" are a class of interfaces motivated by such considerations

- (there can be more such classes)

## Class Connectable

Indicates that two related types can be "connected". Does not specify the nature of the connection.

```

class Connectable a b

(<->) :: a -> b -> Module Empty

```

Example use (for connectable types A and B):

## Class Connectable

The simplest types in the Connectable class are Get and Put

L8- 8

## Class Connectable

FIFO interfaces can be converted into Get and Put (and therefore become connectable)

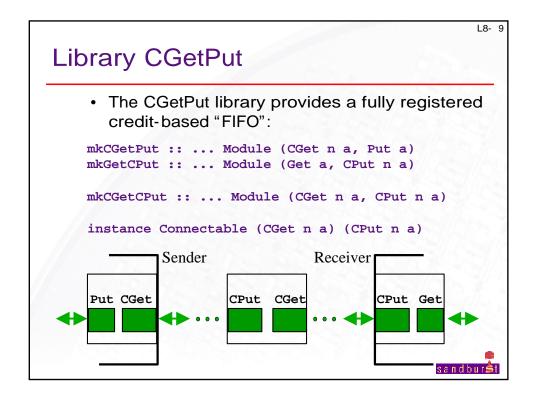

## Library CGetPut

- The intermediate buffers (mkCGetPut) are optional:

- Insert them to add buffering along long wires

- They add latency

- The latency of the transfer is r, in the absence of any intermediate buffers

- -r = 4 in our implementation

- The "credit" value is n.

- Choose n = 4 for full bandwidth

- Choose n = 1 for minimum registers (but  $\frac{1}{4}$  bandwidth)

## Library BGetPut

The BGetPut library provides a fully registered connection that makes no assumptions about setup and hold times, and so can connect different clock domains

```

mkBGetPut :: ... Module (BGet a, Put a)

mkGetBPut :: ... Module (Get a, BPut a)

instance Connectable (BGet a) (BPut a)

(but it's not fast)

```

L8-12

## Multiple connections

Two pairs of (corresponding) connectable types are themselves connectable:

(see also ClientServer library, and CGetPut and BGetPut versions of ClientServer)

8- 13

# Multiple connections

• Two lists of (corresponding) connectable types are themselves connectable:

"Control and Status" Registers

Control/Status registers

• Many chips have "control and status registers" for configuration, diagnostics, statistics, debugging, etc.

• These registers are read/written from a special "register access" port into the chip, such as a PCI bus

packets in packets out

Control/Status Registers (CSRs)

- CSRs have "two faces":

- "Chip side": the ordinary register interface

- "Local bus side": read/write like a memory location

- · Each CSR has its own address

- CSRs may be scattered all over the design

- The "plumbing" for local bus side of CSRs can be quite messy if done explicitly

- Bluespec has mechanisms that hide/ simplify/ automate the local bus side

- Part of the power of monads/modules-- not built into the language!

L8-16

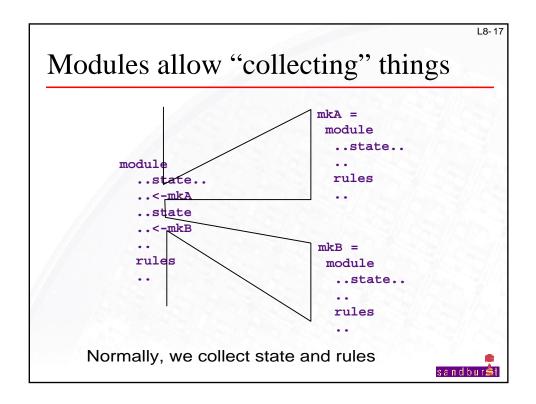

# In general, modules can collect other things (lib ModuleCollect) • Collect items of type a and return a value of type i (usually an interface): data ModuleCollect a i • Add an item to a collection addToCollection :: a -> ModuleCollect a i • Retrieve the collection and the regular value getCollection :: ModuleCollect a i -> Module (i, List a)

8- 19

## Library ModuleCollect

- A module expression, in general, has type

- Module t is just a special case, where the only things being collected are state and rules.

- Instead, we can treat the whole module structure as a ModuleCollect structure and, at the top, extract the collected objects and restore it back to a Module type.

10 20

# Library LocalBus

We use ModuleCollect to automatically gather up all the "local bus side" interfaces of Control/ Status Registers

# Library LocalBus

In a module, for a CSR, we simply use lbRegRW instead of mkReg

```

module

...

r :: Reg (Bit 32) <- mkReg 15

csr :: Reg (Bit 32) <- lbRegRW 0x100 15

```

- 0x100 is the localbus address of the CSR

- The module's type is something like:

```

ModuleCollect (LBSReg 24 32) t

```

instead of:

Module t

### L8-22

# Library LocalBus

- Simplifying local bus address management:

- Add a base address to all the LBSRegs in a module

.8- 23

## Library LocalBus

Collecting and converting into a memorylike interface

(and there are further facilities to collect multiple such RAM interfaces into a single RAM interface)

L8-24

# Library LocalBus: summary

- Wherever you want a CSR, use a constructor like lbRegRW instead of mkReg

- Give it a local bus address (can be a computed value, argument to module constructor function)

- When instantiating sub-modules, use lbsOffset to move the CSRs of each submodule to a relatively unique local bus address region

- At the top-level, use lbsCollect to obtain the original interface to the module, and a RAM interface to all its CSRs.

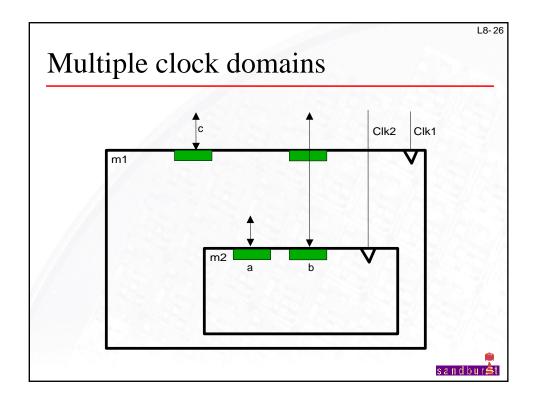

# Library ClockConv

A type for clocks

data Clock

- The type is abstract: you can essentially only pass it in as a value from the outside.

- Externally represented as 2 wires, a clock and a reset.

- A class of types that are allowed to cross a clock domain boundary:

classClockConv a

Two useful types in this class:

```

instance ClockConv (Get a)

instance ClockConv (Put a)

```

Any type can be "closed", making it a ClockConv type

```

instance ClockConv (Closed a)

close :: a -> Closed a

```

L8-28

# Library ClockConv

Convert a module to be clocked by a given clock instead of the default clock:

```

Example

mkM2 :: Module (A, Closed B)

module

...

return (ia, close ib)

mkM1 clk2 =

module

...

(m2a,m2b) <- clockConv clk2 mkM2

...

return (ic, m2b)

```