## Bluespec IA-64 Modeling

Roland Wunderlich and James C. Hoe Computer Architecture Lab (CALCM) Carnegie Mellon University

## Why Bluespec?

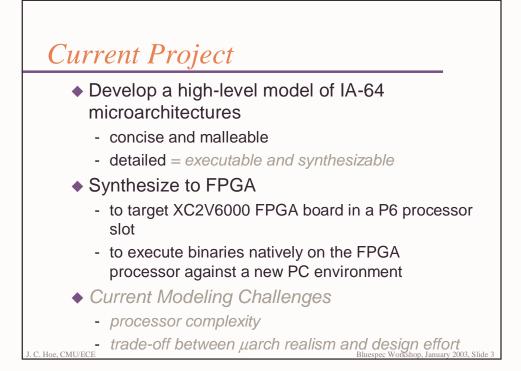

Detailed

- nothing left to interpretation

- litmus test: can it be executed or synthesized automatically?

Concise

- compact and expressive

- natural correspondence to HW structures and abstractions

- Maintainable

- easy to understand

- modular: composible and decomposible

J. C. Hoe, CMU/ECE

espec Workshop, January 2003, Slide

## Synthesis Results

## ◆ Synplify and Xilinx ISE for a XC2V6000 –6

- LUTs: 43,408 of 74,900 (58%)

- Critical path: 23.450 ms (42.6 MHz)

- Cost breakdown (synthesized in pieces)

|             |                                           | LUT<br>(max 38,400) | Critical Path<br>(ns) | Freq.<br>(MHz) |  |

|-------------|-------------------------------------------|---------------------|-----------------------|----------------|--|

|             | Fetch                                     | 6%                  | 14.8                  | 67.3           |  |

|             | Decode                                    | 8%                  | 23.0                  | 43.5           |  |

|             | Dispersal+<br>Rn+Rd                       | 24%                 | 17.2                  | 58.1           |  |

|             | Execute                                   | 11%                 | 19.5                  | 51.4           |  |

| C) II UE CE | DELECT DELECTION We delet a Laure 2002 CP |                     |                       |                |  |