#### Bluespec at MIT

Arvind (arvind@mit.edu) Computer Science & Artificial Intelligence Lab. Massachusetts Institute of Technology

The First Bluespec Workshop, MIT, Cambridge, MA August 13, 2007

August 13, 2007

http://csg.csail.mit.edu/arvind/

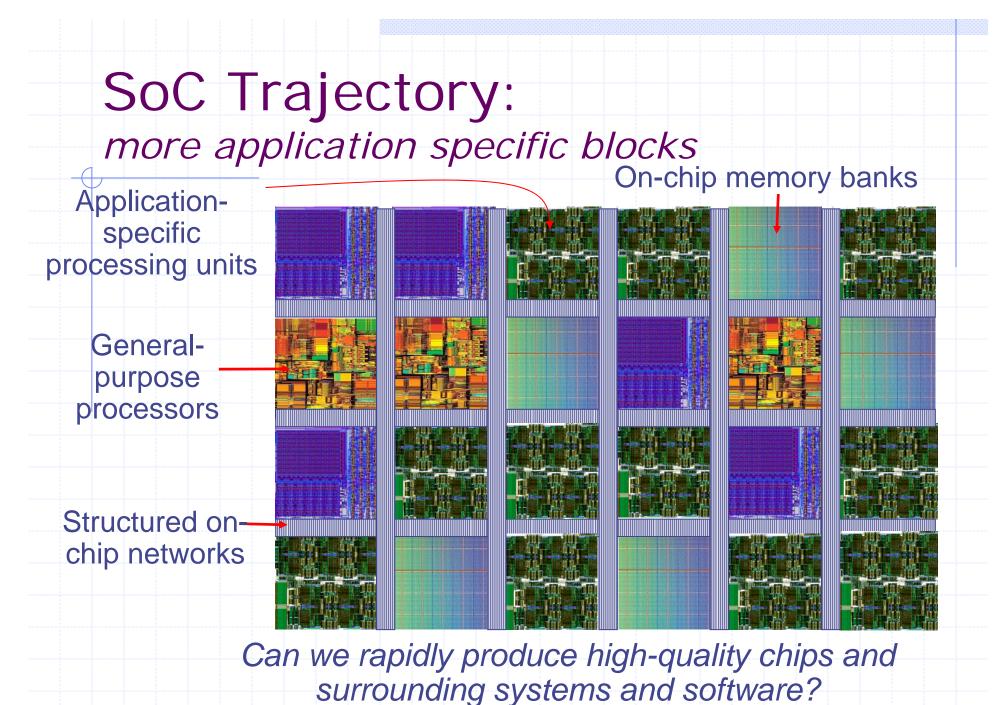

Real power saving implies specialized hardware

- H.264 implementations in software vs hardware

- the power/energy savings could be 100 to 1000 fold

but our mind set is that hardware

design is

Difficult, risky

Increased time-to-main

Inflexible, brittle, er

How to deal with changing standards, errors

August 13, 2007

http://csg.csail.mit.edu/arvind/

http://csq.csail.mit.edu/arvind/

August 13, 2007

## Making hardware design

#### easier

August 13, 2007

#### **Recent Applications**

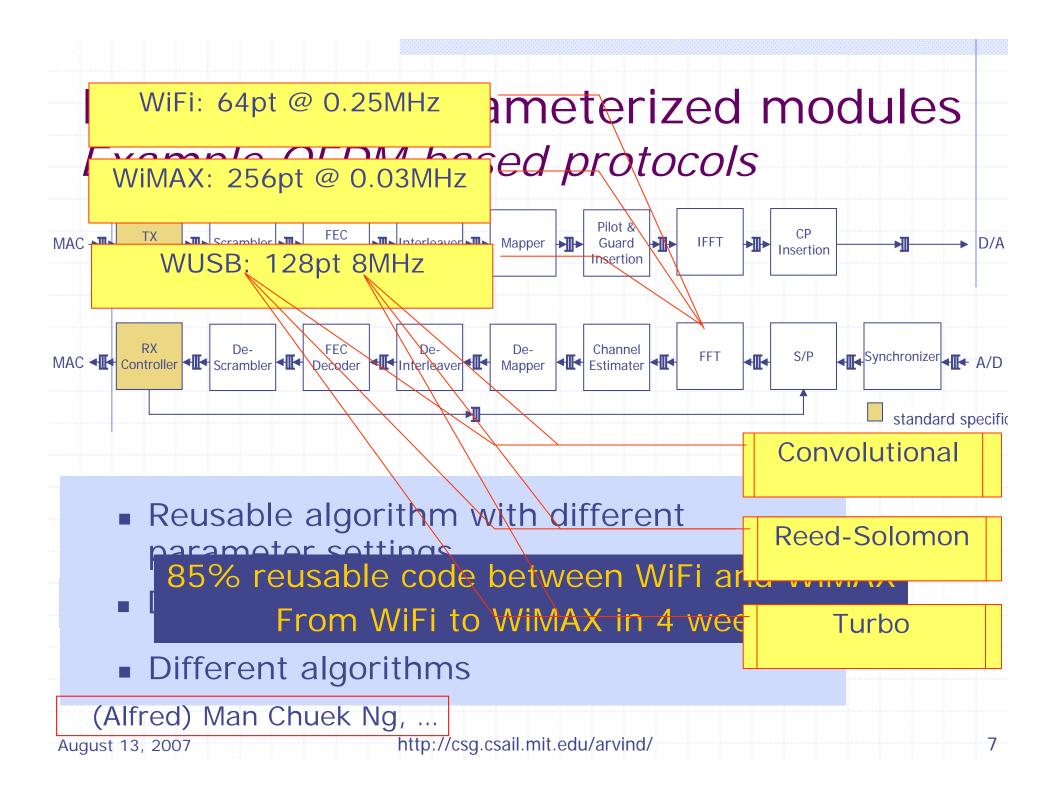

- Multiradio OFDM: From WiFi to WiMax

- 802.11a and 802.16 from the same source

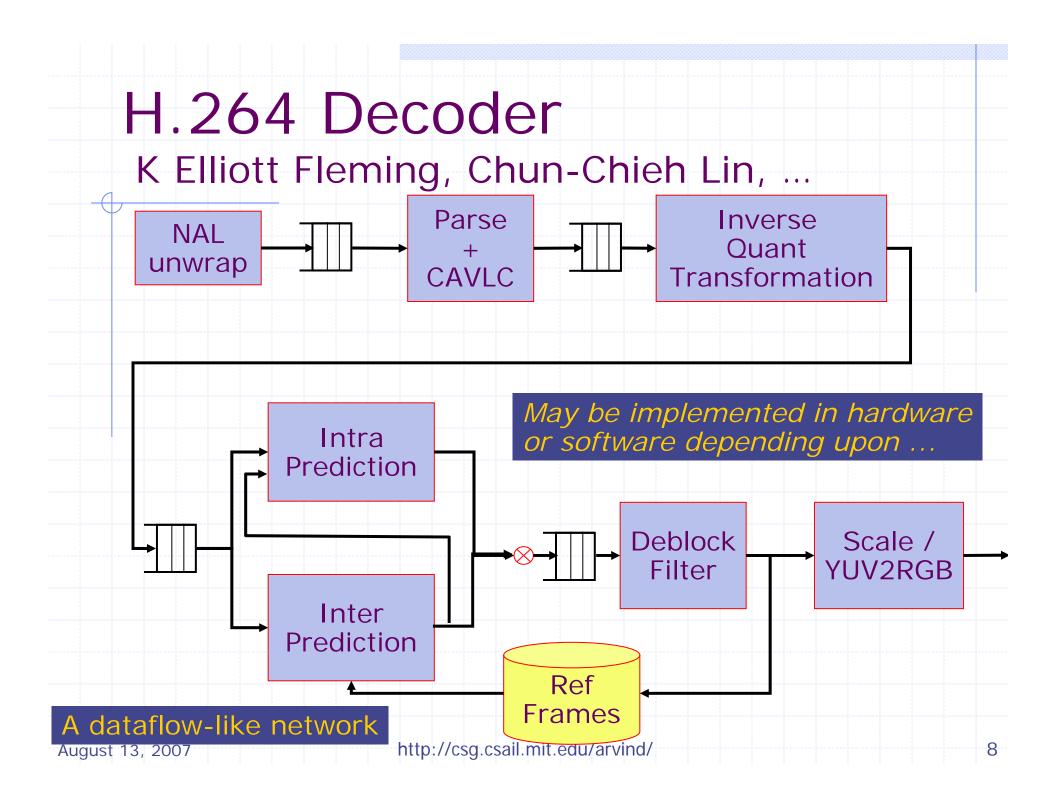

- H.264 Decoder

- Baseline profile, 720p X ~75 frames

- FPGA implementation working

Other examples: Processors, Cache Coherence Protocols, IP Lookup, ...

> Negotiations are underway with sponsors to publish all designs done at MIT under the MIT open source license

August 13, 2007

http://csg.csail.mit.edu/arvind/

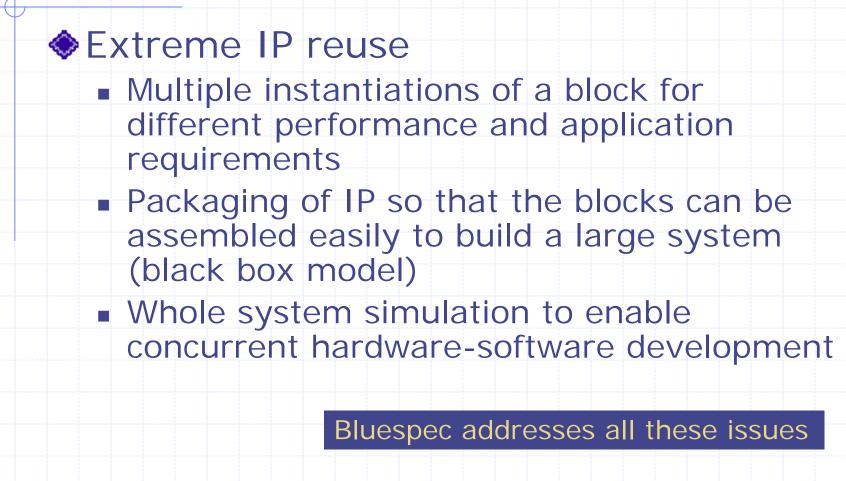

Importance of Publishing Bluespec Designs

Enables whole community to undertake much more ambitious projects

We already see the effects in 6.375 projects

Enables derivative designs, specializations and variety at a fraction of the development cost

August 13, 2007

### H.264 Learnings

Productivity: Base profile

- Effort: Less than one-man year

- 8K lines of Bluespec (contrast 20k to 80K lines of C)

- First draft decoded 720p @ ~32fps, (Available C codes do not meet this performance)

- Architectural Exploration: Many improvements made over a period of sevral months to increase performance and reduce area

- Process several samples / cycle

- Adjust FIFO depths

- Pipeline modules: Interpolator, Deblocking filter

- After improvements decodes 720p @ ~95fps (180nm)

#### Modular refinement is both feasible and essential

#### Current research

- Make the path to hardware design easier

- FPGA emulation infrastructure

- Set up an infrastructure to study power related optimizations

- Hardware-software interaction: test benches, device drivers, transaction-level modeling

- Continue to explore new examples: PowerPC

- Semantic extensions and associated compiling schemes

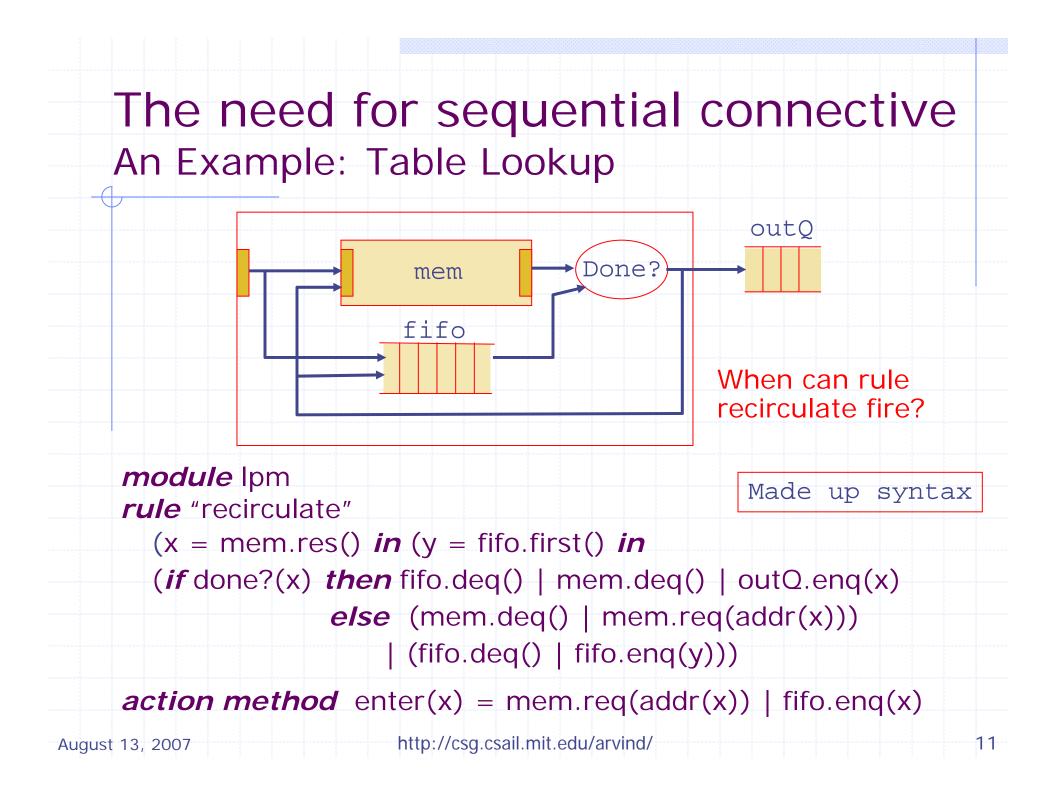

- The sequential connective: Control over scheduling, Multi-cycle atomic actions

- Recursive method calls

Exploratory: Compiling Bluespec for multicores

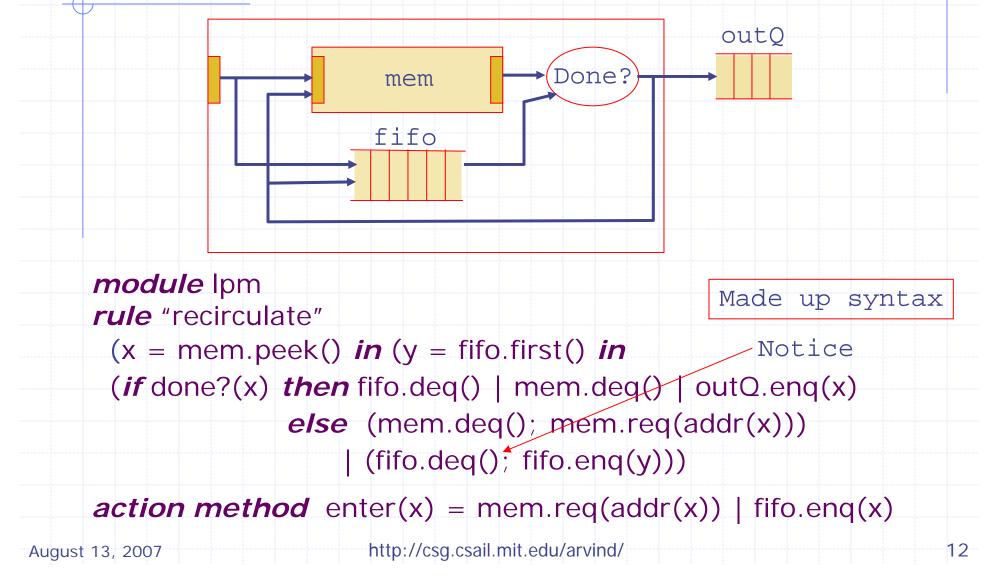

# Table lookup using the sequential connective