# Bluespec Product Status and Direction

# Source: Arvind

# A long time ago....

### A tool....

### Content....

# Templates....

# Community....

# Making things faster and easier

A long time ago....

A tool....

Content....

Verilog

**VHDL**

Threads

SystemC

+ Debug

+ ...

# Templates....

# Community....

| <b>L</b> |                                                                                              | Diuespec.com  Outspec Francis  Dirac Calaborit Memberist Susegnus  Diracis Statu have no new messages Statut out componanties! |        |                                                                |

|----------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------------|

| DI       |                                                                                              |                                                                                                                                |        |                                                                |

| The time | visited on Wed Aug 08, 2007 7-45 am<br>now is Wed Aug 06, 2007 3:36 pm<br>ec.com Forum Index |                                                                                                                                |        | View posts since last v<br>View your po<br>View unexposered po |

|          | Farmin                                                                                       | Trajex                                                                                                                         | Paieta | Last Pest:                                                     |

| Annou    | ncements                                                                                     |                                                                                                                                |        |                                                                |

| 0        | Announcements                                                                                | 1.3                                                                                                                            | 1      | Tue Hay 08, 3007 11:39 a                                       |

| Bluesp   | pec SystemVerillog                                                                           |                                                                                                                                |        |                                                                |

| 0        | Designing with BSV's Rules, Interfaces,                                                      |                                                                                                                                |        | The Aug 03: 2007 4:17 at patil highlighted #4                  |

| 0        | Tools: BSC (Bluespec Compiler)                                                               |                                                                                                                                | 15     | Fri Jul 27, 2007 6:00 pm<br>Daugh #0                           |

| 0        | Tools: Illuesim                                                                              | 2                                                                                                                              | *      | The Jul 18, 2007 12:46 pr<br>(00000000 #Q)                     |

| 0        | Tools: Other                                                                                 | Ni.                                                                                                                            |        | Wed 3ul 04, 2007 12:31 p                                       |

| ESE (    | ESL Synthesis Extensions)                                                                    |                                                                                                                                |        |                                                                |

Open Content:

Designs Tools Templates

# Where we are and where we're going

- Bluespec status

- Bluespec product direction

- Growing the community

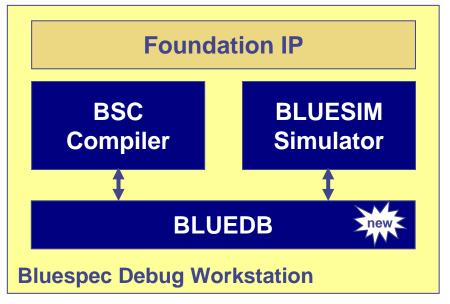

#### **Product Status**

- What's relatively new:

- Multiple clock domain (MCD) completion

- Bluesim simulator (including MCD)

- AzureIP Foundation Library: specifically, bus fabrics and EVE transactors

- 08-2007 Bluespec release due shortly

- Will be posted on new Forums please register!

- <a href="http://www.bluespec.com/forum/">http://www.bluespec.com/forum/</a> (or available off support area)

- Highlights:

- Bluesim

- BSV-to-SystemC (Beta)

- Rule scheduling attribute enhancements

- Lots more enhancements & bug fixes

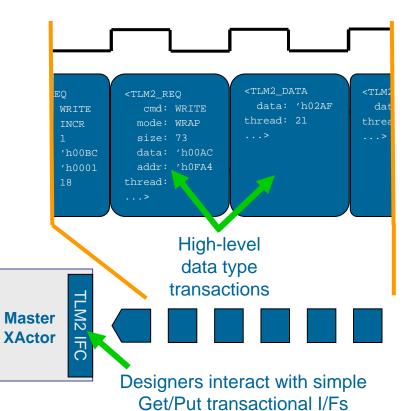

# AzurelP<sup>™</sup> foundation libraries: ESL... only faster!

# Main Categories

(Modules, Data Types & Functions):

Connectivity – transactional I/Fs

Storage - FIFOs, registers, ...

Math – fixed point, complex, ...

Aggregation - vectors, lists

**FSM** – finite state machine language for sequential, parallel, conditional, loop structures

Clock Domains (MCD) - clock synchronizers, ...

Utility – completion buffer, random number, ...

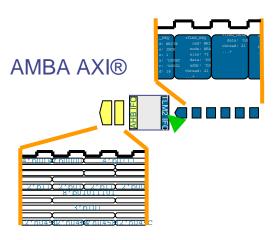

- NEW! Bus Fabric AMBA® AXI® & AHB and OCP

- NEW! EVE transactors, models

#### Just in the Aggregation Library:

#### Data types:

- vector data type holding elements of one type

- · list similar to vector, but used when element numbers

#### Over 125 functions. A sampling:

- newVector generates vector of undefined elements

- genVector creates vector of #s from 0 to n-1

- replicate creates vector based on single element

- · genWith applies function to vector

- · cons adds element to vector

- · append combines two vectors into a third

- · concat combines vector of vectors into one vector

- [i] or select extract (an) element(s)

- · update updates element in vector

- head extracts head of vector

- last extracts tail of vector

- tail removes the head element leaving the rest

- init removes the tail element leaving the rest

- · take take number of elements from start of vector

- takeTail create new vector by dropping head element(s)

- takeAt take number of elements starting at any position

- rotate move the first element to the last and shift rest

- rotateR move last element to the first and shift rest

- rotateBy shift each element n places and rotate

shiftInAt0 shift in at head and drop tail

- ShirtinAtu Shirt in at nead and drop tai

- shiftInAtN shift in at index N and drop tail

reverse reverses element order

- transpose matrix transposition of vector of vectors

- · transposLN matrix transposition of vector of lists

- elem check if a value is an element of a vector

- any test if predicate holds for any element of vector

- all test if predicate function holds for all elements of vector

- countElem returns number of elements that match value

- · countlf returns number of elements that match predicate function

- findElem returns index of element which equals value

- · findIndex returns index of element which satisfies predicate function

- rotateBitsBy shifts bits left in bit-vector

- countOnes returns number of elements equal to one in bit-vector

- countLeadingZeros returns number of leading zeros in bit-vector

- · zip combines two vectors into vector of tuples

- unzip separate vector of pairs into two vectors

- map map a function over a vector, returning new vector

- zipWith combine two vectors with a function

- fold reduce a vector by applying function over all its elements, using binary tree

- mapPairs map a function over a vector consuming two elements at a time

- joinActions join number of actions together

- joinRules join number of rules together

- scanr apply function over vector, creating new vector result, start at highest

- mapAccumL map a function, but pass accumulator from head to tail

- mapM takes monadic function and a vector and applies function to elements

- mapM\_ mapM, but throws away vector leaving action

# Bluespec AzurelP<sup>TM</sup> for Bus Fabrics

4'b0000

2'b01

AHB IFC

2'b00

32'h045C

4'b0111

2'b11

8'b01011101

3'b101

32'h0454 \ 32'h0458

Standard bus protocols, AMBA® AXI® & AHB and OCP, abstracted to...

4'b0010

2'b11

32'h0450

...high-level transactions & data types

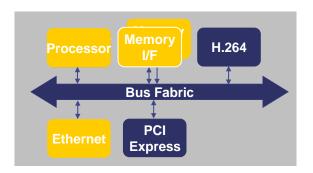

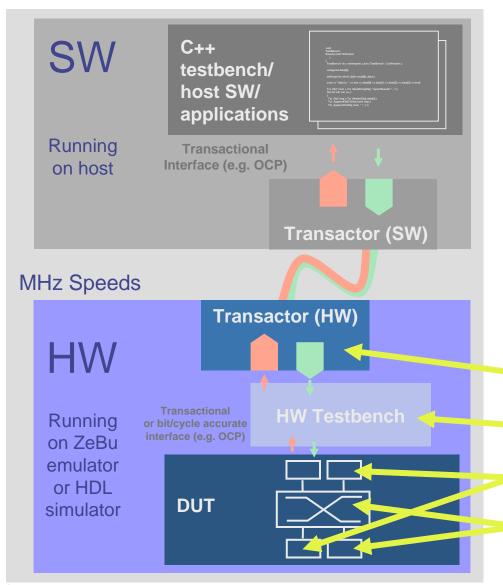

# Accuracy and Speed Early: Accelerating Architecture, Modeling, Implementation and Verification

Bluespec for synthesizable:

- Transactors (transaction-level, high-level types)

- Testbenches (FSM, atomic stimulus, random number, ..)

- Models (e.g. traffic gen/memory/ high-level customer designs)

- Implementations (e.g. AMBA® AXI®/ OCP/customer block/DMA)

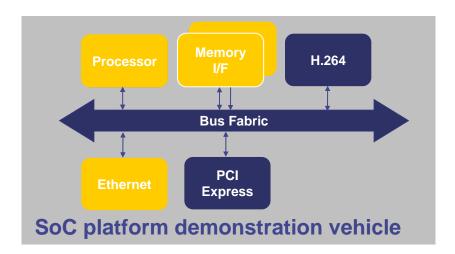

## **Bluespec Product Direction**

- SoC demonstration platform initiative:

- SoC composition

- Synthesizable models <-> implementations

- Legacy IP integration

- Ongoing enhancements to compiler and simulator

- E.g. Bluesim performance

- AzurelP library: OCP next... then...

- Enhanced design experience:

- Source level debug: high-level types & rules

- Integrated design, debug & simulation

# Growing the Community

- University program update:

- Now providing free tools to universities

- Forms on the website under Partnerships and Affiliations

- Please spread the word!

- Discussion Forums: <a href="http://www.bluespec.com/forum/">http://www.bluespec.com/forum/</a>

Please encourage participation: both questions <u>and</u> responses

- Working on:

- A Wiki! Goal: support both Bluespec content & community content

- Open source designs

Would love to hear ideas, suggestions and feedback:

George Harper

george.harper@bluespec.com

781-250-2207