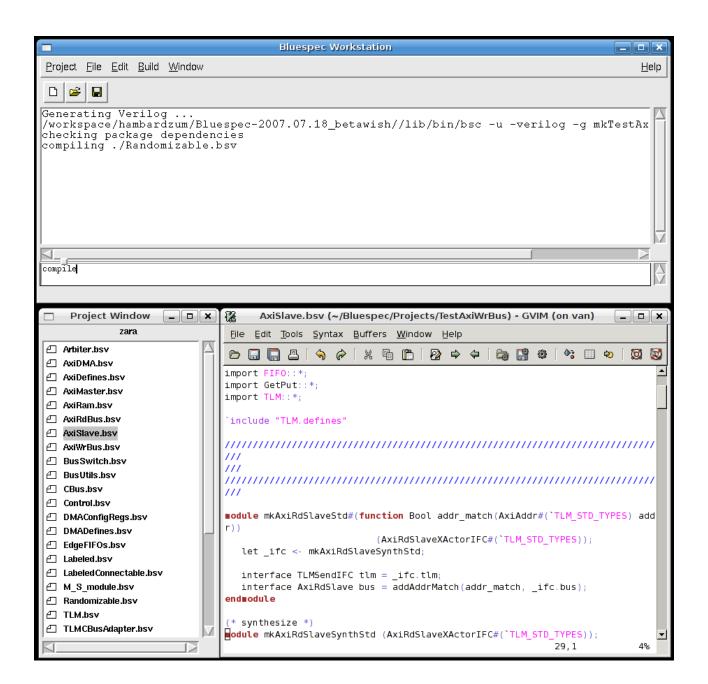

# Preview of Bluespec Debug Workstation

#### Overview

Bluespec Workstation integrating development and debug with Bluespec SystemVerilog

#### Features:

- Single environment for compile, debug, simulate

- Supports standard tools (editors, simulator, waves)

- Adds Bluespec specific analysis

#### Releases:

- Beta, Fall 2007

- General, Q1 2008

## Bluespec Analysis Features

- Provide source level view of high-level data

- Details hierarchical view of advanced types (structures, unions, enumeration, interfaces)

- Maps complex types into Verilog bits

- Links structures to wave viewing

- Provides graphical tools to analyze and verify rule schedule and method use

- Allows users to develop scripts for custom analyses or reports

- Beta, Fall 2007

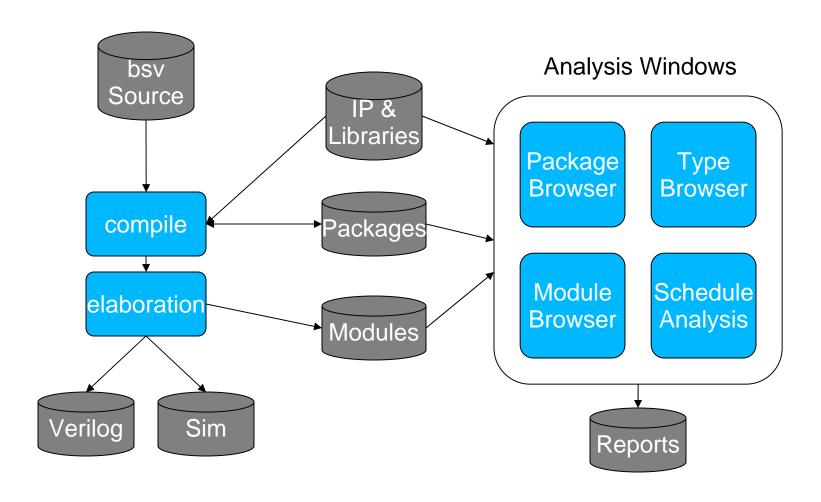

### Workstation Architecture

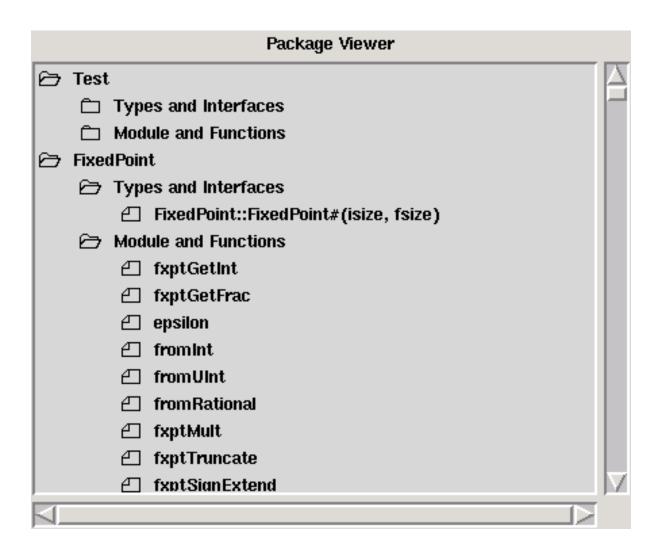

## Package Browser

- Pre-elaboration view of design

- View package contents including:

- Interfaces & types with type parameters

- Modules & functions with argument type

- Links to source

# Package Browser

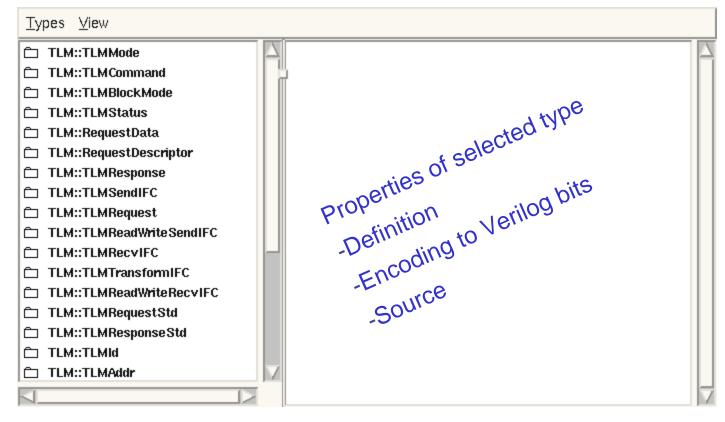

## Type Browser

- Interactive type analysis

- Show details of any type

- polymorphic or concrete

- recursively expand interfaces, structs and unions

- show fields and mapping to Verilog bits

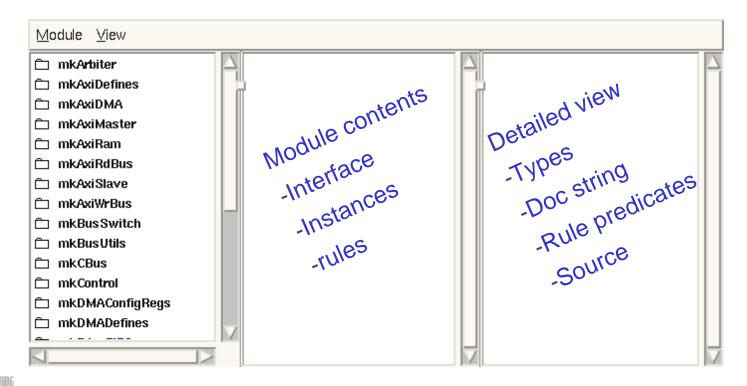

#### Module Browser

- Post-Elaboration Viewer

- Show module hierarchy and composition

- instance name, types, and doc

- rule predicates and method calls

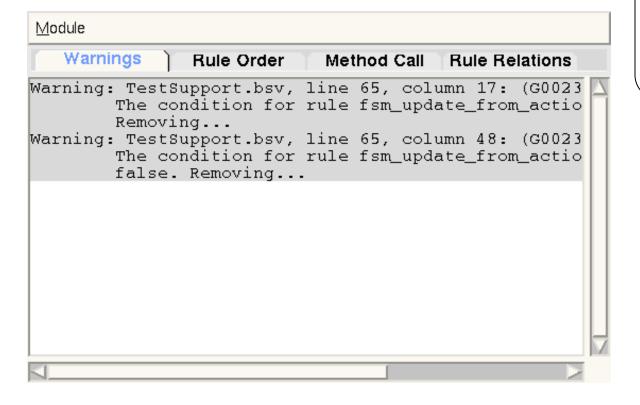

## Schedule Analysis

- View and Analyze Schedule

- Rule execution order

- Instance/method call use table

- Blocking rule

- Messages from scheduling

- Relation between any pairs of rule

- Possible to add custom report

# Schedule Analysis

#### Phase II Features

- Extend to Dynamic (simulation time) analysis

- Tight integration with Bluesim simulation: e.g. rule execution, rule condition analysis, interactive control, breakpoints, etc

- Design analysis, e.g., design structure, flop count, path delay estimates

- Others

- Scheduled Spring 2008

#### Feedback

Would love to hear suggestions and feedback:

Ed Czeck support@bluespec.com