# LABORATORY FOR COMPUTER SCIENCE

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

# Specification of Memory Models and Design of Provably Correct Cache Coherence Protocols

Computation Structures Group Memo 398 May 2, 1998

Xiaowei Shen and Arvind

This paper describes research done at the Laboratory for Computer Science of the Massachusetts Institute of Technology. Funding for this work is provided in part by the Advanced Research Projects Agency of the Department of Defense under the Office of Naval Research contract N00014-92-J-1310 and Ft Huachuca contract DABT63-95-C-0150.

545 TECHNOLOGY SQUARE, CAMBRIDGE, MASSACHUSETTS 02139

# Specification of Memory Models and Design of Provably Correct Cache Coherence Protocols

Xiaowei Shen and Arvind

May 2, 1998

#### Abstract

We propose a two-phase Imperative-Directive design methodology for designing cache coherence protocols, and use it to develop a family of protocols to implement Sequential Consistency in a distributed system with hierarchical caches. In the Imperative design phase, actions or state transitions are defined to ensure that the system only exhibits behaviors that are consistent with the memory model. In the Directive design phase one ensures liveness, i.e., the system eventually takes the desired action. In each design phase the protocol can be refined incrementally to accommodate implementation constraints. The separation of correctness and liveness concerns (and successive refinement) greatly simplifies protocol design and verification. The methodology is especially suitable for designing adaptive protocols which essentially allow imperative actions to be invoked adaptively according to program access patterns.

# 1 Introduction

The design of cache coherence protocols plays an important role in building parallel or distributed systems that support shared memory. Protocols can be implemented completely in hardware or completely in software or using a combination of the both. The performance of shared memory systems largely depends on the cache coherence protocols that are responsible for maintaining a coherent view of replicated data in accordance with a memory model. Over the years, the desire to achieve higher performance has resulted in more and more sophisticated cache coherence protocols, which are difficult to design and verify. In this paper we present a new Imperative-Directive methodology for designing protocols and verifying them against a memory model. The methodology is illustrated through an elaborate protocol that implements Sequential Consistency on DSM (Distributed Shared Memory) systems with hierarchy of caches.

#### 1.1 Memory Models

A memory model is a contract that specifies the memory behavior which the system implementors (architects, compiler writers, etc.) provide to the programmers. Sequential Consistency [17] has been the dominant memory model in parallel computing for decades, but for performance reasons, both architects and compiler writers have been exploring alternative memory models that allow more implementation flexibility. Architects prefer weaker instruction orderings (see, for example, PowerPC [19]), which often give rise to relaxed memory models such as Weak Consistency [8], Release Consistency [10, 11] and Lazy Release Consistency [15]. The language and compiler community have suggested their own relaxed memory models such as Location Consistency [9] and DAG Consistency [5]. One problem with relaxed memory models is that even experts may not agree on their precise definition.

We have chosen Sequential Consistency [17] to demonstrate our methodology for designing protocols. This is not because we believe Sequential Consistency is the most desirable memory model, but rather because there is a consensus on its definition. The correctness of a protocol to implement a memory model can be discussed only if there is a precise specification of the memory model. It is important that the specification be independent of any specific implementation, and thus of caches, write buffers and interconnection networks etc. We will present an operational but fairly abstract view of Sequential Consistency, and then design protocols that admit exactly those behaviors that are permitted by this operational model. Needless to say that the same technique can be applied to designing and verifying coherence protocols for other memory models.

#### 1.2 Design Methodology

In spite of the number of publications on cache coherence protocols [12, 18, 16, 1, 2], it is difficult to discern a methodology that has guided the design of these protocols. A major source of difficulty in protocol design is that designers often try to deal with many different issues simultaneously. Are cache states being maintained correctly? Is deadlock possible due to reordering of messages or lack of buffers in the network? What is the consequence of having write buffers and allowing instructions to be executed out-of-order? Answering these questions can be difficult in asynchronous systems with distributed control. The net result is that protocol design is viewed as black magic, where even the designers are not totally confident of their understanding of the protocol behavior.

We propose a two phase Imperative-Directive design methodology to rectify this problem. The methodology completely separates the *correctness* and the *liveness* concerns in the design process. Correctness ensures that the system can only exhibit behaviors that are allowed by the memory model. The rules that specify such state transitions are called *imperative rules*. The protocol designer initially focuses on developing a complete set of imperative rules. In the second phase, the main concern is liveness, i.e., ensuring via *directive rules* that the system always takes appropriate imperative actions at appropriate times. Improper conditions for invoking imperative rules can cause deadlocks or livelocks but cannot affect the correctness of the system.

By separating the correctness and the liveness concerns, the Imperative-Directive methodology can dramatically simplify the design and verification of cache coherence protocols. Protocols designed using this methodology are often easy to understand, modify and reason about. We illustrate our methodology by successively developing a family of cache coherence protocols to implement Sequential Consistency on DSM systems with hierarchy of caches. The final protocol is, to our knowledge, the first precise description of a provably correct coherence protocol for DSM systems with multi-level caches. The methodology has proved extremely effective in designing adaptive cache coherence protocols [23] because adaptability is only about when and how to invoke imperative actions; imperative rules remain unaffected.

#### **1.3** Formal Verification

The verification of cache coherence protocols has gained considerable attention in recent years [4, 27, 22, 21]. Most methods verify certain invariants for cache coherence protocols, and are based on state enumeration [13, 14] and symbolic model checking [6, 7, 20], which can check correctness of assertions by exhaustively exploring all reachable states of the system. For example, Stern and Dill [27] use the Mur $\varphi$  system to automatically check if all reachable states satisfy certain properties which are attached to protocol specifications. Pong and Dubois [21] exploit the symmetry and homogeneity of the system states by keeping track of whether zero, one or multiple copies have been cached. This reduces the state space and makes the verification independent of the number of processors. Generally speaking, the major difference among these techniques is the representation of protocol states and the pruning method adopted in the state expansion process.

Exponential state explosion has been a serious concern for model checker approaches. Another problem is that it is often difficult to choose the invariants in a systematic manner or to convince oneself that all the important invariants have been considered. While some invariants are obvious (e.g., two L1 caches should not contain the same address in the exclusive state simultaneously), many others are motivated by the specific protocol implementation instead of the memory model. Sometimes it is not even clear if the chosen invariants are necessary or sufficient for the correctness. This means that for the same memory model, we may have to prove very different properties for different implementations. In this sense, these techniques are more like a bag of useful tools for debugging cache coherence protocols, rather than for verifying them.

The difficulty of protocol verification with current approaches can be largely attributed to the fact that protocols are designed and verified separately and sequentially. In our approach, both the memory model and the protocol are expressed in the same formalism, and there is a notion of when one system *completely implements* another system. We begin with a baseline protocol as the operational specification of the memory model, and then refine the protocol successively by incorporating more and more implementation and optimization details. Protocols are designed and verified iteratively throughout the successive process. The invariants that need to be verified are usually straightforward, because the semantics gap between the two models associated with each refinement step is relatively small. Our experience shows that most of the commonly known invariants systematically show up as lemmas and can be verified by case analysis on rewriting rules.

### 1.4 The Organization of the Paper

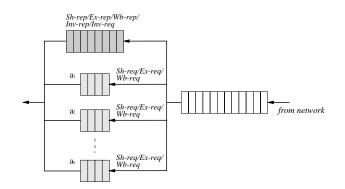

We begin with a brief introduction to our formalism, Term Rewriting Systems, and the notion of a complete implementation with respect to a specification. In Section 3 we give a baseline protocol, the SC model, which will be used as the specification of Sequential Consistency. We define the HC model, a directory-based coherence protocol for DSM systems with hierarchical

Figure 1: Successive Design Process (SC is the specification of Sequential Consistency, HC defines a protocol for systems with hierarchical caches, HCN is a refined version of HC with message passing, and HCN-base is a HCN-based cache coherence protocol that is free from deadlock and livelock)

caches, and prove that HC is a complete implementation of SC (Sections 4 & 5). Some derived rules of HC are discussed in Section 6. Then we define the HCN model by refining HC with message passing, and prove that HCN is a complete implementation of HC (Sections 7 & 8). This is followed by a discussion of potential optimizations of HCN in Section 9.

In Section 10 we start with a general discussion regarding the liveness issue, and then introduce directive messages and directive rules. We present HCN-base, a simple protocol derived from HCN, and show that the protocol implements Sequential Consistency and guarantees that each processor can always make progress (Sections 11 & 12). The design of HCN-base is completed in Section 13 with a buffer management policy that ensures fair message processing. Finally we present a summary and briefly discuss our research in progress.

# 2 The Formalism

Our formal framework is based on Term Rewriting Systems (TRS's). We use TRS's to specify the operational behavior of memory models and cache coherence protocols. A TRS consists of a set of terms and a set of rewriting rules. In the architectural context, the terms represent system states and the rules specify state transitions. The general structure of rewriting rules is as follows:

$$\begin{array}{ccc} s_1 & if & p(s_1) \\ \hline & & s_2 \end{array}$$

where  $s_1$  and  $s_2$  are terms, and  $p(s_1)$  is an optional predicate about term  $s_1$ .

A rule can be used to rewrite a term if its left-hand-side pattern matches the term or one of its subterms, and the corresponding predicate is true. If several rules are applicable, then any one of them may be applied. If no rule is applicable, then the term cannot be rewritten any further and is said to be in *normal form*. Sometimes a rewriting strategy is used to specify which rule among the applicable rules should be applied to a term at every step.

We say term  $s_1$  can be rewritten to term  $s_2$  in one rewriting step  $(s_1 \longrightarrow s_2)$ , if there exist a context  $\mathbb{C}[\![\,]\!]$  and terms  $s'_1$  and  $s'_2$  such that  $s_1 = \mathbb{C}[\![s'_1]\!]$  and  $s_2 = \mathbb{C}[\![s'_2]\!]$ , and  $s'_1$  can be rewritten to  $s'_2$  according to some rewriting rule. (A context is a term with a "hole" that can be filled by a term.  $\mathbb{C}[\![s]\!]$  refers to the term in which the hole is filled by term s). We say term  $s_1$  can be rewritten to term  $s_2$  in zero or more rewriting steps  $(s_1 \longrightarrow s_2)$ , if either  $s_1 = s_2$ , or there exists a term s' such that  $s_1 \longrightarrow s'$  and  $s' \longrightarrow s_2$ .

A term s is a legal term if there exists  $s_0 \in S_0$  such that  $s_0 \longrightarrow s$ . Since we are only interested in legal terms, we will drop the qualifier "legal" in our discussion.

A TRS is *confluent* if, for any term  $s_1$ , if  $s_1 \longrightarrow s_2$  and  $s_1 \longrightarrow s_3$ , then there exists a term  $s_4$  such that  $s_2 \longrightarrow s_4$  and  $s_3 \longrightarrow s_4$ . A TRS is *strongly terminating* if, for any term, it can always be rewritten to a normal form using any rewriting strategy.

**Notations:** While pattern matching it is important to distinguish between variables and constants or data-structure constructors. A variable matches any expression while a constant or constructor matches only itself. Throughout the paper, we will follow the convention that variables are represented by identifiers with only lower-case letters, while constants and constructors are represented by either identifiers that begin with a capital letter, or special characters such as '|', ' $\odot$ ', and ' $\otimes$ '. We use ' $\epsilon$ ' to represent the empty term, and '-' the wild-card term that can match any term.

#### 2.1 Correctness of an Implementation

The use of TRS's allows us to define and prove when a protocol implements a memory model correctly. The proof is based on showing that the TRS for the protocol admits only the observable behaviors that are permitted by the memory model. We say that system Bis a *complete implementation* of system A if there exists a pair of mapping functions g ( $B \mapsto A$ ) and f ( $A \mapsto B$ ), such that

- 1. Soundness:  $s_1 \xrightarrow{B} s_2 \implies g(s_1) \xrightarrow{A} g(s_2);$

- 2. Completeness:  $s_1 \xrightarrow{A} s_2 \implies f(s_1) \xrightarrow{B} f(s_2);$

- 3. Connection: g(f(s)) = s.

The soundness property states that an implementation cannot take a step that is inconsistent with the specification, while the completeness property states that an implementation can imitate every possible step of the specification. Together these conditions can be interpreted as saying that the two systems can *simulate* each other. However, the correspondence between the implementation and the specification has not been properly confined with just these two conditions. For example, consider a function that maps all implementation terms to the same specification term. The connection property rules out such unreasonable mapping functions. The intuition behind this property is that an implementation term contains enough information to reconstruct the corresponding specification term. It is important to notice that the connection property is asymmetric, i.e., f(g(s)) does not necessarily equal to s. This is because an implementation term usually contains extra information that cannot be reconstructed once it is projected to a term in the specification.

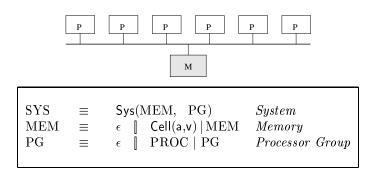

Figure 2: The SC Model (Initially, the memory contains a cell for each address)

The notion of complete implementation is transitive, i.e., if system C is a complete implementation of system B, which is in turn a complete implementation of system A, then system C is a complete implementation of system B. This implies that the proof that a protocol is a complete implementation of a memory model can be carried out step-by-step throughout the successive design process. Needless to say any system is a complete implementation of itself.

Many real implementations are not complete according to the above definition. Any sound system can be regarded as a *partial implementation* of the specification. However, some partial implementations can be pretty silly in reality: for example, an implementation that has no rewrite rule and thus makes no transition is a partial implementation of any specification by the virtue of being sound.

# 3 The SC Model: Specification of Sequential Consistency

Intuitively, a system is sequentially consistent if the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appears in this sequence in the order specified by its program [17]. We take a slightly different approach and define Sequential Consistency operationally using a multiprocessor system based on a simple non-pipelined processor, which has no caches or write buffers and which executes instructions sequentially. The system is defined using a TRS called SC. All the protocols presented in this paper implement only those behaviors that are permitted by SC.

The grammar of the SC model is given in Figure 2. The system has two components, a memory and a processor group. The memory consists of a set of memory cells, where each memory cell has an address and a value. We assume addresses in a memory are pairwise distinct. The processor group consists of a set of processors where each processor has a program counter, a register file, and a program. The processor grammar and rules are presented in [24] and understanding them is not necessary to follow the rest of the paper as long as we remember that instructions are executed strictly according to the program order (the program counter holds the address of the instruction to be executed).

Notations: We use '[]' as meta notation in grammars to separate disjuncts (SYS, MEM and PG are grammar symbols). Identifiers such as Sys, Cell and Proc are constructors. Notation prog[ia] refers to the instruction at instruction address ia in program prog. We use rf[r] to represent the content of register r in register file rf, and rf[r := v] to represent the register file which is the same as rf except that register r contains value v.

We use '|' as an associative and commutative constructor  $(s_1 | s_2 = s_2 | s_1 \text{ and } s | \epsilon = s)$ . As we shall see, it can be used as a connective for terms such as processor groups, system groups and directories, which are intuitively associative and commutative.

The memory access rules are defined as follows:

Since the connective '|' is associative and commutative, any processor can be brought into the leftmost position in the processor group. Thus, if two processors intend to write to the same address, either can be allowed to proceed. Non-determinism can happen due to data races, however, memory access atomicity is guaranteed because there is no data replication and the Load and Store operations are performed directly on the memory.

We claim that SC define an operational semantics for Sequential Consistency although it has different flavor from the traditional definition. It is easy to show that a total instruction order, consistent with the program order for each individual processor, exists for all instructions. From now on we identify the range of behaviors admitted by Sequential Consistency as precisely the set of legal terms of SC. In the rest of the paper we will present several cache coherence protocols to implement Sequential Consistency and show that they admit only SC behaviors.

# 4 The HC Model: A System with Hierarchical Caches

A typical distributed memory system consists of multi-level caches and uses different implementation technologies and possibly different protocols in different parts of the system. In this section, we define a directory-based cache coherence protocol for a system with hierarchy of caches and call it the HC (Hierarchical Caches) model. In HC, we ignore the communication latency between memory sites, and assume that coherence actions involving two or more memory sites (e.g., a local read followed by a remote write) can be performed in one rewriting step.

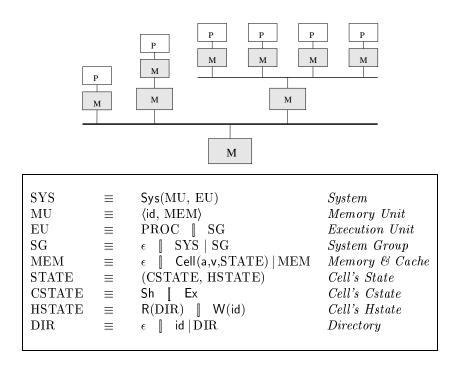

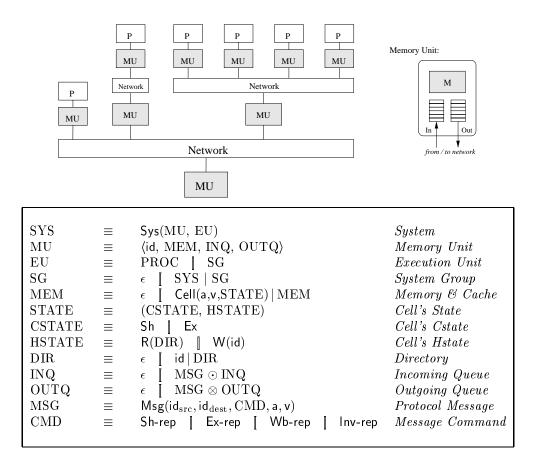

The grammar of the HC model is given in Figure 3. The system has two components, a memory unit and an execution unit. The memory unit consists of an identifier and a memory. A memory is a set of memory cells, where each memory cell has an address, a value and a state used for coherence maintenance. The execution unit is either a single processor, or a

Figure 3: The HC Model (Initially, all memories except the outermost memory are empty; the outermost memory contains a cell for each address and the state of each cell is  $(E_x, R(\epsilon))$ )

system group that consists of a set of systems. This recursive definition effectively allows arbitrary levels of cache hierarchy. Notice that although we show each memory as one block pictorially, in implementation addresses can be divided among multiple sites.

In the memory hierarchy, the memory at the root is called the outermost memory, and the memories that directly interface with processors are called innermost memories or L1 caches. Every memory except the innermost and outermost behaves simultaneously as a *cache* and *home*, that is, for its parent a memory is a cache which holds replicated data, and for its children it is the home where all the cells that have been cached by the children reside. Thus, we do not draw a distinction between "cache" and "memory", and use the two words interchangeably. Given a memory id, parent(id) represents its parent's identifier, children(id) the set of identifiers for its children, and siblings(id) the set of identifiers for its siblings.

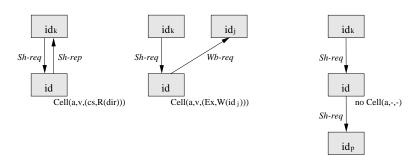

#### 4.1 State Encoding

Each memory cell contains an address, a value and a state for coherence maintenance. The state in each cell has two components, Cstate (cache state) and Hstate (home state). The Cstate is the "horizontal" state that indicates whether the cell is shared (Sh) or exclusive (Ex) with respect to its sibling caches. The Hstate is the "vertical" state that records which children have cached the data and for which purpose (i.e., for reading or writing). If the Hstate is R(dir), shared copies are cached in the children specified by the directory dir, which is a set of memory identifiers. If the Hstate is W(id), the child memory id has the exclusive copy for the address and can write into the cell.

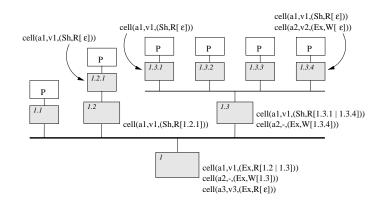

Figure 4: A Snapshot of Coherent States (For example, in memory  $m_{1.3}$ , the state for address  $a_1$  is  $(\mathsf{Sh}, \mathsf{R}(m_{1.3.1} | m_{1.3.4}))$ , indicating that the cell is a read-only copy and its child memories  $m_{1.3.1}$  and  $m_{1.3.4}$  have cached shared copies at the time; the state for address  $a_2$  is  $(\mathsf{Ex}, \mathsf{W}(m_{1.3.4}))$ , indicating that the cell is a read-write copy and the exclusive ownership has been given to child memory  $m_{1.3.4}$ )

The Hstate is always  $R(\epsilon)$  for the cells in the innermost memories, because the innermost memories cannot have children. Similarly the Cstate is always Ex for the cells in the outermost memory, because it has no siblings. It is worth noting that (Sh,W(id)) is an illegal state, because a memory cannot give the write permission to any child unless it has obtained the exclusive ownership for that address. A snapshot of hierarchical caches in coherent states is shown in Figure 4.

**Inclusion Invariants:** The protocol can be implemented efficiently if, by checking a cell's state in a memory, it can be determined whether any further coherence actions need to be taken for its descendant memories. To accomplish this, HC maintains two invariants, namely *shared inclusion* and *exclusive inclusion*. The shared inclusion invariant states that, if a memory has a shared copy, its parent must have the address with the same value. The exclusive inclusion invariant states that, if a memory has an exclusive copy, its parent must have the address exclusive copy, its parent must have the address exclusive copy, its parent must have the address exclusive copy.

### 4.2 Rewriting Rules

The rewriting rules of the HC model are all imperative rules and fall naturally into three categories: the rules for memory access operations (i.e., Load and Store), the rules for caching operations (i.e., moving data and/or coherence information from parents to children), and the rules for de-caching operations (i.e., moving data and/or coherence information from children to parents).

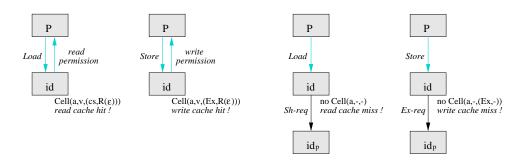

**Memory Access Rules:** Memory access operations by a processor are performed on its L1 cache. A Load instruction can execute if the data is cached in the L1 cache. A Store instruction can execute if the L1 cache has cached the address with the exclusive ownership.

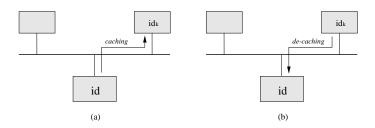

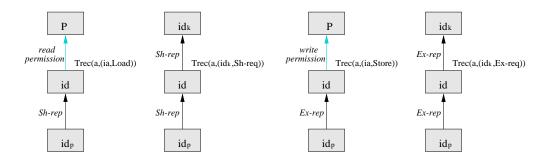

Figure 5: Caching and De-Caching Operations

$\begin{array}{ll} HC\text{-}Load \ Rule \\ & \text{Sys}(\langle \text{id}, \ \text{Cell}(a, v, (cs, \mathsf{R}(\epsilon))) \mid \mathsf{m}\rangle, \quad \text{Proc}(\text{ia}, \ \text{rf}, \ \text{prog})) \\ & if \quad \text{prog}[\text{ia}] = \ \mathsf{r} := \text{Load}(\mathsf{r}_1) \quad and \ \mathsf{a} = \mathsf{rf}[\mathsf{r}_1] \\ \longrightarrow \quad \text{Sys}(\langle \text{id}, \ \text{Cell}(a, v, (cs, \mathsf{R}(\epsilon))) \mid \mathsf{m}\rangle, \quad \text{Proc}(\text{ia}+1, \ \mathsf{rf}[\mathsf{r} := \mathsf{v}], \ \mathsf{prog})) \\ HC\text{-}Store \ Rule \\ & \text{Sys}(\langle \text{id}, \ \text{Cell}(\mathsf{a}, u, (\mathsf{Ex}, \mathsf{R}(\epsilon))) \mid \mathsf{m}\rangle, \quad \text{Proc}(\text{ia}, \ \mathsf{rf}, \ \mathsf{prog})) \\ & if \quad \text{prog}[\text{ia}] = \ \text{Store}(\mathsf{r}_1, \mathsf{r}_2) \quad and \ \mathsf{a} = \mathsf{rf}[\mathsf{r}_1] \\ \longrightarrow \quad \text{Sys}(\langle \text{id}, \ \text{Cell}(\mathsf{a}, v, (\mathsf{Ex}, \mathsf{R}(\epsilon))) \mid \mathsf{m}\rangle, \quad \text{Proc}(\text{ia}+1, \ \mathsf{rf}, \ \mathsf{prog})) \quad where \quad \mathsf{v} = \mathsf{rf}[\mathsf{r}_2] \end{array}$

**Caching Rules:** If the state of a cell in memory id is (-,R(dir)) and the directory dir shows that child  $id_k$  has not cached the data, then memory id can give a shared copy to memory  $id_k$  and record  $id_k$  in the directory. If the state of a cell in memory id is  $(Ex,R(\epsilon))$ , then it can give an exclusive copy to child  $id_k$  and change the cell's Hstate to  $W(id_k)$ . See Figure 5 (a).

**De-Caching Rules:** If the state of a cell in memory  $id_k$  is (Ex,R(dir)), then it can write the most up-to-date data back to the parent and change the cell's Cstate to Sh. If the state of a cell in memory  $id_k$  is  $(Sh,R(\epsilon))$ , then it can invalidate the cell and delete identifier  $id_k$  from the corresponding directory in the parent. See Figure 5 (b).

$\begin{array}{ll} & Writeback \ Rule \\ & & Sys(\langle id, \ Cell(a,u,(Ex,W(id_k))) \mid m \rangle, \ Sys(\langle id_k, \ Cell(a,v,(Ex,R(dir))) \mid m_k \rangle, \ eu_k) \mid sg) \\ \rightarrow & Sys(\langle id, \ Cell(a,v,(Ex,R(id_k))) \mid m \rangle, \ Sys(\langle id_k, \ Cell(a,v,(Sh,R(dir))) \mid m_k \rangle, \ eu_k) \mid sg) \\ & Invalidate \ Rule \\ & & Sys(\langle id, \ Cell(a,v,(cs,R(id_k \mid dir))) \mid m \rangle, \ Sys(\langle id_k, \ Cell(a,v,(Sh,R(\epsilon))) \mid m_k \rangle, \ eu_k) \mid sg) \\ \rightarrow & Sys(\langle id, \ Cell(a,v,(cs,R(dir))) \mid m \rangle, \ Sys(\langle id_k, \ m_k \rangle, \ eu_k) \mid sg) \\ \end{array}$

# 5 Verification of the HC Model

We can prove that the HC model completely implements the SC model. The proof consists of three steps:

1. Soundness: Define cache-flush function CF (HC  $\mapsto$  SC), and show

$$s_1 \xrightarrow{\mathsf{HC}} s_2 \implies CF(s_1) \xrightarrow{\mathsf{SC}} CF(s_2);$$

2. Completeness: Define cache-lift function CL (SC  $\mapsto$  HC), and show

$$s_1 \xrightarrow{\mathsf{SC}} s_2 \implies CL(s_1) \xrightarrow{\mathsf{HC}} CL(s_2);$$

3. Connection: For any SC term s, show CF(CL(s)) = s.

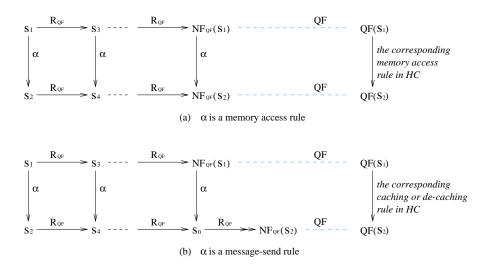

The *CF* function is easy to define once we notice that we can apply the de-caching rules repeatedly to empty all non-outermost caches and propagate all valid values to the outermost memory. To show soundness, we prove that if  $s_1 \longrightarrow s_2$  by applying some rule  $\alpha$  in HC, then in SC, either  $CF(s_1) = CF(s_2)$  if  $\alpha$  is a caching or de-caching rule; or  $CF(s_1) \longrightarrow CF(s_2)$  (by applying some memory access rule) if  $\alpha$  is a memory access rule.

The *CL* function is based on the simple observation that a SC term can be "lifted" to a HC term by introducing empty caches in the memory hierarchy, setting the state for each outermost memory cell to  $(Ex, R(\epsilon))$ , and assigning memory identifiers for all memory units. It is easy to show that each SC rule can be simulated by a sequence of HC rules.

#### 5.1 Inclusion Invariants

The HC model maintains two inclusion invariants. The shared inclusion invariant states that, if a memory has a shared copy, the parent must have the address with the same value. The exclusive inclusion invariant states that, if a memory has an exclusive copy, the parent must have the address and the ownership, albeit the value of the cell can be out-of-date. It is because of these invariants that the cache coherence protocol can determine, simply by checking the a cell's state, if further coherence actions need to be taken for its descendant memories.

**Lemma 1 (Inclusion Invariants)** In any HC term  $Sys(\langle id, m \rangle, Sys(\langle id_k, m_k \rangle, eu_k) | sg)$ ,

- $\bullet \ \mathsf{Cell}(\mathsf{a},\!\mathsf{v},\!(\mathsf{Sh},\!\!\cdot)) \ \in \ \mathsf{m}_k \ \implies \ \mathsf{Cell}(\mathsf{a},\!\mathsf{v},\!(\!\cdot,\!\mathsf{R}(\mathsf{id}_k \mid \! \cdot \! ))) \ \in \ \mathsf{m}$

- $\bullet \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{E}\mathsf{x},\text{-})) \ \in \ \mathsf{m}_k \ \implies \ \mathsf{Cell}(\mathsf{a},\text{-},(\mathsf{E}\mathsf{x},\mathsf{W}(\mathsf{id}_k))) \ \in \ \mathsf{m}$

**Proof** The proof is by induction on rewriting steps. The invariants hold trivially for the initial terms where all non-outermost memories are empty. It can be shown by checking each rewriting rule that, if the invariants hold for a term, then they still hold after the term is rewritten according to that rule.  $\Box$

It can be shown that no memory can contain two cells that have the same address. This is because only caching rules can create new cells (in the child memory). According to the Inclusion Invariants, if a caching rule is applicable, the child memory cannot have a cell that has the same address as the cell that is to be created.

# 5.2 Cache Flushing Property

Suppose we define a new rewriting system  $\mathsf{R}_{\mathsf{CF}},$  which has the same grammar as  $\mathsf{HC}$  but uses only the de-caching rules.

### **Definition 2** (**TRS for cache flushing**) $R_{CF} \equiv \{ Writeback, Invalidate \}$

Now we discuss some properties of the  $\mathsf{R}_{\mathsf{CF}}$  system.

Lemma 3  $R_{CF}$  is strongly terminating and confluent, i.e., for any HC term, rewriting with respect to  $R_{CF}$  terminates within a finite number of steps and always reaches the same normal form, regardless of the order in which the rules are applied.

**Proof** The termination is obvious because  $R_{CF}$  includes only the de-caching rules that can either invalidate Sh cells or degrade Ex cells to Sh cells, but can never create cells or upgrade Sh cells to Ex cells. The confluence follows from the fact that the de-caching rules do not interfere each other.  $\Box$

**Definition 4** For any HC term s,  $NF_{CF}(s)$  is the normal form of s in  $R_{CF}$ .

Lemma 5 (Cache Flushing Property) For any HC term s, all non-outermost memories are empty in  $NF_{CF}(s)$ .

**Proof** Suppose not all non-outermost memories are empty. Consider a non-outermost memory which is not empty and whose descendant memories (if any) are all empty. According to the Inclusion Invariants, either the *Writeback* rule or the *Invalidate* rule would apply, and hence the term cannot be a normal form.  $\Box$

**Lemma 6 (Value Preservation Property)** For any HC term s, if Cell(a,v,(-,R(-))) is in some cache of s, then Cell(a,v,-) is in the outermost memory of  $NF_{CF}(s)$ .

**Proof** This can be shown by checking each de-caching rule.

- When Writeback applies, Cell(a,v,(Ex,R(-))) is in the child and Cell(a,u,(Ex,W(-))) is in the parent; after the writeback, Cell(a,v,(Ex,R(-))) is in the parent memory (i.e., value v is preserved).

- When Invalidate applies, Cell(a,v,(Sh,R(ε))) is in the child and Cell(a,v,(-,R(-))) is in the parent; after the invalidation, Cell(a,v,(-,R(-))) is in the parent memory (i.e., value v is preserved).

By induction, if Cell(a,v,(-,R(-))) is in some cache, Cell(a,v,-) will be in the outermost memory after applying the de-caching rules repeatedly till all non-outermost caches are emptied.  $\Box$

The Value Preservation Property shows that we can propagate all valid values to the outermost memory by repeatedly applying the de-caching rules. This is the key idea behind the cache-flush function used in the soundness proof. It should be noted that  $NF_{CF}(s)$  also preserves all processor states including program counters, register files and programs.

#### 5.3 Soundness of HC

We define function CF (cache-flush) that maps HC terms to SC terms as follows:

**Definition 7 (Cache-flush function)** For any HC term s, CF(s) is the projection of  $NF_{CF}(s)$  on the corresponding SC term where all non-outermost memory units have been deleted along with the coherence states of all the cells in the outermost memory and the identifier for the outermost memory.

**Lemma 8 (Soundness)**  $s_1 \xrightarrow{\mathsf{HC}} s_2 \implies CF(s_1) \xrightarrow{\mathsf{SC}} CF(s_2).$

**Proof** The proof is by induction on rewriting steps. We give the proof for one rewriting step. Assume  $s_1 \longrightarrow s_2$  by applying some rule  $\alpha$  in HC. The proof is based on the case analysis on  $\alpha$ .

- $\alpha \in \mathsf{R}_{\mathsf{CF}}$ . Needless to say  $CF(s_1) = CF(s_2)$ .

- $\alpha$  is Sh-Caching. Then  $s_2 \longrightarrow s_1$  by applying Invalidate, hence  $CF(s_1) = CF(s_2)$ .

- $\alpha$  is Ex-Caching. Then  $s_2 \longrightarrow s_1$  by applying Writeback followed by Invalidate, hence  $CF(s_1) = CF(s_2)$ .

- $\alpha$  is *HC-Load*. Let  $Cell(a,v,(-,R(\epsilon)))$  be the cell in the L1 cache. Then Cell(a,v) is preserved in both  $CF(s_1)$  and  $CF(s_2)$ ; and  $CF(s_1)$  differs from  $CF(s_2)$  only in the program counter and the register modified by the load operation. Thus  $CF(s_1) \rightarrow CF(s_2)$  by applying *SC-Load*.

- $\alpha$  is *HC-Store*. Let  $Cell(a,u,(Ex,R(\epsilon)))$  and  $Cell(a,v,(Ex,R(\epsilon)))$  be the cell in the L1 cache of  $s_1$  and  $s_2$ , respectively. Then Cell(a,u) and Cell(a,v) are preserved in  $CF(s_1)$  and  $CF(s_2)$ , respectively; and  $CF(s_1)$  is the same as  $CF(s_2)$  except for the program counter and the cell modified by the store operation. Thus  $CF(s_1) \longrightarrow CF(s_2)$  by applying *SC-Store*.  $\Box$

One thing that is still missing from the definition of CF is that we have not shown that the function always maps legal HC terms to legal SC terms. The soundness of HC guarantees this, noting that CF maps the initial HC term to the initial SC term.

#### 5.4 Completeness of HC

We define function CL (cache-lift) that maps SC terms to corresponding HC terms. Suppose the memory hierarchy structure of the HC system is known. For any SC term s, CL(s) is defined by introducing empty caches in the memory hierarchy, setting the state for each outermost memory cell to  $(Ex,R(\epsilon))$ , and assigning memory identifiers for all memories.

It is easy to show that each SC rule can be simulated by a sequence of HC rules. For example, to simulate the SC-Load rule, we can apply Sh-Caching n times to propagate a shared copy to the corresponding L1 cache, then apply HC-Load to read the data from the L1 cache, and then apply Invalidate n times to purge the shared copies from the L1 cache and all caches between the L1 cache and the outermost memory. Here n is the L1 cache's depth, counting from the outermost memory whose depth is 0.

Lemma 9 (Completeness)  $s_1 \xrightarrow{\mathsf{SC}} s_2 \implies CL(s_1) \xrightarrow{\mathsf{HC}} CL(s_2).$

It is trivial to show that CF is the inverse function of CL.

**Lemma 10 (Connection)** For any SC term s, CF(CL(s)) = s.

This completes the proof that HC is a complete implementation of SC.

Theorem 11 The HC model completely implements the SC model.

# 6 Some Derived Rules of the HC Model

A derived rule is one that can be derived from other rules of the TRS. A derived rule can simply be an existing rule but with more stringent predicate, or a sequential combination of several other rules. Adding derived rules cannot affect the correctness of the system, but may improve the performance by some measure.

#### 6.1 Pushout

The pushout operation allows a memory to write the most up-to-date data of an exclusive cell back to the parent memory and invalidate the cell in one rewriting step, if the cell is not cached by any child (i.e., the cell's state is  $(\mathsf{Ex},\mathsf{R}(\epsilon))$ ).

```

Pushout Rule

```

```

Sys(\langle id, Cell(a,u,(Ex,W(id_k))) | m\rangle, Sys(\langle id_k, Cell(a,v,(Ex,R(\epsilon))) | m_k\rangle, eu_k) | sg)

```

$\longrightarrow \quad \mathsf{Sys}(\langle \mathsf{id}, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{R}(\epsilon))) \,|\, \mathsf{m}\rangle, \quad \mathsf{Sys}(\langle \mathsf{id}_k, \ \mathsf{m}_k\rangle, \ \mathsf{eu}_k) \,|\, \mathsf{sg})$

Obviously applying *Pushout* has the same effect as applying *Writeback* and *Invalidate* consecutively. We can define another model which is the same as HC except that the *Writeback* rule is replaced by the *Pushout* rule. In this new model, *Writeback* can be treated as a derived rule (*Pushout* followed by *Sh-Caching*). It can be shown that these two TRS's are equivalent.

### 6.2 Upgrade

The upgrade operation allows a memory to obtain the exclusive ownership for a shared cell in one rewriting step, if its parent has the exclusive ownership and has not given the data to any other child. Upgrade is also known as Dclaim.

Upgrade Rule

```

\begin{array}{lll} & Sys(\langle \mathsf{id}, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{R}(\mathsf{id}_k))) \,|\, \mathsf{m}\rangle, & Sys(\langle \mathsf{id}_k, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Sh},\mathsf{R}(\mathsf{dir}))) \,|\, \mathsf{m}_k\rangle, \, \mathsf{eu}_k) \,|\, \mathsf{sg}) \\ \rightarrow & Sys(\langle \mathsf{id}, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{W}(\mathsf{id}_k))) \,|\, \mathsf{m}\rangle, & Sys(\langle \mathsf{id}_k, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{R}(\mathsf{dir}))) \,|\, \mathsf{m}_k\rangle, \, \mathsf{eu}_k) \,|\, \mathsf{sg}) \end{array}

```

It can be shown that applying Upgrade has the same effect as applying Invalidate n+1 times, followed by Ex-Caching, followed by Sh-Caching n times, where n is the number of shared copies (of the same address) cached in the descendant memories  $(n \ge 0)$ . Here

the *Invalidate* rule is applied repeatedly to invalidate the shared copies in the descendant memories before the shared copy in the memory itself can be invalidated, and the *Sh-Caching* rule is applied repeatedly to propagate shared copies to those descendant memories in which shared copies have just been invalidated.

### 6.3 Forward

If the state of a cell in a memory is (Ex,R(dir)), then it can write the most up-to-date data back to its parent and forward a shared copy to some sibling memory. Similarly, if the state of a cell in a memory is  $(Ex,R(\epsilon))$ , then it can invalidate the cell and forward the exclusive copy to some sibling memory. Forward is also known as Intervention.

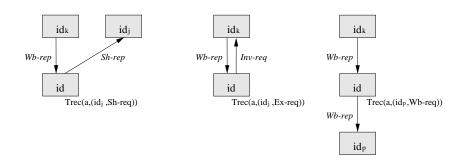

$\begin{array}{ll} Sh\mbox{-}Forward\ Rule & Sys(\langle id,\ Cell(a,u,(Ex,W(id_k))) \mid m\rangle, & Sys(\langle id_k,\ Cell(a,v,(Ex,R(dir))) \mid m_k\rangle,\ eu_k) \mid Sys(\langle id_j,\ m_j\rangle,\ eu_j) \mid sg) \\ \longrightarrow & Sys(\langle id,\ Cell(a,v,(Ex,R(id_k|id_j))) \mid m\rangle, & Sys(\langle id_k,\ Cell(a,v,(Sh,R(dir))) \mid m_k\rangle,\ eu_k) \mid Sys(\langle id_j,\ Cell(a,v,(Sh,R(\epsilon))) \mid m_j\rangle,\ eu_j) \mid sg) \\ & Ex\mbox{-}Forward\ Rule \end{array}$

$\begin{array}{rl} & Sys(\langle \mathsf{id}, \ \mathsf{Cell}(\mathsf{a},\mathsf{u},(\mathsf{Ex},\mathsf{W}(\mathsf{id}_k))) \,|\, \mathsf{m}\rangle, \\ & & Sys(\langle \mathsf{id}_k, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{R}(\epsilon))) \,|\, \mathsf{m}_k\rangle, \, \mathsf{eu}_k) \,\mid \mathsf{Sys}(\langle \mathsf{id}_j, \ \mathsf{m}_j\rangle, \, \mathsf{eu}_j) \,\mid \mathsf{sg}) \\ \rightarrow & Sys(\langle \mathsf{id}, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{W}(\mathsf{id}_j))) \,|\, \mathsf{m}\rangle, \\ & & Sys(\langle \mathsf{id}_k, \ \mathsf{m}_k\rangle, \, \mathsf{eu}_k) \,\mid \mathsf{Sys}(\langle \mathsf{id}_j, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{R}(\epsilon))) \,|\, \mathsf{m}_j\rangle, \, \mathsf{eu}_j) \,|\, \mathsf{sg}) \end{array}$

Obviously applying *Sh-Forward* has the same effect as applying *Writeback* followed by *Sh-Caching*, while applying *Ex-Forward* has the same effect as applying *Writeback* and *Invalidate* followed by *Ex-Caching*.

For exclusive forwarding, it is unnecessary to update the cell's value in the parent memory with the most up-to-date data. The cell's value cannot be used before it is overwritten later (maybe with the same value). Based on this, we can optimize *Ex-Forward* as follows:

$\begin{array}{c} \textit{Ex-Forward-Without-Writeback Rule} \\ & \mathsf{Sys}(\langle \mathsf{id}, \, \mathsf{Cell}(\mathsf{a},\mathsf{u},(\mathsf{Ex},\mathsf{W}(\mathsf{id}_k))) \, | \, \mathsf{m} \rangle, \\ & \mathsf{Sys}(\langle \mathsf{id}_k, \, \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{R}(\epsilon))) \, | \, \mathsf{m}_k \rangle, \, \mathsf{eu}_k) \, | \, \mathsf{Sys}(\langle \mathsf{id}_j, \, \mathsf{m}_j \rangle, \, \mathsf{eu}_j) \, | \, \mathsf{sg}) \\ \rightarrow & \mathsf{Sys}(\langle \mathsf{id}, \, \mathsf{Cell}(\mathsf{a},\mathsf{u},(\mathsf{Ex},\mathsf{W}(\mathsf{id}_j))) \, | \, \mathsf{m} \rangle, \\ & \mathsf{Sys}(\langle \mathsf{id}_k, \, \mathsf{m}_k \rangle, \, \mathsf{eu}_k) \, | \, \mathsf{Sys}(\langle \mathsf{id}_j, \, \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{R}(\epsilon))) \, | \, \mathsf{m}_j \rangle, \, \mathsf{eu}_j) \, | \, \mathsf{sg}) \end{array}$

It is worth noting that *Ex-Forward-Without-Writeback* is not a derived rule, since it allows terms that are illegal in HC. However, extending HC with this new rule cannot result in any illegal program behavior that violates Sequential Consistency. It can be proved that the extended system is still a complete implementation of SC.

# 7 The HCN Model: Refining HC with Message Passing

The HC model assumes that coherence actions involving two or more memory units can be performed with one rewriting step. For example, the *Ex-Caching* rule states that if a memory has a cell whose state is  $(Ex, R(\epsilon))$ , it can send an exclusive copy to some child and

Figure 6: Grammar of the HCN Model (Initially, all non-outermost memories, and all incoming and outgoing message queues are empty; the outermost memory contains a cell for each address and the state of each cell is  $(Ex, R(\epsilon))$ )

the child will receive the data and cache the cell in the  $(Ex,R(\epsilon))$  state. All this happens atomically with respect to other components of the system. Such rules are considered nonlocal in DSM systems where memory units communicate each other via message passing and the communication latency cannot be ignored. The caching and de-caching rules of HC are all non-local rules. Without special hardware support, it is expensive and difficult to ensure the atomicity of coherence actions such as a local read followed by a remote write.

In this section, we define the HCN model (HC with Network) by incorporating a message passing network to HC. The grammar of HCN is given in Figure 6. Each memory unit has two new components, an incoming message queue and an outgoing message queue. The queue constructors ' $\odot$ ' and ' $\otimes$ ' are associative and commutative, allowing non-FIFO message passing and non-blocking message processing. In HCN, each rewriting rule except message passing rules can examine and/or update only the local memory unit.

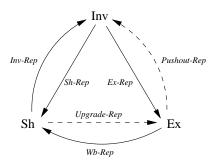

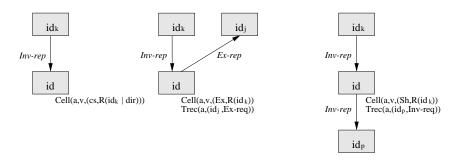

Figure 7: Relationship of Cache State Transitions and Reply Messages (Inv represents the state that the address is not cached; Pushout-rep and Upgrade-rep are potential optimizations)

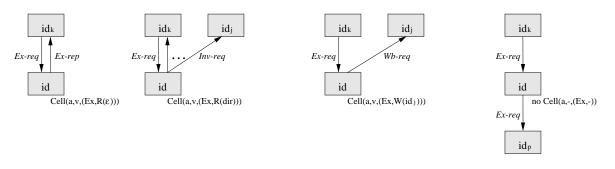

#### 7.1 Messages and Message Queues

In HCN, all protocol messages are imperative messages. A message has five fields: source, destination, command, address and data (which can be ' $\perp$ ' if the message carries no data). There are four types of message commands: Sh-rep, Ex-rep, Wb-rep and Inv-rep, where the suffix '-rep' stands for 'reply', because such messages are usually, although not necessarily, issued upon requests (this will become clear later when request messages are introduced). Figure 7 shows the cache state transition that can happen when a reply message is received and processed.

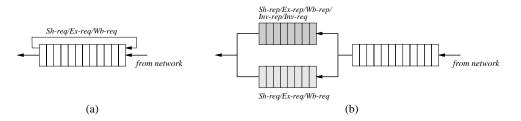

We use outgoing queues to characterize certain properties of the network. The constructor  $\otimes$  is associative and commutative, indicating any message in an outgoing queue to be brought to the front of the queue. This effectively models general non-FIFO networks which enforce no restriction on the order in which messages are delivered. With this associativity and commutativity, messages issued from the same source can arrive at their destinations in arbitrary order, even when the destination is also the same.

Ideally we would like to treat incoming queues as FIFOs and process incoming messages in the order in which they are received. However, this may cause deadlock or livelock unless messages that cannot be processed temporarily are properly buffered so that other messages can be processed first. To avoid this complication, we assume that the constructor ' $\odot$ ' is associative and commutative, thus incoming messages can be processed in arbitrary order since any message in an incoming queue can be brought to the front of the queue if necessary.

The adoption of associative and commutative queues for incoming messages allows us to treat buffer management as a separate issue that is transparent to imperative and directive rules. This simplifies the protocol design, because messages always appear to arrive in the order in which they are to be processed, and scenarios involving message reordering become irrelevant. Our experience shows that exposing buffer management at early design stages is inappropriate, since it could give rise to a bloated set of rewriting rules and dramatically complicate the protocol verification. Throughout the successive design process, buffer management should not be considered until all imperative and directive rules are defined; and its goal is purely to reorder incoming messages whenever necessary. We will revisit the buffer management issue in Section 13.

### 7.2 Rewriting Rules

The derivation of HCN rules from the HC rules is quite straightforward: each caching and de-caching rule in HC becomes a pair of rules for sending and receiving messages; and two message passing rules are introduced for passing messages between parent and child memories. The memory access rules remain unaffected (they are considered local rules because the processor and its L1 cache are tightly coupled and coherence actions involving the both appear to be atomic).

In HCN, a caching or de-caching operation is performed in three steps: the source site sends a message to its outgoing queue; the network transfers the message to the corresponding destination; and the destination site receives the message from its incoming queue.

**Memory Access Rules:** Memory access operations by a processor are performed on its L1 cache, and the message queues are not affected.

$\begin{array}{l} HCN-Load \ Rule \\ & \operatorname{Sys}(\langle \operatorname{id}, \operatorname{Cell}(a, v, (\operatorname{cs}, \mathsf{R}(\epsilon))) \mid \mathsf{m}, \operatorname{in}, \operatorname{out} \rangle, \operatorname{Proc}(\operatorname{ia}, \operatorname{rf}, \operatorname{prog})) \\ & if \ \operatorname{prog}[\operatorname{ia}] = \mathsf{r} := \operatorname{Load}(\mathsf{r}_1) \ and \ \mathsf{a} = \operatorname{rf}[\mathsf{r}_1] \\ \longrightarrow \ \operatorname{Sys}(\langle \operatorname{id}, \operatorname{Cell}(\mathsf{a}, v, (\operatorname{cs}, \mathsf{R}(\epsilon))) \mid \mathsf{m}, \operatorname{in}, \operatorname{out} \rangle, \operatorname{Proc}(\operatorname{ia}+1, \operatorname{rf}[\mathsf{r} := \mathsf{v}], \operatorname{prog})) \\ HCN-Store \ Rule \\ & \operatorname{Sys}(\langle \operatorname{id}, \operatorname{Cell}(\mathsf{a}, u, (\mathsf{Ex}, \mathsf{R}(\epsilon))) \mid \mathsf{m}, \operatorname{in}, \operatorname{out} \rangle, \operatorname{Proc}(\operatorname{ia}, \mathsf{rf}, \operatorname{prog})) \\ & if \ \operatorname{prog}[\operatorname{ia}] = \operatorname{Store}(\mathsf{r}_1, \mathsf{r}_2) \ and \ \mathsf{a} = \operatorname{rf}[\mathsf{r}_1] \\ \longrightarrow \ \operatorname{Sys}(\langle \operatorname{id}, \operatorname{Cell}(\mathsf{a}, v, (\mathsf{Ex}, \mathsf{R}(\epsilon))) \mid \mathsf{m}, \operatorname{in}, \operatorname{out} \rangle, \operatorname{Proc}(\operatorname{ia}+1, \operatorname{rf}, \operatorname{prog})) \ where \ \mathsf{v} = \operatorname{rf}[\mathsf{r}_2] \end{array}$

**Sh-Caching Rules:** If the state of a cell in memory id is (-,R(dir)), and the directory dir shows that the data is not cached in child  $id_k$ , then memory id can send a Sh-rep message to the child to give it a shared copy. When the Sh-rep message arrives, memory  $id_k$  caches the data in the  $(Sh,R(\epsilon))$  state.

**Ex-Caching Rules:** If the state of a cell in memory id is  $(Ex,R(\epsilon))$ , then it can send an Ex-rep message to child  $id_k$  to give it an exclusive copy. When the Ex-rep message arrives, memory  $id_k$  caches the data in the  $(Ex,R(\epsilon))$  state.

$\begin{array}{ll} Send-Ex-Rep \ Rule & \langle \mathsf{id}, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{R}(\epsilon))) \, | \, \mathsf{m}, \ \mathsf{in}, \ \mathsf{out} \rangle \\ - \to & \langle \mathsf{id}, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{W}(\mathsf{id}_k))) \, | \, \mathsf{m}, \ \mathsf{in}, \ \mathsf{out} \otimes \mathsf{Msg}(\mathsf{id},\mathsf{id}_k,\mathsf{Ex}\text{-}\mathsf{rep},\mathsf{a},\mathsf{v}) \rangle & where \quad \mathsf{id}_k \in \mathsf{children}(\mathsf{id}) \\ Receive-Ex-Rep \ Rule & & \langle \mathsf{id}_k, \ \mathsf{m}_k, \ \mathsf{Msg}(\mathsf{id},\mathsf{id}_k,\mathsf{Ex}\text{-}\mathsf{rep},\mathsf{a},\mathsf{v}) \odot \mathsf{in}_k, \ \mathsf{out}_k \rangle \\ - \to & & \langle \mathsf{id}_k, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{R}(\epsilon))) \, | \, \mathsf{m}_k, \ \mathsf{in}_k, \ \mathsf{out}_k \rangle \end{array}$

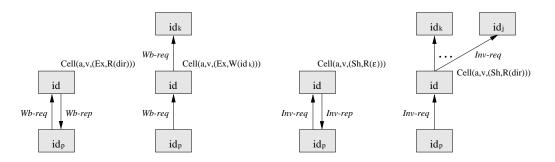

Writeback Rules: If the state of a cell in memory  $id_k$  is (Ex,R(dir)), then it can send a Wb-rep message to its parent id to write the most up-to-date data back to the home. When the Wb-rep message is received, memory id updates the cell's value and changes the cell's Hstate from  $W(id_k)$  to  $R(id_k)$ .

$\begin{array}{ll} Send-Wb-Rep \ Rule & \langle \mathsf{id}_k, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{R}(\mathsf{dir}))) \mid \mathsf{m}_k, \ \mathsf{in}_k, \ \mathsf{out}_k \rangle \\ \longrightarrow & \langle \mathsf{id}_k, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Sh},\mathsf{R}(\mathsf{dir}))) \mid \mathsf{m}_k, \ \mathsf{in}_k, \ \mathsf{out}_k \otimes \mathsf{Msg}(\mathsf{id}_k, \mathsf{id}, \mathsf{Wb}\text{-}\mathsf{rep}, \mathsf{a}, \mathsf{v}) \rangle & where \quad \mathsf{id} = \mathsf{parent}(\mathsf{id}_k) \\ Receive-Wb-Rep \ Rule & & \langle \mathsf{id}, \ \mathsf{Cell}(\mathsf{a},\mathsf{u},(\mathsf{Ex},\mathsf{W}(\mathsf{id}_k))) \mid \mathsf{m}, \ \mathsf{Msg}(\mathsf{id}_k, \mathsf{id}, \mathsf{Wb}\text{-}\mathsf{rep}, \mathsf{a}, \mathsf{v}) \odot \mathsf{in}, \ \mathsf{out} \rangle \\ \longrightarrow & \langle \mathsf{id}, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{R}(\mathsf{id}_k))) \mid \mathsf{m}, \ \mathsf{in}, \ \mathsf{out} \rangle \end{array}$

**Invalidate Rules:** If state of a cell in memory  $id_k$  is  $(Sh, R(\epsilon))$ , then it can purge the cell and send an lnv-rep message to its parent id to notify the home of the invalidation. When the lnv-rep message is received, memory id removes identifier  $id_k$  from the directory.

Message Passing Rules: Messages passing can happen only between the memories that have the parent-child relationship. The Message-Passing-To-Child rule transfers a message from the parent's outgoing queue to the child's incoming queue; while the Message-Passing-To-Parent rule transfers a message from the child's outgoing queue to the parent's incoming queue. Since the constructor ' $\otimes$ ' is associative and commutative, messages in an outgoing queue can be chosen to deliver in any order.

Message-Passing-To-Child Rule

$\begin{array}{rcl} & Sys(\langle id, m, in, Msg(id, id_k, cmd, a, v) \otimes out \rangle, & Sys(\langle id_k, m_k, in_k, out_k \rangle, eu_k) \mid sg) \\ \longrightarrow & Sys(\langle id, m, in, out \rangle, & Sys(\langle id_k, m_k, in_k \odot Msg(id, id_k, cmd, a, v), out_k \rangle, eu_k) \mid sg) \\ & Message-Passing-To-Parent Rule \\ & Sys(\langle id, m, in, out \rangle, & Sys(\langle id_k, m_k, in_k, Msg(id_k, id, cmd, a, v) \otimes out_k \rangle, eu_k) \mid sg) \\ \longrightarrow & Sys(\langle id, m, in \odot Msg(id_k, id, cmd, a, v), out \rangle, & Sys(\langle id_k, m_k, in_k, out_k \rangle, eu_k) \mid sg) \end{array}$

Still one scenario deserves a bit more discussion. Suppose a cell in  $(Ex,R(\epsilon))$  state performs a writeback operation followed by an invalidate operation. With non-FIFO message passing, the lnv-rep message may arrive at the parent before the Wb-rep message. If incoming messages were required to be processed in the FIFO order, deadlock could happen because the lnv-rep message cannot be processed before the Wb-rep message is processed. However, this will not occur, since messages in the incoming queue can be examined in any order, which allows the Wb-rep message to be processed first.

# 8 Verification of the HCN Model

It can be shown that the HCN model completely implements the HC model. The proof consists of three steps:

1. Soundness: Define queue-flush function QF (HCN  $\mapsto$  HC), and show

$s_1 \xrightarrow{\mathsf{HCN}} s_2 \implies QF(s_1) \xrightarrow{\mathsf{HC}} QF(s_2);$

2. Completeness: Define queue-lift function QL (HC  $\mapsto$  HCN), and show

$s_1 \xrightarrow{\mathsf{HC}} s_2 \implies QL(s_1) \xrightarrow{\mathsf{HCN}} QL(s_2);$

3. Connection: For any HC term s, show QF(QL(s)) = s.

The QF function is defined based on the intuition that, in HCN, when only message passing and message receive rules are applied, all message queues will eventually become empty. To show soundness, we prove that if  $s_1 \rightarrow s_2$  by applying some rule  $\alpha$  in HCN, then in HC, either  $QF(s_1) = QF(s_2)$  if  $\alpha$  is a message passing or message receive rule; or  $QF(s_1)$  $\rightarrow QF(s_2)$  by applying an appropriate HC rule if  $\alpha$  is a memory access or message send rule.

The queue-lift function QL maps HC terms to HCN terms by simply introducing empty incoming and outgoing queues for each memory unit. It is easy to show that each HC rule can be simulated by a sequence of HCN rules.

#### 8.1 Inclusion Invariants

As the Inclusion Invariants for the HC model, the HCN model maintains analogous invariants. However, the invariants are more complicated, because caching and de-caching operations involve two memory units that can communicate only via sending and receiving messages. In other words, a coherence action that is atomic in HC may have to be carried out in multiple steps in HCN. For example, if the directory shows that a shared copy has been cached by a child regarding some address, it means three possible cases: the child has the shared copy at the time; a Sh-rep message is on the way to the child (the child will receive the shared copy); or an Inv-rep message is on the way to the parent (the child has just invalidated the shared copy).

In our notation, we use ' $\cup$ ' to represent the operator that merges messages from two queues, and '-' the operator that deletes a message from a queue. The invariants fall into two categories: the situation when a cell is cached in a memory; and the situation when a message is in transient in the network. The meaning of the invariants is straightforward. For example, if a child has a shared cell, then either the parent has the address with the same value while the directory shows that the child has a shared copy; or there is a Wb-rep message on the way to the parent in which the Hstate indicates that an exclusive copy has been given to the child.

Lemma 12 (Inclusion Invariants) In any HCN term Sys( $\langle id, m, in, out \rangle$ , Sys( $\langle id_k, m_k, in_k, out_k \rangle$ ,  $eu_k$ ) | sg),

#### Sh-Inclusion

#### **Ex-Inclusion**

#### Sh-rep-Inclusion

$\begin{array}{rcl} \mathsf{Msg}(\mathsf{id},\mathsf{id}_k,\mathsf{Sh}\text{-}\mathsf{rep},\mathsf{a},\mathsf{v}) \ \in \ \mathsf{out} \ \cup \ \mathsf{in}_k & \Longrightarrow \\ & \mathsf{a} \ \notin \ \mathsf{m}_k \\ & \mathsf{Cell}(\mathsf{a},\mathsf{v},(\text{-},\mathsf{R}(\mathsf{id}_k|\text{-}))) \ \in \ \mathsf{m} \\ & \mathsf{Msg}(\mathsf{id},\mathsf{id}_k,\text{-},\mathsf{a},\text{-}) \ \notin \ \mathsf{out} \ \cup \ \mathsf{in}_k - \ \mathsf{Msg}(\mathsf{id},\mathsf{id}_k,\mathsf{Sh}\text{-}\mathsf{rep},\mathsf{a},\mathsf{v}) \\ & \mathsf{Msg}(\mathsf{id}_k,\mathsf{id}_k,\text{-},\mathsf{a},\text{-}) \ \notin \ \mathsf{out}_k \ \cup \ \mathsf{in} \end{array}$

#### **Ex-rep-Inclusion**

$\begin{array}{rcl} \mathsf{Msg}(\mathsf{id},\mathsf{id}_k,\mathsf{Ex}\text{-}\mathsf{rep},\mathsf{a},\mathsf{v}) \ \in \ \mathsf{out} \ \cup \ \mathsf{in}_k & \Longrightarrow \\ & \mathsf{a} \ \notin \ \mathsf{m}_k \\ & \mathsf{Cell}(\mathsf{a},\!\mathsf{v},\!(\mathsf{Ex},\!\mathsf{W}(\mathsf{id}_k))) \ \in \ \mathsf{m} \\ & \mathsf{Msg}(\mathsf{id},\mathsf{id}_k,\!-\!,\mathsf{a},\!-\!) \ \notin \ \mathsf{out} \ \cup \ \mathsf{in}_k \ - \ \mathsf{Msg}(\mathsf{id},\mathsf{id}_k,\mathsf{Ex}\text{-}\mathsf{rep},\mathsf{a},\mathsf{v}) \\ & \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\!-\!,\mathsf{a},\!-\!) \ \notin \ \mathsf{out}_k \ - \ \mathsf{in} \end{array}$

#### Wb-rep-Inclusion

$\begin{array}{ll} \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\mathsf{Wb}\text{-rep},\mathsf{a},\mathsf{v}) \in \mathsf{out} \cup \mathsf{in}_k \implies \\ & \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Sh},\mathsf{R}(\text{-}))) \in \mathsf{m}_k \\ & \mathsf{Cell}(\mathsf{a},\text{-},(\mathsf{Ex},\mathsf{W}(\mathsf{id}_k))) \in \mathsf{m} \\ & \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\text{-},\mathsf{a},\text{-}) \notin \mathsf{out} \cup \mathsf{in}_k \\ & \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\text{-},\mathsf{a},\text{-}) \notin \mathsf{out}_k \cup \mathsf{in} - \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\mathsf{Wb}\text{-rep},\mathsf{a},\mathsf{v}) \\ \\ or \\ & \mathsf{a} \notin \mathsf{m}_k \\ & \mathsf{Cell}(\mathsf{a},\text{-},(\mathsf{Ex},\mathsf{W}(\mathsf{id}_k))) \in \mathsf{m} \\ & \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\mathsf{Inv}\text{-rep},\mathsf{a},\bot) \in \mathsf{out}_k \cup \mathsf{in} \\ & \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\mathsf{Inv}\text{-rep},\mathsf{a},\bot) \in \mathsf{out}_k \cup \mathsf{in} \\ & \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\mathsf{-},\mathsf{a},\text{-}) \notin \mathsf{out} \cup \mathsf{in}_k \\ & \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\text{-},\mathsf{a},\text{-}) \notin \mathsf{out}_k \cup \mathsf{in} - \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\mathsf{Wb}\text{-rep},\mathsf{a},\mathsf{v}) - \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\mathsf{Inv}\text{-rep},\mathsf{a},\bot) \\ \end{array}$

#### Inv-rep-Inclusion

```

\begin{array}{lll} \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\mathsf{Inv}\text{-rep},\mathsf{a},\bot) \in \mathsf{out} \cup \mathsf{in}_k \implies \\ \mathsf{a} \notin \mathsf{m}_k & \\ \mathsf{Cell}(\mathsf{a},\!-\!(\mathsf{-},\!\mathsf{R}(\mathsf{id}_k|\!-\!))) \in \mathsf{m} & \\ \mathsf{Msg}(\mathsf{id},\mathsf{id}_k,\!-\!,\mathsf{a},\!-\!) \notin \mathsf{out} \cup \mathsf{in}_k & \\ \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\!-\!,\mathsf{a},\!-\!) \notin \mathsf{out}_k \cup \mathsf{in} - \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\mathsf{Inv}\text{-rep},\mathsf{a},\bot) \\ or & \\ \mathsf{a} \notin \mathsf{m}_k & \\ \mathsf{Cell}(\mathsf{a},\!-\!(\mathsf{Ex},\!\mathsf{W}(\mathsf{id}_k))) \in \mathsf{m} & \\ \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\mathsf{Wb}\text{-rep},\mathsf{a},\mathsf{v}) \in \mathsf{out}_k \cup \mathsf{in} & \\ \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\mathsf{Wb}\text{-rep},\mathsf{a},\mathsf{v}) \in \mathsf{out}_k \cup \mathsf{in} & \\ \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\!-\!,\mathsf{a},\!-\!) \notin \mathsf{out} \cup \mathsf{in}_k & \\ \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\!-\!,\mathsf{a},\!-\!) \notin \mathsf{out}_k \cup \mathsf{in} - \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\mathsf{Wb}\text{-rep},\mathsf{a},\mathsf{v}) - \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\mathsf{Inv}\text{-rep},\mathsf{a},\bot) \end{array}

```

**Proof** The proof is by induction on rewriting steps. The invariants hold trivially for the initial terms where all caches and queues are empty. It can be shown by checking each rewriting rule that, if the invariants hold for a term, then they still hold after the term is rewritten according to that rule.  $\Box$

Based on the Inclusion Invariants, we can show that no memory can contain two cells that have the same address. This is because only the *Receive-Sh-Rep* and *Receive-Ex-Rep* rules can create new cells; when a Sh-rep or Ex-rep is received, the memory cannot have a cell regarding the same address.

## 8.2 Queue Flushing Property

Suppose we define a new rewriting system  $\mathsf{R}_{\mathsf{QF}},$  which has the same grammar as  $\mathsf{HCN}$  but uses only a subset of the  $\mathsf{HCN}$  rules.

### Definition 13 (TRS for queue flushing)

```

R<sub>QF</sub> = { Message-Passing-To-Child, Message-Passing-To-Parent,

Receive-Sh-Rep, Receive-Ex-Rep, Receive-Wb-Rep, Receive-Inv-Rep }

```

Now we discuss some properties of the  $\mathsf{R}_{\mathsf{QF}}$  system.

**Lemma 14**  $R_{QF}$  is strongly terminating and confluent, i.e., for any HCN term, rewriting with respect to  $R_{QF}$  terminates within a finite number of steps and always reaches the same normal form, regardless of the order in which the rules are applied.

**Proof** The termination is obvious because  $R_{QF}$  includes only the message passing and message receive rules. The message passing rules move messages from sources to destinations, while the message receive rules process messages extracted from incoming queues. However, none of these rules can generate new messages. The confluence follows from the fact that message passing and message receive rules do not interfere each other.  $\Box$

In fact  $\mathsf{R}_{\mathsf{QF}}$  rules not only do not interfere each other, but also do not interfere with non- $\mathsf{R}_{\mathsf{QF}}$  rules. This can be trivially verified by checking each pair of  $\mathsf{R}_{\mathsf{QF}}$  / non- $\mathsf{R}_{\mathsf{QF}}$  rules.

**Lemma 15**  $R_{QF}$  rules do not interfere with non- $R_{QF}$  rules, i.e., if  $s_1 \longrightarrow s_2$  by applying rule  $\alpha \notin R_{QF}$ , and  $s_1 \longrightarrow s_3$  by applying rule  $\beta \in R_{QF}$ , then there exists  $s_4$  such that  $s_2 \longrightarrow s_4$  by applying  $\beta$  and  $s_3 \longrightarrow s_4$  by applying  $\alpha$ .

**Definition 16** For any HCN term s,  $NF_{QF}(s)$  is the normal form of s in  $R_{QF}$ .

Lemma 17 (Queue Flushing Property) For any HCN term s, all incoming and outgoing message queues are empty in  $NF_{QF}(s)$ .

**Proof** Suppose not all message queues are empty. If an outgoing queue is not empty, some message passing rule would apply; if an incoming queue is not empty, according to the Inclusion Invariants, some message receive rule would apply. Thus the term cannot be a normal form.  $\Box$

#### 8.3 Soundness of HCN

We define function QF (queue-flush) that maps HCN terms to HC terms as follows:

**Definition 18 (Queue-flush function)** For any HCN term s, QF(s) is the projection of  $NF_{QF}(s)$  on the corresponding HC term where all the message queues have been deleted.

The queue-flush function builds a relationship between HCN terms and HC terms. Based on this mapping function, HC can simulate HCN in the following sense: if HCN applies a message passing or message receive rule, then HC applies no rule (no action is taken); if HCN applies a memory access or message send rule, then HC applies an appropriate rule defined as follows.

| the $HCN$ rule | the corresponding $HC$ rule |

|----------------|-----------------------------|

| HCN-Load       | HC-Load                     |

| HCN-Store      | HC-Store                    |

| Send-Sh-Rep    | Sh-Caching                  |

| Send-Ex-Rep    | Ex-Caching                  |

| Send-Wb-Rep    | Writeback                   |

| Send-Inv-Rep   | Invalidate                  |

Lemma 19 (Soundness)  $s_1 \xrightarrow{\text{HCN}} s_2 \implies QF(s_1) \xrightarrow{\text{HC}} QF(s_2).$

**Proof** We give the proof for one rewriting step; proof for multiple steps follows from induction. Assume  $s_1 \longrightarrow s_2$  by applying some rule  $\alpha$  in HCN. The proof is based on the case analysis on  $\alpha$ :

- $\alpha \in \mathsf{R}_{\mathsf{QF}}$ . Needless to say  $QF(s_1) = QF(s_2)$ .

- $\alpha$  is a memory access rule. Since  $\alpha$  cannot interfere with any  $R_{QF}$  rule and applying  $\alpha$  cannot generate any new message, it can be shown by induction that  $NF_{QF}(s_1) \rightarrow NF_{QF}(s_2)$  by applying  $\alpha$ . Notice all message queues are empty in  $NF_{QF}(s_1)$  and  $NF_{QF}(s_2)$ , thus  $QF(NF_{QF}(s_1)) \rightarrow QF(NF_{QF}(s_2))$  by applying the corresponding memory access rule. Hence  $QF(s_1) \rightarrow QF(s_2)$ . See Figure 8 (a).

Figure 8: Simulate HCN in HC

•  $\alpha$  is a message send rule. Since  $\alpha$  cannot interfere with any  $\mathsf{R}_{\mathsf{QF}}$  rules, it can be shown by induction that there exists  $s_n$  such that  $NF_{QF}(s_1) \longrightarrow s_n$  by applying  $\alpha$ , and  $s_2 \longrightarrow s_n$  by applying  $\mathsf{R}_{\mathsf{QF}}$  rules. Since applying  $\alpha$  generates a new message,  $s_n \longrightarrow NF_{QF}(s_2)$  by applying a message passing rule followed by a message receive rule. Notice all message queues are empty in  $NF_{QF}(s_1)$  and  $NF_{QF}(s_2)$ , thus  $QF(NF_{QF}(s_1)) \longrightarrow QF(NF_{QF}(s_2))$  by applying the corresponding caching or de-caching rule. Hence  $QF(s_1) \longrightarrow QF(s_2)$ . See Figure 8 (b).  $\Box$

### 8.4 Completeness of HCN

We define function QL (queue-lift) that maps HC terms to corresponding HCN terms. For any HC term s, QL(s) is defined by adding empty incoming and outgoing message queues in each memory unit. Based on this mapping function, it is easy to show that each HC rule can be simulated by a sequence of HCN rules. For example, to simulate the *Sh-Caching* rule, we can apply *Send-Sh-Rep*, followed by *Message-Passing-To-Child*, and followed by *Receive-Sh-Rep*. The table below gives the sequence of HCN rules for each HC rule.

| the $HC$ rule | the sequence of HCN rules to simulate the HC rule          |

|---------------|------------------------------------------------------------|

| HC-Load       | HCN-Load                                                   |

| HC-Store      | HCN-Store                                                  |

| Sh-Caching    | Send-Sh-Rep + Message-Passing-To-Child + Receive-Sh-Rep    |

| Ex-Caching    | Send-Ex-Rep + Message-Passing-To-Child + Receive-Ex-Rep    |

| Writeback     | Send-Wb-Rep + Message-Passing-To-Parent + Receive-Wb-Rep   |

| Invalidate    | Send-Inv-Rep + Message-Passing-To-Parent + Receive-Inv-Rep |

Lemma 20 (Completeness)  $s_1 \xrightarrow{\mathsf{HC}} s_2 \implies QL(s_1) \xrightarrow{\mathsf{HCN}} QL(s_2).$

It is trivial to show that QF is the inverse function of QL.

**Lemma 21 (Connection)** For any HC term s, QF(QL(s)) = s.

This completes the proof that HCN is a complete implementation of HC.

Theorem 22 The HCN model completely implements the HC model.

# 9 Some Optimizations of the HCN Model

A memory model can be implemented with different protocols. In designing cache coherence protocols, the designer often faces various design options. While soundness and liveness should always be guaranteed, different protocols can result in different performance, complexity and implementation cost. In this section, we discuss some optimization techniques for the HCN model. Although the optimization rules cannot be derived from the existing HCN rules, they can be employed safely to optimize certain common scenarios. We can extend HCN with one or more such optimizations while ensuring that the extended model remains a complete implementation of HC. All the optimization rules are imperative rules.

### 9.1 Pushout

In HCN, when an exclusive cell is pushed out, the memory sends two messages to its parent, a Wb-rep followed by an Inv-rep. The pushout optimization uses just one message, Pushout-rep, to notify the parent of the pushout operation. The Pushout-rep message can be considered as a combination of the Wb-rep and Inv-rep, and can be used to reduce the number of messages. It can also simplify the protocol design, noting in HCN the Inv-rep can arrive before the Wb-rep with non-FIFO message passing.

```

\begin{array}{ll} & Send-Pushout-Rep \ Rule & & & \langle \mathsf{id}_k, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{R}(\epsilon))) \mid \mathsf{m}_k, \ \mathsf{in}_k, \ \mathsf{out}_k \rangle \\ & \longrightarrow & & \langle \mathsf{id}_k, \ \mathsf{m}_k, \ \mathsf{in}_k, \ \mathsf{out}_k \otimes \mathsf{Msg}(\mathsf{id}_k, \mathsf{id}, \mathsf{Pushout}\text{-}\mathsf{rep}, \mathsf{a}, \mathsf{v}) \rangle \quad \textit{where} \quad \mathsf{id} = \mathsf{parent}(\mathsf{id}_k) \\ & Receive-Pushout\text{-}Rep \ Rule & & & \\ & & & \langle \mathsf{id}, \ \mathsf{Cell}(\mathsf{a},\mathsf{u},(\mathsf{Ex},\mathsf{W}(\mathsf{id}_k))) \mid \mathsf{m}, \ \mathsf{Msg}(\mathsf{id}_k, \mathsf{id}, \mathsf{Pushout}\text{-}\mathsf{rep}, \mathsf{a}, \mathsf{v}) \odot \mathsf{in}, \ \mathsf{out} \rangle \\ & \longrightarrow & & & \langle \mathsf{id}, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{R}(\epsilon))) \mid \mathsf{m}, \ \mathsf{in}, \ \mathsf{out} \rangle \end{array}

```

We can extend the HCN model with the pushout rules. It is trivial to show that the extended system is a complete implementation of HCN (the projection function replaces each Pushout-rep message with a Wb-rep followed by an Inv-rep).

### 9.2 Upgrade

The motivation of the upgrade optimization is to allow a shared copy to be upgraded with the exclusive ownership without being invalidated first. If the state of a cell in memory id is  $(Ex,R(id_k))$ , then memory id can send an Upgrade-rep message to child  $id_k$ ; when the Upgrade-rep message is received, memory  $id_k$  changes the cell's Cstate from Sh to Ex.

Send-Upgrade-Rep Rule  $\langle id, Cell(a,v,(Ex,R(id_k))) | m, in, out \rangle$  $\longrightarrow \langle id, Cell(a,v,(Ex,W(id_k))) | m, in, out \otimes Msg(id, id_k, Upgrade-rep, a, <math>\perp ) \rangle$  Receive-Upgrade-Rep Rule

$\langle id_k, Cell(a,v,(Sh,R(dir))) | m_k, Msg(id, id_k, Upgrade-rep, a, \bot) \odot in_k, out_k \rangle \rightarrow \langle id_k, Cell(a,v,(Ex,R(dir))) | m_k, in_k, out_k \rangle$

Consider the scenario in which the shared copy in the child has just been invalidated when the Upgrade-rep message arrives (an Inv-rep message is on its way to the parent). Deadlock can happen because the Upgrade-rep and Inv-rep messages cannot be processed (in order for one message to be processed, the other has to be processed first). To We can rely on directive rules to deal with the dilemma, noting that deadlock in an imperative model does not necessarily mean deadlock in the final protocol. For example, the deadlock cannot happen if we can somehow ensure that the shared copy in the child cannot be invalidated in this case. This can be achieved by using directive messages to properly coordinate the parent and child memories.

Relying on directive rules to avoid such deadlock can put unnecessary constraints on how directive messages must be used, and performance can also be sacrificed. A better solution is to provide proper rules so that the protocol can recover from a potential deadlock situation by cancelling certain operation effects. For example, we can use a negative acknowledgment to notify the parent or the child that the Upgrade-rep or Inv-rep message cannot be processed. This technique can be adopted to eliminate deadlocks for many similar scenarios throughout the protocol design.

Using Upgrade-neg-rep: When the Upgrade-rep message arrives, if the child does not have the shared copy, there are two possible cases: either the shared copy has been invalidated (an Inv-rep is on the way to the parent), or the shared copy has not been received yet (a Sh-rep is on the way to the child). Notice that the child cannot decide which case is true based on its local information. To prevent deadlock, the child can discard the Upgrade-rep message and send an Upgrade-neg-rep message to the parent to report the failure of the upgrade operation. When the Upgrade-neg-rep is received, the parent sets the cell's Hstate to Sh (the cell's value is still valid).

$\begin{array}{ll} Receive-Upgrade-Rep-And-Send-Upgrade-Neg-Rep\ Rule\\ & \langle \mathsf{id}_k,\ \mathsf{m}_k,\ \mathsf{Msg}(\mathsf{id},\mathsf{id}_k,\mathsf{Upgrade-rep},\mathsf{a},\mathsf{v})\odot\mathsf{in}_k,\ \mathsf{out}_k\rangle \quad \textit{if} \ \mathsf{a}\notin\mathsf{m}_k\\ \longrightarrow & \langle \mathsf{id}_k,\ \mathsf{m}_k,\ \mathsf{in}_k,\ \mathsf{out}\otimes\mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\mathsf{Upgrade-neg-rep},\mathsf{a},\bot)\rangle\\ Receive-Upgrade-Neg-Rep\ Rule\\ & \langle \mathsf{id},\ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{W}(\mathsf{id}_k)))\,|\,\mathsf{m},\ \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\mathsf{Upgrade-neg-rep},\mathsf{a},\bot)\odot\mathsf{in},\ \mathsf{out}\rangle\\ \longrightarrow & \langle \mathsf{id},\ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{R}(\mathsf{id}_k)))\,|\,\mathsf{m},\ \mathsf{n},\ \mathsf{out}\rangle\end{array}$

Using lnv-neg-rep: Instead of using the Upgrade-rep message, we can have the parent send an lnv-neg-rep message to the child to negatively acknowledge the invalidate operation while letting the Upgrade-rep message wait at the child. Notice that the lnv-neg-rep message carries the data read from the cell in the parent. When the lnv-neg-rep is received, the child caches the data in the  $(Sh, R(\epsilon))$  as if the invalidate operation were never performed.

Receive-Inv-Rep-And-Send-Inv-Neg-Rep Rule

$\langle \mathsf{id}, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{W}(\mathsf{id}_k))) \,|\, \mathsf{m}, \ \mathsf{Msg}(\mathsf{id}_k,\mathsf{id},\mathsf{Inv}\text{-}\mathsf{rep},\mathsf{a},\bot) \odot \mathsf{in}, \ \mathsf{out} \rangle$

$\rightarrow \quad \langle \mathsf{id}, \ \mathsf{Cell}(\mathsf{a},\mathsf{v},(\mathsf{Ex},\mathsf{W}(\mathsf{id}_k))) \,|\, \mathsf{m}, \ \mathsf{in}, \ \mathsf{out} \otimes \mathsf{Msg}(\mathsf{id},\mathsf{id}_k,\mathsf{Inv-neg-rep},\mathsf{a},\mathsf{v}) \rangle$

$\begin{array}{ll} \textit{Receive-Inv-Neg-Rep Rule} \\ & \langle \mathsf{id}_k, \, \mathsf{m}_k, \, \mathsf{Msg}(\mathsf{id}, \mathsf{id}_k, \, \mathsf{Inv-neg-rep}, \mathsf{a}, \mathsf{v}) \odot \mathsf{in}_k, \, \mathsf{out}_k \rangle \\ \longrightarrow & \langle \mathsf{id}_k, \, \mathsf{Cell}(\mathsf{a}, \mathsf{v}, (\mathsf{Sh}, \mathsf{R}(\epsilon))) \, | \, \mathsf{m}_k, \, \mathsf{in}_k, \, \mathsf{out}_k \rangle \end{array}$

**Discussion:** The rewriting rules of an imperative model can be classified as two categories, the *memory access rules* that perform memory access operations such as load and store, and the *coherence maintenance rules* that move coherence information such as data and ownership in the memory hierarchy. Intrinsically the imperative model is not confluent due to potential data access races. However, we can always make the coherence maintenance rules confluent by introducing extra rules if necessary to undo improper operations. The confluence of the coherence maintenance rules eliminates deadlock in the imperative model, thereby providing more flexibility for the directive design phase.

### 9.3 Forward

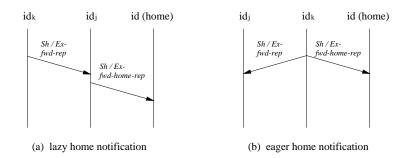

The forward optimization accelerates the processing when a memory wants to have a shared or exclusive copy while the most up-to-date data resides in some sibling memory. It allows the memory that exclusively owns the data to send a copy to a sibling memory directly. If a memory has a cell in the  $(Ex,R(\epsilon))$  state, it can send a Sh-fwd-rep message to a sibling memory to give it a shared copy; if a memory has a cell in the  $(Ex,R(\epsilon))$  state, it can send a Sh-fwd-rep message to a sibling an Ex-fwd-rep message to a sibling memory to give it an exclusive copy.