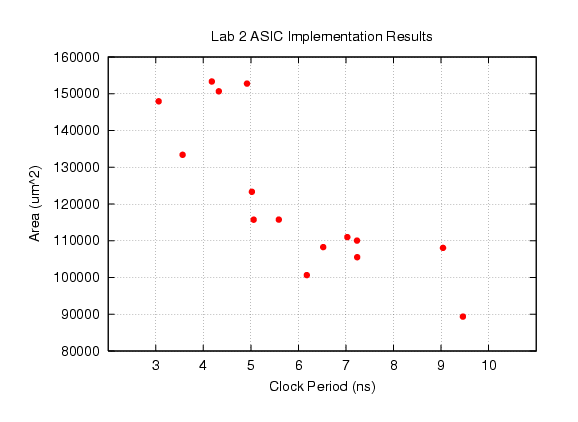

The following plot shows the area and clock period for each student's optimized two-stage SMIPS processor. Students either optimized for area, performance, or both using a variety of techniques including modifying the micro-architecture, changing options in the synthesis or place+route tools, and utilizing Synopsys DesignWare components.